Новини світу мікро- та наноелектроніки

Adaptable pullup

It’s common for I2C systems to have both standard and fast devices on the same bus.

For I2C systems, the speed and power consumption both depend on the values of pullup resistors: the values of them should be low enough to secure the fast charge of the bus capacitance.

Wow the engineering world with your unique design: Design Ideas Submission Guide

But the low values increase power consumption, the low values can also present too heavy a load for the transmitter.

The variable topology of the bus can make the situation somewhat more complicated.

Hence when your system is power-restricted and you need to use several I2C chips at different I2C modes, you have to compromise between these chips. Or you can use the adaptable pullup, which is shown in Figure 1.

Figure 1: The adaptable pullup where a closed transistor connects additional resistors R5 and R6 in parallel to the main pullup resistors R1 and R2

Figure 1: The adaptable pullup where a closed transistor connects additional resistors R5 and R6 in parallel to the main pullup resistors R1 and R2

The circuit is rather simple: a closed transistor connects additional resistors R5 and R6 in parallel to the main pullup resistors R1 and R2.

The connection can be controlled by GPIO for example, as shown in Figure1, and should be done before the fast data exchange takes place.

Another solution is shown in Figure 2, which represents one-half of the whole circuit (the second half for SDA is omitted for brevity). The circuit uses an analog switch (for instance, TS5A3159 of TI) to disconnect the “fast” part of the bus. While it’s disconnected, the resistor R5 provides a high (idle) voltage level on the bus. Note that the capacitance of the switch, which can be large enough (20 to 100pF), should be taken into account.

Figure 2: Alternative adaptable pullup solution that uses an analog switch to disconnect the “fast” part of the bus.

—Peter Demchenko studied math at the University of Vilnius and has worked in software development.

Related Content

- Active pullup/pulldown network saves watts

- Pull-up Resistors

- A self-testing GPIO

- Logic Probe has a wide voltage range

The post Adaptable pullup appeared first on EDN.

Vishay Intertechnology Industrial-Grade TRANSZORB and Automotive Grade PAR TVS Deliver Peak Pulse Power of 600 W in DFN3820A Package

Featuring Compact 3.8 mm by 2.0 mm Footprint, Low 0.88 mm Profile, and Wettable Flanks, Space-Saving Devices Offer Operating Temperatures to +185 °C

Vishay Intertechnology, Inc. today introduced four new series of surface-mount industrial-grade TRANSZORB and automotive-grade PAR transient voltage suppressors (TVS) in the low profile DFN3820A package with wettable flanks. Providing space-saving solutions for automotive, computer, consumer, and industrial applications, the 6DFNxxA, 6DFNxxxCA, T6NxxA, and T6NxxxCA offer peak pulse power of 600 W at 10/1000 μs and low leakage current down to 1 μA.

The first package in Vishay’s new Power DFN family, the DFN3820A features a compact 3.8 mm by 2.0 mm footprint and an extremely low typical height of 0.88 mm, allowing the Vishay General Semiconductor TVS to make more efficient use of PCB space. Footprint-compatible with the SMP (DO-220AA) package, the DFN3820A is 85 % smaller than the SMB (DO-214AA) and 42 % smaller than the SlimSMAW (DO-221AD), but it keeps peak pulse power dissipation with a 10/1000 μs waveform at 600 W.

The devices released are designed to protect sensitive electronic equipment against voltage transients induced by inductive load switching and lightning. The 6DFNxxA and 6DFNxxxCA TRANSZORB TVS will be used for signal line protection in server power modules, digital media controllers, and AV signal extenders for computer and consumer applications, in addition to industrial robot control boards, process/flow control instruments, and automation systems.

AEC-Q101 qualified and offering high-temperature operation to +185 °C, the T6NxxA and T6NxxxCA PAR TVS are intended for automotive load dump protection. Typical applications will include advanced driver assistance (ADAS), battery management (BMS), electric power steering (EPS), and infotainment systems; central control units; on-board chargers (OBC); DC/DC converters and traction inverters; and electrical motor drives.

The TVS offer excellent clamping capability with a maximum clamping voltage from 16.7 V to 70.1 V for the 6DFNxxA and T6NxxA, and 16.7 V to 137 V for the 6DFNxxxCA and T6NxxxCA. The wettable flanks of their DFN3820A package allow for automatic optical inspection (AOI), eliminating the need for an X-ray inspection. Ideal for automated placement, the rectifiers offer an MSL moisture sensitivity level of 1, per J-STD-020, LF maximum peak of 260 °C. The devices are RoHS-compliant and halogen-free, and their matte tin-plated leads meet the JESD 201 class 2 whisker test.

Device Specification Table:

| Series |

6DFNxxA |

6DFNxxxCA |

T6NxxA |

T6NxxxCA |

| Automotive Grade |

No |

No |

Yes |

Yes |

| VBR (V) |

12 to 51 |

12 to 100 |

12 to 51 |

12 to 100 |

| VWM (V) |

10.2 to 43.6 |

10.2 to 85.5 |

10.2 to 43.6 |

10.2 to 85.5 |

| Max. reverse leakage at VWM (mA) |

1.0 to 2.0 |

|||

| PPPM (10/1000 μs) (W) |

600 |

|||

| Max. clamping voltage (V) |

16.7 to 70.1 |

16.7 to 137 |

16.7 to 70.1 |

16.7 to 137 |

| TJ max. (°C) |

175 |

175 |

185 |

185 |

| Polarity |

Unidirectional |

Bidirectional |

Unidirectional |

Bidirectional |

| Package |

DFN3820A |

|||

| Circuit configuration |

Single |

|||

The post Vishay Intertechnology Industrial-Grade TRANSZORB and Automotive Grade PAR TVS Deliver Peak Pulse Power of 600 W in DFN3820A Package appeared first on ELE Times.

Ceremorphic Driving Vision to Develop Sustainable Product Portfolio Across Sectors

Ceremorphic is doing great business and quality development in the areas of supercomputing, datacentre, life sciences, automotive, robotics, and metaverse processing. As the world moves towards a highly advanced computing era, Ceremorphic is leading many channels in developing high-tech computing and engineering systems. Their technical excellence covers a vast portfolio including multi-thread processors, security processing, machine learning processors, analog computing, reliable circuits, 3D interconnects, graph neural processing, programmable logic, and low-power memory.

Dr. Venkat Mattela, Founder & CEO, of Ceremorphic

Dr. Venkat Mattela, Founder & CEO, of Ceremorphic

Rashi Bajpai, Sub-Editor at ELE Times interacted with Dr. Venkat Mattela, Founder & CEO, of Ceremorphic about the company’s vision and technical competence, and also touched upon topics of Make in India and ESG norms.

This is an excerpt from the conversation.

ELE Times: Please throw some light on Ceremorphic’s recent development of the ultra-low power supercomputer chip built in TSMC 5nm.

Venkat Mattela: Designing products with optimal energy consumption is a challenge we foresee for the semiconductor industry for the next few decades especially with the advent of carbon neutrality mandates. As supercomputing innovations burgeon and data centers consume ever more energy, within a decade they will consume a significant part of the total energy generation in the world. This was the catalyst behind our mission to design chips with ultra-low energy consumption. Our breakthrough innovation is not just in advanced nodes like 5nm and 3nm, but we are also broadening our reach to other paradigms to minimize task workloads alongside semiconductor technology optimizations. Having taped out our 5nm chip in October 2022 and validated key technologies for our upcoming 3nm device, we’re proud of how far we’ve come in addressing these challenges. Equipped with advanced features like multi-thread processing and custom connectivity interfaces, our chips cater to modern applications’ rigorous demands, from AI model training to drug discovery. We’re excited to continue pushing the boundaries of technology and remain committed to creating solutions that make a meaningful impact.

ELE Times: In the latest development under the “Make in India” policy, India is set to begin manufacturing equipment for semiconductor manufacturing. In this regard, what in your view, are India’s major contributions to the semiconductor industry besides cutting-edge R&D? Also help us understand the challenges with physical manufacturing.

Venkat Mattela: In addition to cutting-edge R&D, India’s contributions to the semiconductor industry extend across various domains, showcasing the nation’s growing significance in this field. Firstly, India serves as a hub for semiconductor design and engineering services, with numerous companies specializing in chip design, verification, and testing. These capabilities play a crucial role in the global semiconductor supply chain, contributing to the development of innovative semiconductor products.

We also boast a robust ecosystem for semiconductor software development, encompassing tools and platforms for chip design, simulation, and optimization. This is complemented by our vast pool of skilled engineers and technologists that form a rich talent pool sought after by semiconductor companies worldwide. Moreover, initiatives like the Skill India program aim to enhance the employability of Indian youth in high-growth sectors such as semiconductors, fostering a skilled workforce for the industry’s future needs.

However, despite these contributions, India faces several challenges in physical manufacturing. One key challenge is the need for robust infrastructure and logistical support. Semiconductor fabrication facilities require state-of-the-art equipment, cleanroom environments, and reliable power and water supply, which may be lacking in certain regions.

Additionally, establishing a consistent supply chain for raw materials, chemicals, and equipment components is crucial to reduce reliance on imported materials and prevent disruptions. To scale up manufacturing, it is crucial to present ourselves as an ideal candidate for manufacturing thereby attracting investments in research, infrastructure, and workforce development.

While initiatives like the “Make in India” policy aim to do this, sustained efforts are needed to overcome regulatory barriers, attract foreign investment, and push for innovation-driven growth in the sector.

ELE Times: What potential collaborations can be explored between the renewable energy sector and semiconductor fabrication plants to establish ESG norms and sustainable practices in manufacturing?

Venkat Mattela: Renewable energy should not be viewed as merely an option, but rather as a standard practice across all industries. Given the semiconductor industry’s substantial energy consumption, it is crucial for us to take the lead in adopting renewable energy sources. Collaborations between the renewable energy sector and semiconductor fabrication plants play a pivotal role in establishing robust ESG norms and sustainable manufacturing practices.

By integrating renewable energy sources such as solar, wind, and hydroelectric power into semiconductor fabrication plants we can significantly reduce carbon emissions and environmental impact. Research and development efforts aimed at enhancing energy efficiency in semiconductor fabrication, such as advanced cooling systems, energy-efficient equipment, and optimized manufacturing processes, can yield significant environmental benefits while also improving operational efficiency and cost-effectiveness. Additionally, encouraging partnerships between renewable energy providers and semiconductor companies can facilitate the development of innovative solutions for energy storage and management. Technologies like battery storage systems and smart grid integration enable semiconductor facilities to store excess renewable energy and optimize its usage based on demand, thereby maximizing energy efficiency and grid stability. By leveraging renewable energy sources, emphasizing innovation, and promoting sustainability across the supply chain, we can contribute to a more environmentally conscious and socially responsible semiconductor industry.

ELE Times: What would be your insights and recommendations for the policymakers navigating the challenges of establishing India as a semiconductor hub?

Venkat Mattela: We are making significant strides in positioning India as a global R&D hub, thanks to our supportive policies and initiatives that prioritize top-tier institutions and foster innovation, particularly in AI. However, transitioning into a semiconductor manufacturing hub requires additional effort and time. A crucial starting point would be to build a semiconductor manufacturing facility, which is doable and requires very dedicated engineering leadership to action. Fortunately, the current government’s policies are highly encouraging and provide India an ideal path to make substantial progress in this direction within the coming decade.

ELE Times: Looking at Ceremorphic’s technology portfolio, help us understand its role in addressing the crucial needs of the high-performance computing era.

Venkat Mattela: Generative AI has played a critical role in enabling various technological applications to efficiently adopt Artificial Intelligence (AI) and supercomputing is the catalyst in training these AI models. At Ceremorphic, we embarked on this journey six years ago with a primary objective of developing ultra-low-energy, low-power supercomputing solutions. While few companies prioritized low-energy supercomputing at the time, it has now become an industry standard. With a portfolio boasting over 200 patented core technologies in this field, we have certainly has played a part in driving this shift. Our efforts in advancing low-energy supercomputing have had far-reaching implications, especially in the life sciences and pharmaceutical space.

We recently introduced our new platform, BioCompDiscoverX, which promises to revolutionize drug development by significantly accelerating the process, reducing costs, and enhancing efficacy. Furthermore, reiterating our commitment to high-performance computing in an energy-efficient manner, our upcoming chip will be manufactured using TSMC’s cutting-edge 3nm node.

ELE Times: What extra efforts and measures are necessary on the grassroots level to further elevate and enhance skill development across various sectors and emerging technologies?

Venkat Mattela: Progress at the grassroot level hinges on the coming together of supportive policies and robust funding infrastructures. As we enter a pivotal decade of innovation, we are witnessing promising advancements in these areas within India. Positioned in our golden era, we have the privilege of seizing numerous opportunities to leave a significant impact on the upcoming technological era.

Advanced universities are already leading the way by implementing specialized curriculums tailored to new technologies. But, to ensure widespread skill development, we must distil key learnings and core concepts and integrate them into the lower education levels to establish a solid foundation for future generations. This approach must go beyond theoretical knowledge and touch upon practical demonstrations of concepts. By encouraging innovation ideation from an early stage, we can sustainably cultivate a culture of creativity that will propel us to the forefront of every emerging technology.

The post Ceremorphic Driving Vision to Develop Sustainable Product Portfolio Across Sectors appeared first on ELE Times.

CSA Catapult in South Wales officially opens advanced packaging facility

IQE expands customer partnership with AWSC with multi-year supply agreement

Anritsu Company Expands Inline Sensor Family

Anritsu Company is proud to announce the launch of our new inline power sensor MA24103A which is designed to measure accurate Peak and True-RMS average power measurements from 25 MHz to 1 GHz and 2 mW to 150 W power range.

Several applications demand accurate peak and average power measurements well below the frequency range of 1 GHz. Agencies in Public Safety, Avionics (air traffic control and repair stations), and Railroads, etc. must maintain critical communications between the control centres and the vehicles. The slightest error in making measurements or maintaining a communication network in these markets could risk public safety or even have fatal consequences.

The advantage of lower frequencies is that they can propagate a longer distance and maintain communication with fast-moving vehicles. Normally, at lower frequencies, the power of the transmitting signal is in the range of watts, which makes the MA24103A more suited for these types of applications.

This highly accurate, Inline Peak Power Sensor communicates with a PC via USB or with an Anritsu handheld instrument equipped with the high-accuracy power meter option 19.

Some of the main markets that benefit from this low-frequency Inline Power Sensor include:

- Broadcast Network and Manufacturer: Lab performance accuracy and low insertion loss over a wide temperature range (0 ºC to 55 ºC), making it perfect for field applications.

- Railroads: to evaluate various systems like Positive Train Control Systems, End of Train (EOT) signals, automated train control systems, and FM voice base stations.

- Avionics: such as Civil and Military Airports for beacon testing, surveillance radar testing, localizer, and marker testing.

The post Anritsu Company Expands Inline Sensor Family appeared first on ELE Times.

Renesas Expands Quick Connect Studio with Real-Time Code Customization, Remote Debugging and Broad Portfolio of Supported Devices

Industry’s First-Ever Cloud-based System Development Tool Enables Rapid Prototypes and Co-Optimization of Software and Hardware

The post Renesas Expands Quick Connect Studio with Real-Time Code Customization, Remote Debugging and Broad Portfolio of Supported Devices appeared first on ELE Times.

Finished my first project

| I made a AND gate on a through hole board. Took a while (1hrs 30 mins) but it was worth it. Try to guess how old I am. (Hint): under 20yo. [link] [comments] |

EEVblog 1609 - Composite Amplifier Tutorial + Practical Demo

GaN vs SiC: A look at two popular WBG semiconductors in power

Wide bandgap semiconductors have taken both power electronics and high frequency circuits by storm, replacing so many applications that were previously dominated by silicon-based devices, e.g., LDMOS HPAs in base stations, IGBTs in high voltage DC/DC conversion etc. Specifically within power electronics, it is no secret that certain applications are demanding power dense solutions that operate at high switching frequencies to minimize switching losses. From traction inverters, onboard chargers, and high voltage DC-DC converters in EVs to uninterruptible power supplies (UPSs) and solar power converters in industrial/commercial applications; WBG semiconductors have carved out an extensive niche for many next generation electronics.

The SiC substrate has established itself for EV and some industrial applications. However, a bit more recently GaN has surfaced as a strong option for many overlapping applications. Understanding the major differences between these substrates in the context of high power circuits and their respective manufacturing considerations might shed light on the future of these two popular compound semiconductors.

WBG benefitsWBG materials are inherently able to operate at higher switching frequencies and with higher electric fields than the conventional Si substrate. When a semiconductor is heated up, its resistance tends to go down due to thermally excited carriers that are more abundant at higher temperatures, causing conduction. Higher bandgap semiconductors will require higher temperatures (more energy) to excite electrons across the bandgap from the valence band to the conduction band. This translates directly to more power handling capabilities and higher device efficiencies.

This can be seen in Table 1 where SiC and GaN exhibit much higher breakdown electric field, electron mobility, saturation velocity, and thermal conductivity than Si—all factors that enhance switching frequency and power density. However, high switching frequencies will lead to more losses and a lower efficiency FET, this is where optimizing the power device figure of merit (FoM) [Rds(on) x Qg], or optimizing the channel resistance and gate charge for lower conduction and switching losses, is critical.

|

Properties |

Si |

SiC |

GaN |

|

Band Gap (eV) |

1.12 |

3.3 |

3.44 |

|

Critical Breakdown Electric Field (V/cm) x106 |

0.3 |

2 to 4 |

3.3 |

|

Electron Mobility (cm2/Vs) |

1000 to 1400 |

650 |

1500 to 2000 |

|

Saturation Velocity (cm/s) x107 |

1 |

2 |

2.2 |

|

Thermal Conductivity (W/cm K) |

1.5 |

4.9 |

1.3 to 2.2 |

Table 1 Properties of Si, SiC, and GaN.

Generally, GaN FETs max out at around 650-V with power applications around 10 kW while 750-V and 1200-V SiC FETs are not unusual and applications can range from 1 kW up to the megawatts (Figure 1). SiC’s excellent thermal conductivity allows for similar power ratings in significantly smaller packages. However, GaN devices are able to switch faster (note the significantly higher electron mobility) which, in turn, can translate to a higher dV/dt, potentially allowing for more converter efficiency.

Figure 1: Power versus frequency plot for various power devices. Source: Texas Instruments

Manufacturing considerationsSiC, the recent golden child of power electronics, gained massive traction after Tesla’s announcement using exclusively SiC in the Model 3 back in March of last year. Since SiC MOSFETs were commercialized by Cree in 2010, the demand for SiC has steadily ramped up with key players taking advantage of available tax credits from the CHIPS act to grow operations and drive down the cost per wafer. Wolfspeed (formerly Cree), for instance, recently invested a total of $5 billion in a new production facility, the John Palmour (JP) manufacturing center to develop 200 mm (~8-inch) wafers.

However, it isn’t that simple: getting a foothold in SiC fabrication requires expensive equipment that is exclusively used for SiC. SiC boules are grown at temperatures in excess of 2700℃ at a rate at least 200 times slower than Si, which requires a large amount of energy. GaN on the other hand can largely use the same equipment as Si semiconductor processing where GaN epitaxial wafers can be grown on its respective substrate (often Si, SiC, or sapphire) at a temperature of 1000 to 1200℃—less than half that of SiC. SiC wafers are also nearly 50% thinner than Si wafers (up to 500 μm), leading to a fairly brittle material that is prone to cracking and chipping—another quality that requires specialized processing equipment.

According to Gregg Lowe, CEO at Wolfspeed, 6-inch SiC wafers cost ~$3,000 in 2018, a cost that has been trimmed down to ~$850 for a 7-inch wafer just 6 years later in 2024. And, as SiC power devices continue to mature, costs per wafer will continue to go down. A major leap in optimizing costs are growing wafer sizes and increasing the number of devices per wafer. For GaN-on-Si, this is relatively simple, larger diameter fabs can produce thousands of 8-inch wafers per week with excellent line yields (98%) afforded by CMOS process control. However, similar economies of scale can be applied to SiC wafer production as companies now advance toward 8-inch wafers where just ten years ago, mass production of 150 mm (~6-inch) wafers were really just on the horizon. And, while the SiC devices themselves may be more expensive than Si and GaN counterparts, the fact is, far less power devices are required to maintain the same performance. On the system level, this means less gate drivers, magnetics, and other peripherals devices that might otherwise be used in an Si-based design.

GaN moving beyond 700 VBecause of its excellent high frequency characteristics, GaN has already established itself as a suitable III-V semiconductor for high frequency circuits such as MMICs, hybrid microwave circuits, etc., along with other compound semiconductors such as gallium arsenide (GaAs) and indium phosphide (InP). GaN is particularly relevant for high power amplifiers (HPAs) in the transmit signal chain. Many of the GaN foundry services currently available generally address high frequency applications with GaN-on-SiC however, more recently, foundries are shifting their focus towards GaN-on-Si for both RF and power applications. Table 2 highlights some of the GaN process technologies for different companies globally. Note the table does not include all GaN foundries such as Global Foundries or UMC which will likely be major contenders in Gan-on-Si technologies.

| Company name | Foundry location | Technology name | Substrate | Wafer Size | Gate length | Cutoff frequency | Power Density | Wafer thickness | Breakdown voltage |

| Wolfspeed RF business (now MACOM) | US | G28V5, G28V4, G40V4, G28V3, G50V3, G50V3, G50V4 | SiC | – | 0.15 µm, 0.25 µm, 0.4 µm | Up to 40 GHz | Up to 8.5 W/mm | Up to 100 um | > 84 V, >120 V, >150 V |

| HRL Laboratories | US | T3 | SiC | – | 40 nm | Up to 150 GHz | – | – | > 50 V |

| NXP | US | – | SiC | 6 inches | – | – | – | – | – |

| MACOM/ OMMIC | US | GSiC140 | SiC | – | 140 nm | Up to 30 GHz | 5.5 W/mm | – | > 70 V |

| Northrop Grumman | US | GAN20 | SiC or Si | 4 inches | 0.2 µm | Up to 200 GHz | – | 100um | – |

| BAE systems | US | 0.14 µm GaN, 0.18 µm GaN | SiC | 4 to 6 inches | 0.14 µm, 0.18 µm | Up to 155 GHz | – | 55 and 100 um | > 80 V |

| Qorvo | US | QGaN25, QGaN15, QGaN25HV, QGaN50 | SiC | 4 inch | – | Up to 50 GHz | – | – | <28V, <40V, < 50 V, <65 V |

| WIN Semiconductors | Taiwan | NP12-01, NP25-20 | SiC | 4 inches | 0.12 µm, 025 µm | Up to 50 GHz | 4 W/mm, 10 W/mm | – | – |

| TSMC | Taiwan | – | Si | 6 inches | – | – | – | – | – |

| X-FAB | Germany and US | – | Si | 6 to 8 inches | 0.35 µm | – | – | – | – |

| Infineon/GaN systems | Austria and Malaysia | Gen1 (CoolGaN), Gen2 | Si | Up to 8 inches | – | – | – | – | – |

| UMS | Germany | GH15, GH25 | SiC | 4 inches | 0.15 µm, 0.25 µm | Up to 35 GHz | Up to 4.5 W/mm | 70 to 100 um | > 70 V, > 100 V |

| GCS | China | 0.15 µm, 0.25µm, 0.4µm, 0.5µm GaN HEMT Processes | Si and SiC | 4 to 6 inches | 0.15 µm, 0.25µm, 0.4µm, and 0.5µm | Up to 23 GHz | Up to 13.5 W/mm | – | > 150 V, > 200 V |

| Innoscience | China | – | Si | Up to 8 inches | 0.5 µm | – | – | – | – |

Table 2: Select GaN foundries and specifications on their technology.

SiC and GaN serve very distinct parts of the power spectrum, however, can higher voltage GaN devices be designed to creep up the spectrum and contend with SiC? The GaN pHEMTs that dominate GaN fabrication have breakdown voltages (~0.6 to 1.5 MV/cm) that generally cap out at around 650 V due to the inherent limits of its critical breakdown field [1-2]. Methods of reaching the intrinsic limits of 3 MV/cm are being explored in research in order to improve the breakdown characteristics of GaN devices.

More and more manufacturers are showcasing their 700-V GaN solutions. There have been talks of a 1200 V GaN FET; Transphorm released a virtual design of their 1200 V GaN-on-Sapphire FET in May of last year. Outside of this much of the talk of GaN moving up the power spectrum has remained in the R&D space. 1200-V Vertical GaN (GaN-on-GaN) transistors are also being researched by NexGen Power Systems with their Fin-JFET technology [3], a success that has allowed the company to receive funding from the US department of energy (DOE) to develop GaN-based electric drive systems. However, many of these solutions are not GaN-on-Si.

GaN-on-Si simply might have the major advantage of bandwagoning on the silicon semiconductor industry’s already established technology maturity, however, using the Si substrate comes with some design challenges. There are two major constraints: a large lattice mismatch and an even larger thermal mismatch between the GaN epitaxial layer and the host substrate causing tensile and compressive strains on the two substrates resulting in dislocations and higher defect densities (Table 3). Other substrates are being researched to overcome this issue, Qromis, for instance, has recently engineered a ceramic poly-aluminum nitride (AlN) layer that is CMOS fab compatible and CTE-matched to GaN.

|

Lattice mismatch |

Thermal mismatch |

|

|

GaN and Si |

16-17% |

116% |

|

GaN and Sapphire |

16% |

-25% |

|

GaN and SiC |

3.5% |

+33% |

Table 3 Lattice and thermal mismatch between GaN and Si, sapphire, and SiC. Source: [4]

Access to GalliumWhile GaN wafers are generally more convenient to manufacture, they do require a precious metal that is, by nature, in limited supply. There was strain on the gallium supply with the 2019 tariffs on Chinese imports ratcheted up significantly causing a 300% increase in gallium metal imported from China compared to 2018 where the surplus was likely stockpiled. China’s restrictions on gallium exports in August of last year further diminished the already small amount imported from China. The bans could have potentially signaled a problem as China produces nearly 98% of the world’s low-purity gallium.

However, the issue has not truly disrupted gallium-based wafer production (GaAs or GaN), largely due to the stockpiling and shifting to other sources for the rare metal (Table 4). Many countries now have the incentive to scale up the operations that, over a decade ago, were shut down due to China’s overproduction. Still, this may be something to consider if China further restricts its exports in the short term. It may also be important to note that since GaN wafers are produced by growing GaN crystals on top of a variety of substrates, relatively small amounts of gallium are used per device as compared to GaAs pHEMTs that are grown on semi-insulating GaAs wafers. So, while this may have been something to consider given the recent history of restricted gallium supplies, it has not really impacted GaN production and likely won’t in the future.

|

U.S. imports for consumption of unwrought gallium and gallium powders (2017 to 2021) |

|||||

|

2017 |

2018 |

2019 |

2020 |

2021 |

|

|

Country/Locality |

Quantity (kg) |

||||

|

China |

4,860 |

19,300 |

494 |

43 |

648 |

|

Taiwan |

— |

— |

500 |

1,000 |

500 |

|

Hong Kong |

2,000 |

5,400 |

1,000 |

— |

— |

|

Korea, Republic of |

1,140 |

1,280 |

11 |

— |

— |

|

Singapore |

525 |

— |

— |

— |

689 |

|

Japan |

540 |

1,070 |

400 |

512 |

4,510 |

|

United Kingdom |

6,180 |

50 |

428 |

— |

15 |

|

Germany |

— |

1,240 |

1,750 |

2,630 |

1,140 |

|

France |

1,980 |

417 |

109 |

163 |

— |

|

Belgium |

— |

— |

47 |

— |

86 |

|

Denmark |

28 |

— |

— |

— |

— |

|

Canada |

— |

— |

— |

84 |

792 |

|

Estonia |

— |

140 |

— |

— |

— |

|

Russia |

1,360 |

507 |

1,000 |

— |

500 |

|

Ukraine |

1,600 |

2,560 |

— |

— |

— |

|

South Africa |

23 |

23 |

— |

— |

— |

|

Total |

20,200 |

32,000 |

5,740 |

4,430 |

8,890 |

Table 4: US imports of unrefined gallium by country or locality according to USGS [5].

SiC and GaNAs it stands SiC and GaN dominate distinct parts of the power spectrum and therefore distinct applications with only some overlap. However, if GaN FETs can successfully increase in drain-source voltage without stifling its current massive manufacturing advantage, it may very well break out of its current place largely in consumer electronics (e.g., USB chargers, AC adapters, etc.) into higher power applications that SiC power devices currently dominate. SiC manufacturing has not stagnated though, and steady progress is being made in wafer size and yield to drive down the cost of SiC.

Aalyia Shaukat, associate editor at EDN, has worked in the design publishing industry for seven years. She holds a Bachelor’s degree in electrical engineering, and has published works in major EE journals.

Related Content

- Silicon carbide (SiC) counterviews at APEC 2024

- APEC 2023: SiC moving into mainstream, cost major barrier

- GaN Power Devices: Challenges and Improvements

- Selecting GaN or SiC devices with a Focus on Reliability

References

- Tian Z, Ji X, Yang D, Liu P. Research Progress in Breakdown Enhancement for GaN-Based High-Electron-Mobility Transistors. Electronics. 2023; 12(21):4435. https://doi.org/10.3390/electronics12214435

- Exploring an Approach toward the Intrinsic Limits of GaN Electronics. Sheng Jiang, Yuefei Cai, Peng Feng, Shuoheng Shen, Xuanming Zhao, Peter Fletcher, Volkan Esendag, Kean-Boon Lee, and Tao Wang. ACS Applied Materials & Interfaces 2020 12 (11), 12949-12954. DOI: 10.1021/acsami.9b19697

- R. Zhang et al., “Vertical GaN Fin JFET: A Power Device with Short Circuit Robustness at Avalanche Breakdown Voltage,” 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 2022, pp. 1-8, doi: 10.1109/IRPS48227.2022.9764569.

- Kaminski, Nando, and Oliver Hilt. “SiC and GaN Devices – Wide Bandgap Is Not All the Same.” IET Circuits, Devices & Systems, vol. 8, no. 3, 2014, pp. 227-236. https://doi.org/10.1049/iet-cds.2013.0223.

- “Gallium Statistics and Information.” U.S. Geological Survey, [last modified August 29, 2023], usgs.gov/centers/national-minerals-information-center/gallium-statistics-and-information. [accessed on 2023-10-26].

The post GaN vs SiC: A look at two popular WBG semiconductors in power appeared first on EDN.

Exploring Process Scenarios to Improve DRAM Device Performance

In the world of advanced semiconductor fabrication, creating precise device profiles (edge shapes) is an important step in achieving targeted on-chip electrical performance. For example, saddle fin profiles in a DRAM memory device must be precisely fabricated during process development in order to avoid memory performance issues. Saddle Fins were introduced in DRAM devices to increase channel length, prevent short channel effects, and increase data retention times.

Critical process equipment settings like etch selectivity or the gas ratio of the etch process, can significantly impact the shape of fabricated saddle fin profiles. These process and profile changes have significant impact on DRAM device performance. It can be challenging to explore all possible saddle fin profile combinations using traditional silicon testing, since wafer-based testing is time-consuming and expensive. To address this issue, virtual fabrication software (SEMulator3D) can be used to test different saddle fin profile shapes without the time and cost of wafer-based development.

In this article we review an example of using virtual fabrication for DRAM saddle fin profile development. We also assess DRAM device performance under different saddle fin profile conditions. This methodology can be used to guide process and integration teams in the development of process recipes and specifications for DRAM devices.

The Challenge of Exploring Different ProfilesImagine you are a DRAM process engineer, and have received nominal process conditions, device specifications, and a target saddle fin profile for a new DRAM design. You want to explore some different process options and saddle fin profiles to improve the performance of your DRAM device. What should you do? This is a common situation for integration and process engineers during the early R&D stages of DRAM process development.

Traditional methods of exploring saddle fin profiles are difficult and sometimes impractical. These methods involve the creation of a series of unique saddle fin profiles on silicon wafers. The process is time-consuming, expensive, and in many cases impractical, due to the large number of scenarios that must be tested.

One solution to these challenges is to use virtual fabrication. SEMulator3D allows us to create and analyze saddle fin profiles within a virtual environment and to subsequently extract and compare device characteristics of these different profiles. The strength of this approach is its ability to accurately simulate the real-world performance of these devices, but to do so faster and less-expensively than using wafer-based testing.

Let’s dive into the methodology behind our approach.

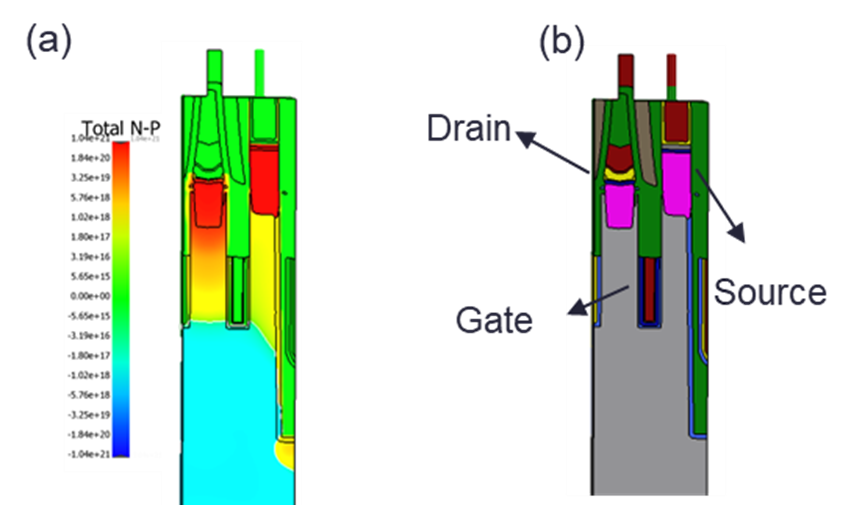

Creating Saddle Fin Profiles in a Virtual EnvironmentFirst, we input the design data and process flow (or process steps) for our device in SEMulator3D. The software can then generate a “virtual” 3D DRAM structure and provide a visualization of saddle fin profiles (Figure 1). In Figure 1(a), a full 3D DRAM structure including the entire simulation domain appears. To enable detailed device study, we cropped a small portion of the simulation domain from this large 3D area. In Figure 1(b), we extracted a cross sectional view of the saddle fin structure, which can be modified by varying a set of multi-etch steps in the process model. The section of the saddle fin we want to modify is identified as the “AA” (active area). We can finely tune the etch taper angle, AA/fin CD, fin height, taper angle, and additional nominal device parameters to modify the AA profile.

Using the structures, we built in SEMulator3D, we next assign dopants and ports to the simulated structure and perform electrical performance evaluation. Accurately assigning dopant species and defining dopant concentrations within the structure is critical to ensuring the accuracy of our simulation. In Figure 2(a), we display a dopant concentration distribution generated in SEMulator3D.

Ports are contact points in the model, which are used to apply or extract electrical signals during a device study. Proper assignment of the ports is very important. Figure 2(b) provides an example of port assignment in our test DRAM structure. By accurately assigning the ports and dopants, we can extract the device’s electrical characteristics under different process scenarios.

Figure 2: (a) Dopant concentration and (b) Port assignments (in blue)

Manufacturability Validation

Figure 2: (a) Dopant concentration and (b) Port assignments (in blue)

Manufacturability Validation

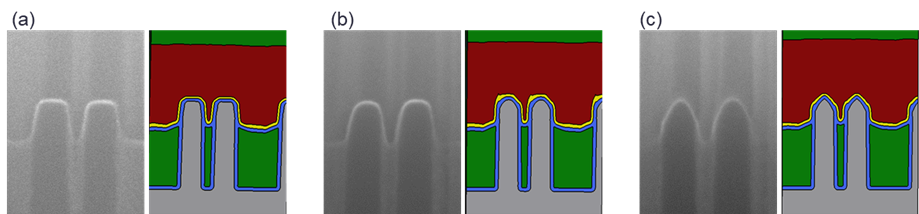

It is important to ensure that our simulation models match real world results. We can validate our model against cross-sectional images (SEM or TEM images) from an actual fabricated device. To ensure our simulated device matches the behavior of an actual manufactured chip, we can create real silicon test wafers containing DRAM structures with different saddle fin profiles.

To study different saddle fin profiles, we use different etch recipes on an etch machine to vary the DRAM wordline etch step. This allows us to create specific saddle fin profiles in silicon that can be compared to our simulated profiles. A process engineer can change etch recipes and easily create silicon-based etch profiles that match simulated cross section images, as shown in Figure 3.

In this case, the engineer created a nominal (Process of Record) profile, a “round” profile (with a rounded top), and a triangular shaped profile (with a triangular top). This wafer-based data is not only used to test electrical performance of the DRAM under different saddle fin profile conditions, but can also be fed back into the virtual model to calibrate the model and ensure that it is accurate during future use.

Figure 3: Cross section images vs. models: (a) Nominal condition (Process of Record), (b) Round profile and (c) Triangle profile

Device Simulation and Validation

Figure 3: Cross section images vs. models: (a) Nominal condition (Process of Record), (b) Round profile and (c) Triangle profile

Device Simulation and Validation

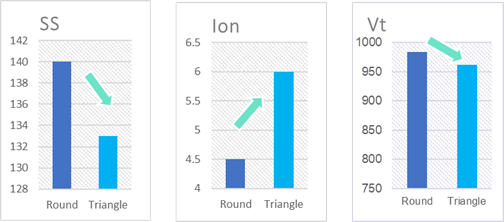

In the final stage of our study, we review the electrical simulation results for different saddle fin profile shapes. Figure 4 displays simulated electrical performance results for the round profile and triangular saddle fin profile. For each of the two profiles, the value of the transistor Subthreshold Swing (SS), On Current (Ion), and Threshold Voltage (Vt) are displayed, with the differences shown. Process integration engineers can use this type of simulation to compare device performance using different process approaches. The same electrical performance differences (trend) were seen on actual fabricated devices, validating the accuracy and reliability of our simulation approach.

Figure 4: Device electrical simulation results: the transistor performance difference between the Round and Triangular Saddle Fin profile is shown for Subthreshold Swing (SS), On Current (Ion), and Threshold Voltage (Vt)

Conclusion

Figure 4: Device electrical simulation results: the transistor performance difference between the Round and Triangular Saddle Fin profile is shown for Subthreshold Swing (SS), On Current (Ion), and Threshold Voltage (Vt)

Conclusion

SEMulator3D provides numerous benefits for the semiconductor manufacturing industry. It allows process integration teams to understand device performance under different process scenarios and lets them easily explore new processes and architectural opportunities.

In this article, we reviewed an example of how virtual fabrication can be used to assess DRAM device performance under different saddle fin profile conditions. Figure 5 displays a summary of the virtual fabrication process and how we used it to understand, optimize, and validate different process scenarios.

Virtual fabrication can be used to guide process and integration teams in the development of process recipes and specifications for any new memory or logic device and to do so at greater speed and lower cost than silicon-based experimentation.

The post Exploring Process Scenarios to Improve DRAM Device Performance appeared first on ELE Times.

TATA in Partnership with Satellogic Launches First Made in India Military Satellite

Tata Advanced Systems Ltd, a subsidiary of TATA Sons, in collaboration with Satellogic has successfully launched India’s first private sector-built sub-metre resolution earth observation satellite, TSAT-1A from the Kennedy Space Centre, Florida through SpaceX’s Falcon 9 rocket on April 7.

The TSAT-1A satellite assembled at TASL’s Karnataka facility represents a significant milestone in space technology. Its deployment as part of SpaceX’s inaugural Bandwagon flight, which also deployed a total of 11 satellites, underscores its importance in the realm of space exploration and satellite deployment.

The satellite is anticipated to bring about a paradigm shift in satellite imaging due to its high-resolution capabilities and rapid data delivery. Its configuration in low-earth orbit, coupled with its lightweight design of less than 50 kg, positions it as a versatile asset capable of serving a wide range of applications. Its potential impact on various sectors including defense and communication, makes it a pivotal development in the field of space technology.

The post TATA in Partnership with Satellogic Launches First Made in India Military Satellite appeared first on ELE Times.

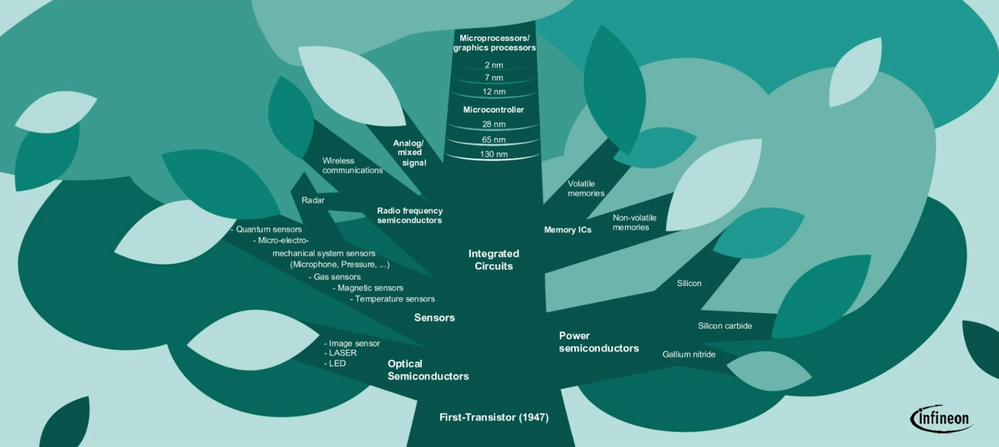

Semiconductors beyond nanometers

SCHUMACHER | Infineon Technologies AG

In today’s world, semiconductors are essential components of our everyday lives and the backbone of our economies. From the devices we use to communicate to the machines that power our factories, semiconductors are the building blocks that enable digitalization and decarbonization. However, public and policy debates about semiconductors often focus solely on their smallest feature size, measured in nanometers, which fails to capture the full complexity and importance of these high-tech goods.

At Infineon, we have developed a simple yet powerful way to understand semiconductors – our “Semiconductor Tree.” This intuitive structure provides a framework for discussing the different branches of the semiconductor industry, from power semiconductors to memory chips and microcontrollers. By exploring each branch of the tree, we can gain a better understanding of the unique properties and specialized industries that each one represents.

First transistor (1947)At the core of the semiconductor industry is the transistor switch, which was first demonstrated in 1947 by a team of researchers at AT&T Bell Labs. Since then, we have seen an exponential miniaturization roadmap, which has led to microprocessors that contain billions of transistors. However, this race to shrink transistors and integrate them as densely as possible into an Integrated Circuit (IC) requires extreme ultraviolet light and the most complex machines ever manufactured by mankind.

Power semiconductorsNotably, one branch of the semiconductor industry has focused on optimizing the individual transistor for faster switching and/or switching of ever-higher electrical power. These are known as power semiconductors and are becoming increasingly important as societies and economies move towards electrification as a means to decarbonize. Power semiconductors require sophisticated control of the underlying technologies and processes, and leading companies often control much of the value chain in-house.

Infineon’s power semiconductor business is an example of an Integrated Device Manufacturer (IDM), with major manufacturing sites in Germany, Austria, and Malaysia.

Memory, microcontrollers/microprocessors, and analog/mixed-signalAnother path to optimizing the transistor was to standardize it as much as possible, shrink it, and pack it as densely as possible. This gave rise to other branches in the semiconductor tree, including memory, microcontrollers, and microprocessors. Each of these branches has its unique properties, requirements, and industries. For instance, memory semiconductors allow storage and read-out of information in the form of electrical signals.

Microcontrollers, on the other hand, control everyday devices like washing machines, cars, airplanes, and industrial control systems. Analog/mixed-signal semiconductors act as the interface between our real world and the digital world, processing analog electrical signals like WiFi, Bluetooth, or radar chips for autonomously driving cars. Since analog signal processing doesn’t follow the same shrink path as analog, manufacturing analog/mixed signal today is often done at a sweet spot of 130-90nm.

Final ThoughtsThe world of semiconductors is vast and diversified, and it is crucial to have a more nuanced understanding of the importance and development of the respective industries. Semiconductors are essential building blocks for our personal lives, modern societies, and economies, and their importance will only grow as we continue to digitize and decarbonize.

As such, it is no surprise that semiconductors are at the center of global politics. By understanding the complexity and importance of semiconductors, we can have more precise discussions about their role in shaping our world.

The post Semiconductors beyond nanometers appeared first on ELE Times.

Samsung’s advanced packaging pivot with Nvidia production win

The news about Samsung snapping an advanced packaging order for Nvidia’s AI chips paired with high-bandwidth memory (HBM) chips underscores the strategic importance of next-generation packaging solutions. According to a report published in South Korean media outlet The Elec, Samsung’s advanced packaging team will provide interposer and 2.5D packaging technology for Nvidia’s AI processors.

It’s important to note that the GPU and HBM building blocks in these AI processors are supplied by other companies—most likely Nvidia’s GPUs manufactured on a TSMC process node and HBM chips designed and produced by Samsung’s archrival SK hynix.

What’s more important is how industry watchers relate this development to the insufficient capacity of TSMC’s chip-on-wafer-on-substrate (CoWoS) technology, which stacks chips and packages them onto a substrate. However, this supply shortage connected with the recent earthquake in Taiwan doesn’t hold much weight, and it’s most likely related to supply and demand issues.

Samsung calls its 2.5D packaging technology iCube; it places one or more logic dies such as CPUs and GPUs and several HBM dies on top of a silicon interposer, making multiple dies operate as a single chip in one package. It deploys parallel and horizontal chip placement to boost performance and combat heat buildup.

Figure 1 The iCube technology offers warpage control even with large interposers, and its ultra-low signal loss is paired with high memory density. Source: Samsung

Samsung’s advanced packaging pivot

Trade media has been abuzz with reports about Samsung beefing up its advanced packaging division by hiring more engineers and developing its own interposer technology. The company reportedly procured a large amount of 2.5D packaging equipment from Japanese semiconductor equipment supplier Shinkawa.

Another report published in The Elec claims that Applied Materials and Besi Semiconductor are installing hybrid bonding equipment at Samsung’s Cheonan Campus. Hybrid bonding enhances I/O and wiring lengths compared to existing bonding methods. TSMC offers hybrid bonding in its 3D packaging services called System on Integrated Chip (SoIC). Intel has also implemented hybrid bonding technology in its 3D packaging technology called Foveros Direct.

Media reports suggest that Samsung has recently ramped up the production capacity at its key site for advanced production in Cheonan to full utilization preceding Nvidia’s advanced packaging orders. Industry observers also expect that this advanced packaging deal with Nvidia could pave the way for Samsung to win the supply of HBM chips for pairing with GPU’s maker’s AI devices.

SK hynix is currently the major supplier of HBM chips for Nvidia’s AI processors, and Samsung is frantically working to close the gap. In fact, when Samsung established the advanced packaging business team in December 2023, the company’s co-CEO Kye-Hyun Kyung hinted about seeing the results of this investment in the second half of 2024.

Advanced packaging in Samsung’s roadmap

Kyung also pinned his hopes on a competitive advantage with Samsung’s memory chips, chip fabrication, and chip design businesses under one roof. Advanced packaging stands out in this semiconductor technology portfolio due to its intrinsic link to large and powerful AI chips and system-in-package (SiP) devices.

Figure 2 Next-generation packaging technologies are in the limelight due to the massive demand for AI chips. Source: Samsung

Like TSMC and Intel Foundry, Samsung is aggressively investing in advanced packaging technologies like silicon interposers while also steadily expanding its production capacity. Interesting times are ahead for next-generation packaging solutions.

Related Content

- Is 3D IC The Next Big Profit Driver?

- Heterogeneous Integration and the Evolution of IC Packaging

- Understanding the Big Spend on Advanced Packaging Facilities

- Tighter integration between process technologies and packaging

- Advanced IC Packaging: Fundamentals for the ‘More than Moore’ Era

The post Samsung’s advanced packaging pivot with Nvidia production win appeared first on EDN.

Aehr quarterly revenue halves due to short-term SiC-related order push-outs following EV market slowdown

Examining an Air Filter with a RANS Turbulence Model

Joseph Carew | Comsol

HVAC systems do more than provide the smooth, chilled air that flows when the temperature outside rises. Within these systems, air moves through filters to ensure high air quality. With clean air at stake, modeling and simulation can be used to gain an in-depth understanding of the physics behind the behavior of air as it moves through a filter…

Modeling an Air FilterThe filters within HVAC systems rely on a material (often fiberglass or cotton folds) capable of straining the air and catching particulates like dust, pollen, and bacteria. These materials impact the flow of the air, catching the unwanted particulates while simultaneously allowing the filtered air to flow through. Modeling these devices and the turbulent flow they induce allows for determining the effectiveness of different materials when they are used for filters, helping designers to narrow down the material options before investing in real-life, experimental versions.

In this blog post, we will look at a common air filter geometry (shown below) as our example.

Modeling this air filter begins with the CFD Module, an add-on product to the COMSOL Multiphysics® software, which enables users to create Reynolds-averaged Navier–Stokes (RANS) turbulence models in open and porous domains. In this example, the air filter is modeled as a highly porous domain with 90% of the material occupied by cylindrical pores with a diameter of .1 mm. The support of the air filter is represented by a frame with no-slip walls. For this example, we employed the Turbulent Flow, k-ω interface because of its accuracy for models with many walls, including no-slip walls. (An in-depth look at the model setup can be found in the model documentation, which can be accessed via the button at the end of this blog post.)

Evaluating the ResultsSolving the model allows for visualizing the change in turbulence, velocity, and pressure as air moves toward, through, and past the filter. The computation begins with the air moving toward the filter (purple in the image below). When the air passes through the filter, the interstitial velocity increases (although the porous-averaged velocity remains constant), resulting in an increase in turbulence kinetic energy. Additionally, there is an abrupt pressure drop due to the increase in velocity and the increased friction and pressure losses, which stem from the high number of wall surfaces. As for the behavior of the air as it moves away from the filter, the frame of the filter prevents the air from moving freely, instead causing downstream wakes of air.

The visualization of the air moving through the filter can be used to conclude whether or not the filter will remove contaminants from the air. To confirm this conclusion, the solution can be evaluated with different slice plots. One of the slice plots for this example indicates that the velocity of the air is most impacted by the porous air filter and the frame and that it homogenizes through the wake region. A slice plot measuring the turbulence kinetic energy shows that the turbulence kinetic energy peaks noticeably within the filter and attains typical values on the no-slip walls.

In general, the model points to a pressure drop and a dramatic increase in turbulence within the filter, creating perturbations in velocity perpendicular to the main direction of the flow thus also increasing the probability of the particles to collide with the pore walls and stay there. In other words, the increase in turbulence provides the mixing required for filtering out the unwanted particulates, which otherwise would flow through the pores undisturbed.

The post Examining an Air Filter with a RANS Turbulence Model appeared first on ELE Times.

Broadcom brings together two proven portfolios to deliver complete hybrid cloud cybersecurity

Rob Greer, Vice President and General Manager, Enterprise Security Group, Broadcom

Merging Carbon Black with Symantec forms the new Enterprise Security Group at BroadcomIt is clear, there is no let-up in cyberattacks, so the timing could not be better for Broadcom to bring Carbon Black and Symantec together. These engineering-first, innovation-centric brands are both committed to delivering proven cybersecurity solutions and support built to meet the unique and highly complex challenges of the largest and most heavily regulated enterprise customers and partners. Broadcom will make significant investments in both brands, and continue to offer both portfolios under the Enterprise Security Group business unit. Our joint mission is to help secure the world’s largest and most advanced enterprises.

Symantec’s portfolio, with some of the best security technology and research in the world, concentrates on data and network protection, while Carbon Black’s complimentary portfolio specializes in both endpoint detection and response (EDR) and application control. Bringing both network and data telemetry to Carbon Black will enable greater visibility and control for our joint customers. Under the new Enterprise Security Group, customers will continue to receive the best service with more dedicated resources and focused support than ever before. What can you expect in the near-term? Let’s take a closer look at innovation, customers, and partners.

InnovationBroadcom’s financial stability empowers Symantec and Carbon Black product portfolios to innovate at a massive scale. Our customers will benefit from access to an enhanced enterprise-grade portfolio and leading technological advancements, with unparalleled service and support.

Initially, we will invest in R&D to improve – and extend the life — of the products our customers are using both on-prem and across hybrid clouds. We also are excited about the complementary nature of both sets of technologies and the combined value they will provide our customers, opening up more choices. For example, Symantec has a data center security product to protect traditional workloads in the data center. Carbon Black has a complementary solution. With access to these two technology sets, defenders will be even better equipped to protect their infrastructures.

On the talent side, we will be making significant investments in engineering. Carbon Black is known for its outstanding, customer-centric engineering capabilities, and we are committed to investing in Carbon Black’s incredible franchise and putting the best talent in the best roles. For example, both Carbon Black and Symantec have existing engineering sites in India. While we see the opportunity to converge them, we do not expect to make headcount reductions in those sites. In fact, we plan to make more investments in India. In addition, we will continue to invest in support and R&D for both brands, retaining key technical and product leaders to ensure continued success today and in the future.

CustomersSymantec and Carbon Black product portfolios will continue to operate in their current states for the immediate future. Our customers can expect to gain access to an extensive and robust enterprise-class portfolio supported by top-tier security experts, intelligence, and continued innovation, all backed by the financial stability of Broadcom.

Looking ahead, we will explore innovative new ways to deliver solutions to our customers. This will involve intensely focusing on the technologies that provide the most value to our customers and partners and invest more resources in those areas so our customers realize even greater value and ROI.

PartnersAt Broadcom, we take a very focused go-to-market approach. As Hock Tan, our CEO, says, “We do what we do best.” By focusing on our core strengths and not trying to be all things to everyone, we open big opportunities for our partners to step in, fill gaps, and profit from them. The addition of the Carbon Black portfolio provides a great opportunity for our partners to drive more revenue, win more customers, and grow. Broadcom will provide the necessary training, support and other resources to ensure our partners’ success with Carbon Black solutions. For examples of our breakthrough approach to building a highly scalable, close-to-the-customer partner ecosystem, look no further than our Global Cybersecurity Aggregator Program (GSAP) and the Expert Advantage Partner Program. Partners in these programs deliver high-value services to customers of all sizes – including our largest enterprise accounts.

Building a strong security futureOver the next few weeks, we will be sharing more details about how today’s announcement will further benefit our customers and partners. In the meantime, we encourage you to visit our online resources to access additional information. As ransomware attacks and other cybersecurity threats continue to rise, you can be rest assured that Carbon Black and Symantec together will provide the mission-critical technologies to defend the most complex, highly regulated organizations.

The post Broadcom brings together two proven portfolios to deliver complete hybrid cloud cybersecurity appeared first on ELE Times.

element14 brings latest Silex Wi-Fi 6 Radio Development Kit from Gateworks to Industrial Developers Worldwide

element14 will be the only distributor to offer this kit for sale at Embedded World 2024.

element14 has announced the availability of Gateworks’ latest Wi-Fi 6 Development Kit – GW11048-5-A.

Gateworks will showcase its cutting-edge technology kit during the Embedded World 2024 exhibition in Nuremberg, Germany, from the 9th to 11th April. element14 has been chosen as the exclusive distributor of the kit, making it the only place where customers can purchase it during the event.

The Wi-Fi 6 Development Kit is designed to facilitate the validation of the Silex SX-SDMAX and SX-PCEAX Wi-Fi 6 radios, providing developers with a seamless out-of-the-box evaluation experience. It delivers ruggedized wireless connectivity for a diverse range of industrial applications, from remote real-time monitoring to predictive maintenance and enhanced logistics.

This latest innovation comes with a pre-loaded Linux system and all the necessary accessories to get started quickly.

Key features include:

- Supports Silex SX-SDMAX and SX-PCEAX Wi-Fi 6 radios (radios not included)

- Includes Venice GW7200 Single Board Computer (SBC) with pre-loaded Linux drivers

- Onboard NXP i.MX8M Mini processor (1.6 GHz quad-core)

- 8GB eMMC flash storage and 1GB LPDDR4 DRAM

- Two Gigabit Ethernet ports and two Mini-PCIe expansion slots

- Multiple connectivity options including MicroSD, Nano SIM, I2C, SPI, and serial ports

- Real-time clock, voltage and temperature monitoring

- Wide input voltage range (8 to 60VDC) with PoE support

- Operates in temperatures ranging from -40°C to +85°C

“We are thrilled to provide Gateworks’ WI-FI 6 development kit to our customers. This cutting-edge technology is a game-changer for those seeking to develop and deploy IoT applications and systems. We look forward to seeing its capabilities showcased at the exhibition and support our customers with all their development needs”, said Romain Soreau, Head of Single Board Computing at element14.

In addition to the Wi-Fi 6 Development Kit, element14 also offers Gateworks Corporation’s complete line of products for industrial applications.

Gateworks will be highlighting their line of railway solutions at Embedded World, aimed at enhancing the efficiency and safety of rail yards, such as rugged Gateworks Single Board Computers (SBCs) combined with a variety of wireless options such as high-precision GNSS Mini-PCIe cards. These solutions enable capabilities such as centimetre-level accuracy in tracking and monitoring critical data, streamlined yard operations and enhanced customer service for rail operators.

The post element14 brings latest Silex Wi-Fi 6 Radio Development Kit from Gateworks to Industrial Developers Worldwide appeared first on ELE Times.

Designers lead advances in CT scanning field

Courtesy: Avnet

When a doctor tells you to get a CT scan, they’re calling on a powerful medical imaging technology for insights only otherwise possible through invasive procedures.

Computed tomography (CT) exploits the penetrating nature of X-rays. A standard X-ray shines a 2D beam of high-energy photons through the subject. How these photons are detected has changed over the years. It was once just photographic film, but today it is more likely to be a digital detector.

Since bone, muscle and fat each absorb X-rays differently, the image captured is effectively the shadow cast by the mix of tissues in the body. Rather than create an image directly from the photons detected, computed tomography processes that captured data to synthesize an image.

In CT scanning, a source illuminates the subject using a fan-shaped beam of X-rays that are picked up by an arc-shaped array of digital detectors. The source and the detector are mounted on a circular gantry, which rotates around the patient, taking scans from multiple angles.

The resulting scans are not directly interpretable as an image. The scans are combined in a computer, creating a more detailed 2D “slice” through the body. Many CT scanners also coordinate the movement of the patient with the gantry’s rotation, creating a sequence of slices through the body that can be processed into a 3D image.

Seeing the advantages of CT in medical imaging Figure 1: Computed tomography is an advanced medical imaging technology. New developments are making it even more useful for healthcare professionals and safer for

Figure 1: Computed tomography is an advanced medical imaging technology. New developments are making it even more useful for healthcare professionals and safer forpatients.

CT scans can render more detail about internal structures than ordinary X-rays and can present that data in augmented 2D or 3D, making it easier to interpret. They are also relatively fast, which makes them useful for providing insights about injuries to the head, spine, chest, abdomen and pelvis.

The ability to post-process CT images means that they can provide a useful basis for detecting tumors and cancers, their size, location, and how they have spread. They can also reveal internal bleeding and the spread of infection as well as enable doctors to visualize blood vessels, aneurysms and blockages throughout the body.

CT imaging can be used to reduce the invasiveness of some procedures. The ability to differentiate diseased tissue helps surgeons avoid removing healthy tissue unnecessarily. Similarly, the 3D detail possible with CT imaging can provide a useful basis for planning procedures such as biopsies, surgery, implants, and radiation treatment.

The technique can reveal the detailed health of bones and joints, making it easier to understand wear or disease and to diagnose fractures. CT scans can also help track the progress of disease and reveal the effectiveness of treatments such as chemotherapy.

There are challenges associated with CT scanning. They usually involve greater exposure to ionizing radiation than is common with standard X-rays. Patients may also react badly to the contrast agents used to improve the CT scan’s effectiveness.

Navigating the key trade-offs in CT scanner design Figure 2: CT scanning is a non-invasive solution to seeing inside the body. It can reveal vital details for healthcare professionals but there are still areas for improvement.

Figure 2: CT scanning is a non-invasive solution to seeing inside the body. It can reveal vital details for healthcare professionals but there are still areas for improvement.

Developers of CT scanners work with two forms of constraints. The first is the paramount nature of combining innovation with patient safety when using ionizing radiation. The second is the tension that can bring for patients and care providers. The availability of new technologies and capabilities must always be met with the best judgment and a conservative attitude.

There are technical trade-offs in CT design too. Perhaps the most important of these is between image quality and radiation dose levels. Higher doses may improve image clarity at the cost of greater exposure. Technologies such as iterative image reconstruction and denoising algorithms based on machine-learning techniques can now replicate some of the image-quality gains of high-dose scans at lower doses.

Trade-offs also exist between the speed of scanning and image resolution. Faster scanning reduces artifacts introduced by patient movements but can result in lower spatial resolutions. Scanning more slowly can deliver higher resolution if the patient is still for long enough.

Designers also need to decide which market niche they want to address. For example, designing a scanner with a large field of view makes it easier to scan large body parts, but requires larger, more expensive detector arrays. Other trade-offs may have to be made between scanner flexibility and specialization, hardware quality and maintenance costs, and software capabilities and reliability.

There are also financial considerations over initial cost and long-term upgradability. Buying a CT scanner means a large upfront outlay and substantial operating costs. Buyers may be prepared to choose a scanner engineered to evolve, rather than a lower-cost machine with a more limited useful lifetime.

Figure 3: CT scanner represent a significant capital outlay. New technologies are tackling the ROI on machines, with capability and longevity in mind.

Making innovations in CT design

Figure 3: CT scanner represent a significant capital outlay. New technologies are tackling the ROI on machines, with capability and longevity in mind.

Making innovations in CT design

Despite the constraints and trade-offs outlined above, there are many avenues for innovation in CT design. Each detector usually has a scintillator, which emits visible light when it is hit with X-rays, mounted over a digitizing photodetector circuit. A basic CT scanner will have one arc of these detectors, but more sophisticated variants will have multiple arcs so that they can sample multiple “slices” simultaneously. There may be as many as 256 arcs.

To support the high number of detectors, semiconductor companies are engineering 128-channel analog-to-digital converters (ADCs). These ADCs can be mounted in modules to produce 256-channel capabilities. The chips have low-power, low-noise, low-input-current integrators. Simultaneous sample-and-hold circuits ensure that all samples are taken at once. Some ADCs targeting medical applications offer resolutions of up to 24 bits.

Achieving low-dose CT imagingDifferent beam energies can reveal different things about the subject they are illuminating. Radiologists can adjust the beam strength used in the scan to pick out specific details. This is called the spectral CT technique.

Another approach is to use a dual-layer detector, with the top layer absorbing the lower-energy X-ray photons and a lower layer absorbing the higher-energy photons. This technique can reveal more about how the X-rays have been affected by their passage through the subject material.

A further innovation involves single-photon capture detection, in which a semiconductor device is used to directly count each X-ray photon. This gives scope for lower-dose CT imaging, since it does away with potential photon losses in the scintillation process of conventional detectors. It also makes it possible to measure the arrival energy of every photon, again giving greater insights into how it has been affected by passing through the patient.

In dual-source CTs, two source/detector array pairs are mounted on the rotating gantry ring at 90 degrees to each other. This arrangement gives good coverage of the patient while minimizing interference between the sources.

The two sources can run at different energies, which brings the advantages of spectral CT discussed above. They can also acquire a whole slice image more quickly than a single-source scanner, which gives them greater temporal resolution for imaging moving features such as a beating heart. This in turn reduces motion artefacts in the final scan. Faster scans may also be more acceptable to some patients.

Developing high-resolution CT scannersHigh-resolution CT scanners produce very thin slices of less than 1 mm. They use more, smaller detectors, to achieve higher spatial resolutions than standard scanners. The extra resolution makes it easier to detect and characterize small features accurately.

Such scanners usually have sophisticated image-reconstruction algorithms to enhance image quality and detail, which is particularly important for visualizing fine structures and edges. They can also have features such as enhanced X-ray beam management. These techniques give higher contrast images than standard scanners.

CT scanners are enormously valuable for producing insights into patient health without the need for invasive procedures. Their developers can call on rapidly evolving technologies, such as detector electronics and machine-learning techniques, to provide enormous scope for innovation. Responsibility for patient safety means the adoption of new technologies can feel slow.

Fortunately, designers can make a real difference here by exploring the systemic trade-offs involved in the development of novel CT scanners to produce capabilities that are engineered to encourage rapid uptake. For example, designing a detector sampling and digitization circuit with a lower noise floor will enable higher-resolution scans at the same beam energy, or similar resolutions at lower doses.

An FPGA accelerator board may be used to speed up image-processing algorithms, increasing the scanner’s throughput and so cutting the cost of individual scans. Or perhaps there’s a better way to manage power use in the scanner, extending its reliability and so cutting its operating costs.

Avnet recognizes the holistic challenge of developing medical imaging products and has the resources to help OEMs address them.

The post Designers lead advances in CT scanning field appeared first on ELE Times.

Infineon PSOC Edge E8x microcontrollers are the first devices designed to meet the new PSA Level 4 certification requirements

With embedded security considered to be a vital aspect in the deployment of Internet of Things (IoT) applications, Infineon Technologies AG has announced that its new PSOC Edge E8x MCU product family has been designed to meet the highest certification level provided by the Platform Security Architecture (PSA) Certified program, a framework for embedded security. The PSA Certified Level 4 device certification is targeted by implementing an on-chip, hardware-isolated enclave that provides secured boot, key storage and crypto operations in all PSOC Edge E8x devices.

“By aspiring to achieve this robust embedded security certification, IoT designers for edge applications such as wearables and smart home applications can be confident their products can achieve highest levels of security,” said Erik Wood, Senior Director Product Security for IoT, Computer and Wireless business, Infineon Technologies. “Integrating hardware security on the MCU also unlocks new edge computing markets such as printers and payment terminals that previously required discrete security chips. As a security leader, we are committed to enabling designers to reach the highest level of security for all applications.”

PSA Certified is a security framework established by Arm and industry partners in 2019. It provides both design guidelines and independent security evaluations through third-party labs intended to assure that all connected devices are built upon a Root of Trust. PSA Certified certifications achieved by an MCU extend through the value chain, allowing device builders and application providers to reuse that certification as they deploy products in the field.

“Connected device security is critical to scaling IoT deployments, and something that Arm and its ecosystem is committed to continuing to drive through initiatives like PSA Certified,” said David Maidment, Senior Director, Secure Devices Ecosystem at Arm. “We applaud Infineon’s ongoing commitment to robust device security by striving to achieve PSA Certified Level 4 iSE/SE for its new family of MCUs.”

The post Infineon PSOC Edge E8x microcontrollers are the first devices designed to meet the new PSA Level 4 certification requirements appeared first on ELE Times.