Feed aggregator

Cornell’s Huili Grace Xing to receive 2025 University Research Award in Technology from SIA and SRC

NUBURU strengthens balance sheet, advances defense-tech acquisition program and revamps blue laser business

The Quantum Leap: How AI and Quantum Computing Are Driving Lead Time Optimization and Supply Chain Resilience in Semiconductor Innovation

Introduction

Silicon has been the primary driver of the computing growth for decades, but Moore’s Law is now reaching its limits. As the need for chips to be faster and more energy-efficient grows, the pressure on supply chains are like never before due to shortages and geopolitical tensions.

This is where AI and quantum computing come into play. It is not science fiction; they are

helping discover new semiconductor materials and optimizing production scheduling in

wafer fabs. This results in shorter lead times, reduced risks, and a more resilient supply chain.

For engineers and procurement teams, the message is simple: keeping up in the chip world

will soon require leveraging both quantum computing and AI together.

Quantum Computing and AI Integration in Semiconductor Innovation

Quantum computing works with qubits, which, unlike classical bits, can exist in

superposition, representing both 0 and 1 simultaneously. This enables quantum processors to tackle complex simulations that classical computers struggle with, such as modelling atomic-level behaviour in new semiconductor materials.

AI enhances this capability. By applying predictive analytics to quantum simulations,

machine learning models identify promising material candidates, predict their performance,

and recommend adjustments. This transforms what was once a slow trial-and-error process

into actionable insights, saving years of laboratory work.

Take Google’s Willow processor as an example. It is the follow-up to Sycamore, and while not built solely for materials research, it demonstrates how quantum systems can scale and

reduce errors. When combined with machine learning, it provides an unprecedented view of

material properties critical for chip innovation.

As Anima Anandkumar points out: “AI helps us turn the raw complexity of quantum

simulations into insights engineers can actually use.”- Anima Anandkumar, Professor,

Caltech & Senior Director of AI Research, Nvidia.

Together, AI and quantum computing are laying the foundation for a fundamentally new

approach to chip design.

AI-Driven Material Science: Operational and Market Impact

When it comes to discovering new semiconductors, atomic-level precision is crucial. AI-

powered quantum models can simulate electron behaviour in materials such as graphene,

gallium nitride, or perovskites. This enables researchers to evaluate conductivity, energy

efficiency, and durability before performing laboratory tests, greatly accelerating material

qualification.

The practical impact is significant. Material validation traditionally took years, but early

studies indicate that timelines can be shortened by 30 to 50 percent. This allows wafer fabs to operate more efficiently, align production with new innovations, and minimize idle time.

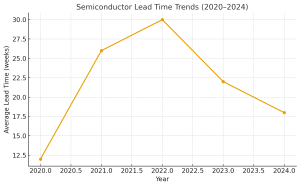

Market pressures further complicate the situation. During the 2021 shortage, lead times

increased from approximately 12 weeks to over a year. With AI, companies can anticipate

supply chain disruptions and proactively adjust sourcing strategies. Quantum simulations also expand the range of usable materials, reducing reliance on a single supplier or high-risk region.

Figure 1. Semiconductor lead times spiked from 12 weeks in 2020 to over 30 weeks in 2022 before easing. AI-quantum integration can help stabilize these fluctuations by enabling predictive analytics and diversified sourcing.

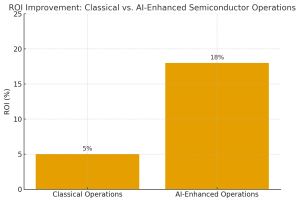

The return on investment is remarkable. According to Deloitte, companies that integrate AI

into R&D and supply chain operations are achieving double-digit efficiency gains, primarily due to improved yield forecasting and reduced downtime. Google’s quantum research team

has demonstrated that AI-driven simulations can narrow the list of promising materials from thousands to just a few within weeks, a process that would normally take years using classical computing. This dramatic compression of the R&D cycle fundamentally changes competitive dynamics.

Strategic Insights for Procurement and Supply Chain Leaders

For procurement and supply chain leaders, this is more than just a technical upgrade; it

represents a genuine strategic advantage. AI-powered quantum tools help optimize lead

times, enabling more precise supplier contracts and reducing the need for excess buffer stock. Predictive analytics also allow teams to identify potential risks before they affect wafer fabs or delay customer deliveries.

Supply chain resilience is also enhanced. When AI-guided quantum simulations confirm

alternative semiconductors that can be sourced from different regions, procurement teams

reduce exposure to geopolitical risks or natural disasters. This approach aligns with national

initiatives such as the U.S. CHIPS and Science Act and the EU Chips Act, both of which

promote stronger local production and more resilient sourcing strategies. Quantum-AI

modelling provides the technical confidence required to qualify these alternative supply

streams.

“The upward trajectory for the industry in the short-term is clear, but the companies that can manage their supply chains and attract and retain talent will be the ones well-positioned to sustain and benefit from the AI boom.”- Mark Gibson, Global Technology Leader, KPMG

Figure 2. Firms adopting AI-enhanced semiconductor operations achieve significantly higher ROI, with consulting studies reporting double-digit efficiency gains compared to classical operations.

At the end of the day, companies that successfully integrate these technologies do not just

bring products to market faster; they also gain a genuine competitive edge in today’s unpredictable global markets. In the semiconductor industry, a delay of a few weeks can result in billions in lost revenue, so agility is essential for survival.

Future Outlook: Scaling Quantum AI Impact on Semiconductor Manufacturing

Looking ahead, the next major development appears to be full-stack quantum-AI design.

Imagine quantum processors running full-chip simulations while AI optimizes them for

speed, efficiency, and manufacturability. Although we are not there yet, incremental

advances in photonic circuits and spintronic components are already producing tangible

results.

For manufacturing teams, the challenge will be maintaining flexibility in supply chains. As

new materials move from simulation to pilot production, procurement and fab teams must

scale in coordination. Today’s quantum processors are not perfect, as they still face

limitations in qubit counts, error rates, and scalability, but if progress continues, practical

industrial applications could emerge within the next ten years. Companies that begin planning now, by developing roadmaps and forming strategic partnerships, will gain a significant advantage.

Conclusion

Right now, the semiconductor industry is at a critical turning point. Combining AI’s

predictive capabilities with quantum computing’s atomic-level insights can accelerate

discovery, shorten lead times, and make supply chains significantly more resilient.

For engineers and procurement leaders, the message is clear: adopting AI-quantum

integration is not just about technology; it is about remaining competitive. The next major

advancement in silicon will not occur by chance. It will be carefully designed, optimized, and engineered using AI and quantum computing together.

The post The Quantum Leap: How AI and Quantum Computing Are Driving Lead Time Optimization and Supply Chain Resilience in Semiconductor Innovation appeared first on ELE Times.

System-level tool streamlines quantum design workflows

Quantum System Analysis software, part of Keysight’s Quantum EDA platform, simulates quantum architectures at the system level. It unifies electromagnetic, circuit, and quantum dynamics domains to enable early design validation in a single environment.

By modeling the full quantum workflow—from initial design through system-level experiments—the software reduces reliance on costly cryogenic testing and shortens time-to-validation. It includes tools for optimizing dilution fridge input lines to manage thermal noise and estimate qubit temperatures. A time dynamics simulator models quantum system evolution using Hamiltonians derived from EM or circuit simulations, accurately emulating experiments such as Rabi and Ramsey pulsing to reveal qubit behavior.

Quantum System Analysis supports superconducting qubit platforms and can be extended to other modalities such as spin qubits. It complements Quantum Layout, QuantumPro EM, and Quantum Circuit Simulation tools.

The post System-level tool streamlines quantum design workflows appeared first on EDN.

CAN FD transceiver boosts space data rates

Microchip’s ATA6571RT radiation-tolerant CAN FD transceiver supports data rates to 5 Mbps for high-reliability space communications. Well-suited for satellites and spacecraft, it withstands a total ionizing dose of 50 krad(Si) and offers single-event latch-up immunity up to 78 MeV·cm²/mg at +125 °C.

Unlike conventional CAN transceivers limited to 1 Mbps, the ATA6571RT handles CAN FD frames with payloads up to 64 bytes, reducing bus load and improving throughput. It ensures robust, efficient data transmission under harsh space conditions, while backward compatibility with classic CAN enables an easy upgrade path for existing systems.

A cyclic redundancy check (CRC) algorithm enhances error detection and reliability in safety-critical applications. The transceiver also delivers improved EMC and ESD performance, along with low current consumption in sleep and standby modes while retaining full wake-up capability. It interfaces directly with 3-V to 3.6-V microcontrollers through the VIO pin.

The ATA6571RT transceiver costs $210 each in 10-unit quantities. A timeline for availability was not provided at the time of this announcement.

The post CAN FD transceiver boosts space data rates appeared first on EDN.

Reconfigurable modules ease analog design

Chameleon adaptive analog modules from Okika provide preprogrammed, ready-to-use analog functions in a compact 14×11-mm form factor. Each module employs the company’s FlexAnalog field-programmable analog array (FPAA) architecture—a reconfigurable matrix with over 40 configurable analog modules (CAMs), including filters, amplifiers, and oscillators. Nonvolatile memory and reconfiguration circuitry are integrated on the module.

Chameleon simplifies analog designs that need flexibility without the complexity of firmware or digital control. Modules function as fixed analog blocks straight out of the box—no microcontroller or firmware required. Configurations can be reprogrammed in-system or using any 3.3-V SPI EEPROM programmer.

Anadigm Designer 2 software provides parameter-tuning and filter-design tools for simulating and verifying Chameleon’s performance. Typical applications include programmable active filters, sensor signal conditioning and linearization, and industrial automation and adaptive control, as well as research and prototyping.

Chameleon extends the FlexAnalog platform into an application-ready design that adapts easily. For pricing and availability, contact sales@okikadevices.com.

The post Reconfigurable modules ease analog design appeared first on EDN.

Vertical GaN advances efficiency and power density

onsemi has developed power semiconductors based on a vertical GaN (vGaN) architecture that improves efficiency, power density, and ruggedness. These GaN-on-GaN devices conduct current vertically through the semiconductor, supporting higher operating voltages and faster switching frequencies.

Most commercially available GaN devices are built on silicon or sapphire substrates, which conduct current laterally. onsemi’s GaN-on-GaN technology enables vertical current flow in a monolithic die, handling voltages up to and beyond 1200 V while delivering higher power density, better thermal stability, and robust performance under extreme conditions. Compared with lateral GaN semiconductors, vGaN devices are roughly three times smaller.

These advantages translate to significant system-level benefits. High-end power systems using vGaN can cut energy and heat losses by nearly 50%, while reducing size and weight. The technology enables smaller, lighter, and more efficient systems for AI data centers, electric vehicles, and other electrification applications.

onsemi is now sampling 700-V and 1200-V vGaN devices to early access customers. For additional information about vertical GaN, click here.

The post Vertical GaN advances efficiency and power density appeared first on EDN.

SoC delivers dual-mode Bluetooth for edge devices

Ambiq’s Apollo510D Lite SoC provides both Bluetooth Classic and BLE 5.4 connectivity, enabling always-on intelligence at the edge. It is powered by a 32-bit Arm Cortex-M55 processor running at up to 250 MHz with Helium vector processing and Ambiq’s turboSPOT dynamic scaling. A dedicated Cortex-M4F network coprocessor operating at up to 96 MHz handles wireless and sensor-fusion tasks.

According to Ambiq, its Subthreshold Power Optimized Technology (SPOT) delivers 16× faster performance and up to 30× better AI energy efficiency than comparable M4- or M33-based devices. The SoC’s BLE 5.4 radio subsystem provides +14 dBm transmit power, while dual-mode capability supports low-power audio streaming and backward compatibility with Classic Bluetooth.

The Apollo510D Lite integrates 2 MB of RAM and 2 MB of nonvolatile memory with dedicated instruction/data caches for faster execution. It also includes secureSPOT 3.0 and Arm TrustZone to enable secure boot, firmware updates, and data protection across connected devices.

Along with the Apollo510D Lite (dual-mode Bluetooth), Ambiq’s lineup includes the Apollo510 Lite (no BLE radio) and the Apollo510B Lite (BLE-only). The Apollo510 Lite series is sampling now, with volume production expected in Q1 2026.

The post SoC delivers dual-mode Bluetooth for edge devices appeared first on EDN.

A push button activated door opener board

| Figured someone might enjoy this 🤷🏻♀️ [link] [comments] |

Uhh ohh there goes my amplifier

| Fo [link] [comments] |

Dual-range motion sensor simplifies IIoT system designs

STMicroelectronics debuts the tiny ISM6HG256X three-in-one motion sensor in a 2.5 × 3-mm package for data-hungry industrial IoT (IIoT) systems, while also supporting edge AI applications. The IMU sensor combines simultaneous low-g (±16 g) and high-g (±256 g) acceleration detection with a high-performance precision gyroscope for angular rate measurement, ensuring the detection from subtle motion or vibrations to severe shocks.

“By integrating an accelerometer with dual full-scale ranges, it eliminates the need for multiple sensors, simplifying system design and reducing overall complexity,” ST said.

The ISM6HG256X is suited for IIoT applications such as asset tracking, worker safety wearables, condition monitoring, robotics, factory automation, and black box event recording.

In addition, the embedded edge processing and self-configurability support real-time event detection and context-adaptive sensing, which are needed for asset tracking sensor nodes, wearable safety devices, continuous industrial equipment monitoring, and automated factory systems.

(Source: STMicroelectronics)

(Source: STMicroelectronics)

Key features of the MEMS motion sensor are the unique machine-learning core and finite state machine, together with adaptive self-configuration and sensor fusion low power (SFLP). In addition, thanks to the SFLP algorithm, 3D orientation tracking also is possible with a few µA of current consumption, according to ST.

These features are designed to bring edge AI directly into the sensor to autonomously classify detected events, which supports real-time, low-latency performance, and ultra-low system power consumption.

The ISM6HG256X is available now in a surface-mount package that can withstand harsh industrial environments from -40°C to 105°C. Pricing starts at $4.27 for orders of 1,000 pieces from the eSTore and through distributors. It is part of ST’s longevity program, ensuring long-term availability of critical components for at least 10 years.

Also available to help with development are the new X-NUCLEO-IKS5A1 industrial expansion board with MEMS Studio design environment and software libraries, X-CUBE-MEMS1. These tools help implement functions such as high-g and low-g fusion, sensor fusion, context awareness, asset tracking, and calibration.

The ISM6HG256X will be showcased in a dedicated STM32 Summit Tech Dive, “From data to insight: build intelligent, low-power IoT solutions with ST smart sensors and STM32,” on November 20.

The post Dual-range motion sensor simplifies IIoT system designs appeared first on EDN.

LIN motor driver improves EV AC applications

As precise control of cabin airflow and temperature becomes more critical in vehicles to enhance passenger comfort as well as to support advanced thermal management systems, Melexis introduces the MLX81350 LIN motor driver for air conditioning (AC) flaps and automated air vents in electric vehicles (EVs). The MLX81350 delivers a balanced combination of performance, system integration, and cost efficiency to meet these requirements.

The fourth-generation automotive LIN motor driver, built on high-voltage silicon-on-insulator technology, delivers up to 5 W (0.5 A) per motor and provides quiet and efficient motor operation for air conditioning flap motors and electronic air vents.

(Source: Melexis)

(Source: Melexis)

In addition to flash programmability, Melexis said the MLX81350 offers high robustness and function density while reducing bill-of-materials complexity. It integrates both analog and digital circuitry, providing a single-chip solution that is fully compliant with industry-standard LIN 2.x/SAE J2602 and ISO 17987-4 specifications for LIN slave nodes.

The MLX81350 features a new software architecture that enhances performance and efficiency over the previous generation. This enhancement includes improved stall detection and the addition of sensorless, closed-loop field-oriented control. This enables smoother motor operation, lower current consumption, and reduced acoustic noise to better support automotive HVAC and thermal management applications, Melexis said.

However, the MLX81350 still maintains pin-to-pin compatibility with its predecessors for easier migration with existing designs.

The LIN motor driver offers lots of peripherals to support advanced motor control and system integration, including a configurable RC clock (24-40 MHz), four general-purpose I/Os (digital and analog), one high-voltage input, 5× 16-bit motor PWM timers, two 16-bit general timers, and a 13-bit ADC with <1.2 -µs conversion time across multiple channels, as well as UART, SPI, and I²C master or slave interfaces. The LIN interface enables seamless communication within vehicle networks, and provides built-in protection and diagnostic features, including over-current, over-voltage, and temperature shutdown, to ensure safe and reliable operation in demanding automotive environments.

The MLX81350 is designed according to ASIL B (ISO 26262) and offers flexible wake-up options via LIN, external pins, or an internal wake-up timer. Other features include a low standby current consumption (25 µA typ.; 50 µA max.) and internal voltage regulators that allow direct powering from the 12-V battery, supporting an operating voltage range of 5.5 V to 28 V.

The MLX81350 is available now. The automotive LIN motor driver is offered in SO-8 EP and QFN-24 packages.

The post LIN motor driver improves EV AC applications appeared first on EDN.

OKW’s plastic enclosures add new custom features

OKW can now supply its plastic enclosures with bespoke internal metal brackets and mounting plates for displays and other large components. The company’s METCASE metal enclosures division designs and manufactures the custom aluminum parts in-house.

(Source: OKW Enclosures Inc.)

(Source: OKW Enclosures Inc.)

One recent project of this type involved OKW’s CARRYTEC handheld enclosures. Two brackets fitted to the lid allowed a display to be flush mounted; a self-adhesive label covered the join between screen and case. Another mounting plate, fitted in the base, was designed to support a power supply.

Custom brackets and supports can be configured to fit existing PCB pillars in OKW’s standard plastic enclosures. Electronic components can then be installed on the brackets’ standoffs.

CARRYTEC (IP 54 optional) is ideal for medical and laboratory electronics, test/measurement, communications, mobile terminals, data collection, energy management, sensors, Industry 4.0, machine building, construction, agriculture and forestry.

The enclosures feature a robust integrated handle with a soft padded insert. They can accommodate screens from 8.4″ to 13.4″. Interfaces are protected by inset areas on the underside. A 5 × AA battery compartment can also be fitted (machining is required).

These housings can be specified in off-white (RAL 9002) ABS (UL 94 HB) or UV-stable lava ASA+PC (UL 94 V-0) in sizes S 8.74″ × 8.07″ × 3.15″, M 10.63″ × 9.72″ × 1.65/3.58″ and L 13.70″ ×11.93″ × 4.61″.

In addition to the custom metal brackets and mounting plates, other customizing services include machining, lacquering, printing, laser marking, decor foils, RFI/EMI shielding, and installation and assembly of accessories.

For more information, view the OKW website: https://www.okwenclosures.com/en/news/blog/BLG2510-metal-brackets-for-plastic-enclosures.htm

The post OKW’s plastic enclosures add new custom features appeared first on EDN.

A current mirror reduces Early effect

It’s just a fact of life. A BJT wired in common emitter, even after compensating for the effects of device and temperature variations, still isn’t a perfect current source.

Wow the engineering world with your unique design: Design Ideas Submission Guide

One of the flaws in the ointment is the Early effect of collector voltage on collector current. It can sometimes be estimated from datasheet parameters if output admittance (hoe) is specified (Ee ~ hoe / test current). A representative value is 1% per volt. Figure 1 shows its mischief in action in the behavior of a simple current mirror, where:

I2 = I1(1 + Vcb/Va)

Va ~ 100v

Ierr = Vcb/Va ~ 1%/V

Figure 1 Current mirror without emitter degeneration.

Figure 1 Current mirror without emitter degeneration.

If the two transistors are matched, I2 should equal I1. But instead, Q2’s collector current may increase by 1% per Vcb volt. A double-digit Vcb may create a double-digit percentage error. That would make for a rather foggy “mirror”!

Fortunately, a simple trick for mitigating Early is well known to skilled practitioners of our art. (Please see the footnote). Emitter degeneration is based on an effect that’s 4000 times stronger than the effect of Vcb on Ic.

That’s the effect of Vbe on collector current, and it can easily reduce Ee by two orders of magnitude. Figure 2 shows how it works:

I2 ~ I1(1 + Vcb/Va) – (0.026R)(I2 – I1))

Ierr ~ (Vcb/Va)/(Vr/26mV + 1)

Figure 2 Current mirror with emitter degeneration

Equal resistors R added in series with both emitters will develop voltages Vr = I1*R and I2*R that will be equal if the currents are equal. But if the currents differ (e.g., because of Early), then a Vbe differential will appear…duh…

This is useful because the Vbe differential will oppose the initial current differential, and the effect is large, even if Vr is small. Figure 3 shows how dramatically this reduces Ierr.

Figure 3 A normalized Early effect (y-axis) versus emitter degeneration voltage Ve = Ia*R (x-axis). Note that just 50 mV reduces Early by 3:1. That’s indeed a “long way”!

Footnote

One DI has an earlier conversation about current mirrors and the Early effect: “A two-way mirror—current mirror that is.” In the grand tradition of editor Aalyia’s DI kitchen, frequent and expert commentator Ashutosh suggested how emitter degeneration could improve performance:

asa70

May 27, 2025

Regarding degen, i’ve found that a half volt at say 1mA FS helps match the in and out currents much better even at a tenth of the current, even for totally randomly selected transistors. I suppose it is because the curves will be closer at smaller currents, so that even a 50 mV drop goes a long way

Ashutosh certainly nailed it! 50mV does go a long (3:1) way!

Stephen Woodward’s relationship with EDN’s DI column goes back quite a long way. Over 100 submissions have been accepted since his first contribution back in 1974.

Related Content

- A two-way mirror—current mirror that is

- A two-way Wilson current mirror

- Use a current mirror to control a power supply

- A comparison between mirrors and Hall-effect current sensings

The post A current mirror reduces Early effect appeared first on EDN.

Ascent Solar and CisLunar team to bring longer-lasting power solutions to US space market

A portable 8085 programing kit

| My dad built this into a Snap-On tool case back in the 80s. I'm currently working on a PCB design so he can put together a new one. [link] [comments] |

Rohde & Schwarz Mobile Test Summit 2025 on the future of wireless communications

Rohde & Schwarz has announced that this year’s Mobile Test Summit will be an online, multi-session event catering to two major time zones. Wireless communications professionals are invited to register for individual sessions on the Rohde & Schwarz website. The sessions will cover a wide range of critical industry topics: AI and machine learning in mobile networks, non-terrestrial networks (NTN) for mobile devices, the transition from 5G to 6G and the next generation of Wi-Fi.

- The first topic, AI and machine learning, will cover how AI and ML are changing mobile networks.

- The second topic is NTN, and its sessions will cover how the evolving NTN landscape enhances the mobile user experience and provides true global coverage for IoT devices.

- The third topic addresses the transition from 5G to 6G, with a focus being on XR applications in the 6G age, new device types and the rise of private 5G NR networks. Special focus will be on the impact on test and measurement as the industry evolves from 5G to 6G.

- The fourth topic covers the latest advancements in Wi-Fi 8 technology and how they elevate the mobile user experience.

Alexander Pabst, Vice President of Wireless Communications at Rohde & Schwarz, says: “As we mark the fifth anniversary of hosting our popular Mobile Test Summit, we’re excited to continue this open forum for the global wireless community to exchange ideas, share experiences and debate the technical and operational questions that will shape the future of connectivity. The virtual, multi‑session format makes it easy for professionals in the wireless ecosystem around the globe to participate in focused conversations and obtain actionable insights that help shape the industry’s future.”

The post Rohde & Schwarz Mobile Test Summit 2025 on the future of wireless communications appeared first on ELE Times.

Sivers details strategic partnership with POET to deliver light engines for AI infrastructure

Infineon and SolarEdge collaborate to advance high-efficiency power infrastructure for AI data centres

Infineon and SolarEdge are partnering to advance the development of highly efficient next-generation Solid-State Transformer (SST) technology for AI and hyperscale data centres.

– The new SST is designed to enable direct medium-voltage to 800–1500V DC conversion with over 99% efficiency, reducing size, weight, and CO₂ footprint – The collaboration combines SolarEdge’s DC expertise with Infineon’s semiconductor innovation to support sustainable, scalable power infrastructure and further expansion into the AI data-centre market

Infineon Technologies AG and SolarEdge Technologies, Inc. announced a collaboration to advance SolarEdge’s Solid-State Transformer (SST) platform for next-generation AI and hyperscale data centres. The collaboration focuses on the joint design, optimization and validation of a modular 2-5 megawatt (MW) SST building block. It combines advanced silicon carbide (SiC) switching technology from Infineon with SolarEdge’s proven power-conversion and control topology set to deliver >99% efficiency, supporting the global shift towards high-efficiency, DC-based data centre infrastructure.

The Solid-State Transformer technology is well positioned to play a crucial role in future,

highly efficient 800 Volt direct current (VDC) AI data centre power architectures. The

technology enables end-to-end efficiency and offers several key advantages, including a

significant reduction of weight and size, a reduced CO₂ footprint, and accelerated

deployment of power distribution, among others, when connecting the public grid with data

centre power distribution. The SST under joint development will enable direct medium-

voltage (13.8–34.5 kV) to 800–1500 V DC conversion.

“Collaborations like this are key to enabling the next generation of 800 Volt DC data centre

power architectures and further driving decarbonization,” said Andreas Urschitz, Chief

Marketing Officer at Infineon. “With high-performance SiC technology from Infineon,

SolarEdge’s proven capabilities in power management and system optimization are

enhanced, creating a strong foundation for the efficient, scalable, and reliable infrastructure

demanded by AI-driven data centres.”

“The AI revolution is redefining power infrastructure,” said Shuki Nir, CEO of SolarEdge. “It

is essential that the data centre industry is equipped with solutions that deliver higher levels of efficiency and reliability. SolarEdge’s deep expertise in DC architecture uniquely positions us to lead this transformation. Collaborating with Infineon brings world-class semiconductor innovation to our efforts to build smarter, more efficient energy systems for the AI era.”

As AI infrastructure drives an unprecedented surge in global power demand, data centre

operators are seeking new ways to deliver more efficient, reliable, and sustainable power.

Building on more than 15 years of leadership in DC-coupled architecture and high-efficiency

power electronics, this development would enable SolarEdge to expand into the data-centre

market with solutions designed to optimize power distribution from the grid to the compute

rack. This optimization relies on the efficient conversion of power, a challenge that

semiconductor solutions from Infineon are addressing, enabling efficient power conversions

from grid to core (GPU). With a focus on delivering reliable and scalable power systems

based on all relevant semiconductor materials silicon (Si), silicon carbide and gallium nitride (GaN), Infineon is enabling reduced environmental footprint and lower operating costs for the AI data centre ecosystem.

The post Infineon and SolarEdge collaborate to advance high-efficiency power infrastructure for AI data centres appeared first on ELE Times.

Designing a thermometer with a 3-digit 7-segment indicator

Transforming a simple 10-kΩ NTC thermistor into a precise digital thermometer is a great example of mixed-signal design in action. Using a mixed-signal IC—AnalogPAK SLG47011—this design measures temperatures from 0.1°C to 99.9°C with impressive accuracy and efficiency.

SLG47011’s analog-to-digital converter (ADC) with programmable gain amplifier (PGA) captures precise voltage readings, while its memory table and width converter drive a 3-digit dynamic 7-segment display. Each digit lights up in rapid sequence, creating a stable indication for a user, a neat demonstration of efficient multiplexing.

Compact, flexible, and self-contained, this design shows how one device can seamlessly handle sensing, computation, and display control—no microcontroller required.

Operating principle

The circuit schematic of the thermometer with a 3-digit 7-segment indicator is shown in Figure 1.

Figure 1 The circuit schematic displays a thermometer with 3-digit 7-segment indicator. Source: Renesas

The VDIV = 1.8 V voltage is applied to PIN 7 through a resistive divider RT / (R + RT), where R = 5.6 kΩ. PIN 8 activates the first digit, while PIN 6 activates the second digit and decimal point. PIN 4 activates the third digit.

The signal from PIN 7 goes to the single-ended input of the PGA (buffer mode, mode #6) and then to ADC CH0 for further sampling. The allowable temperature range measured by the thermometer is 0.1°C to 99.9°C (or 273.25 K to 373.05 K).

The voltage (VIN) after the resistive divider is equal to:

The ADC converts this voltage to a 10-bit code using the formula:

Whereas,

- RT is the resistance of the NTC thermistor:

- R0 = 10,000 Ω is the resistance at ambient temperature T0 (25°C or 285.15 K)

- B = 4050 K is a constant of the thermistor

- VIN is the voltage on PIN 7

- 1024 represents the 10-bit resolution of the ADC (210)

- 1620 represents the internal Vref in mV

- VINdec is VIN in 10-bit decimal format

The maximum value of VINdec is 1023.

The NTC thermistor resistances for the minimum and maximum value of the temperature are calculated using equations below:

The maximum voltage after the resistive divider is ![]()

The minimum voltage after the resistive divider is ![]()

The relationship between the measured temperature and VIN for the applied parameters of the circuit is shown in Figure 2.

Figure 2 Graph shows the relationship between temperature and VIN.

Thermometer design

The GreenPAK IC-based thermometer design is shown in Figure 3. Download free Go Configure Software Hub to open the design file and see how the functionality is carried out.

Figure 3 Thermometer with 3-digit 7-segment indicator design is built around a mixed-signal IC. Source: Renesas

The SLG47011 mixed-signal IC contains a memory table macrocell that can hold 4096 12-bit words. This space is enough to store the values of each of the three indicator digits for each VINdec (1024 * 3 = 3072 values in total). In other words, the 3n word of the memory table corresponds to the first digit, the 3n + 1 to the second digit, and the 3n + 2 to the third digit of each corresponding T, where n = VINdec.

The ADC output value is sent to the MathCore macrocell, where it’s multiplied by three. This value is then used as a memory table address. Assuming that the ADC output is 1000, the MathCore output is 3000. This means that the memory table values at 3000, 3001, and 3002 addresses will be used and will correspond to the indicator’s first, second, and third digits accordingly.

Data from the MathCore output goes to the IN+ CH0 input of the multichannel DCMP macrocell. This data is compared with the data on the IN- CH0 input, which is taken from the Data Buffer0 output. Data Buffer0 stores the data from the CNT11/DLY11/FSM0 macrocell, which operates in Counter/FSM mode.

The Counter/FSM is reset to “1” when a HIGH signal from the ADC data-ready output arrives and starts counting upward. The multichannel DCMP OUT0 output is connected to the Keep input of CNT11/DLY11/FSM0. This means that when the CNT11/DLY11/FSM0 current value is equal to the MathCore output value, the DCMP OUT0 output is HIGH, and the Keep input of CNT11/DLY11/FSM0 is also HIGH, keeping the counted value for further addressing to the memory table.

At the same time, together with CNT11/DLY11/FSM0, the Memory Control Counter is counting upward from 0 and sets the memory table address.

Thus, when the ADC measures a certain voltage value, the previously described comparison operation will point to the corresponding voltage value stored in the memory table—three consecutively recorded digits, which are then dynamically displayed on the 7-segment display.

The memory table’s stored data then goes to the width converter macrocell, which converts the serial 12-bit input into a parallel 12-bit output (Table 1).

Table 1 The above data highlights width converter connections. Source: Renesas

The inverter enables the decimal point (DP) through PIN 16 based on state of 3-bit LUT0 (second digit).

To dynamically display the temperature, the digits will be ON sequentially with a period of 300 μs. The period is set by the CNT2/DLY2 macrocell (in Reset Counter Mode). The 3-bit LUT4 sets the clock of the width converter based on its synchronization with the CNT11/DLY11/FSM0 clock and the state of DCMP OUT0.

The P DLY, DFF8, and 3-bit LUT12 macrocells form a state counter for the Up/Down input of the Memory Control Counter macrocell based on the state of the second digit (falling edge on OUT2 of the width converter).

When the first digit is ON, the Memory Control Counter counts upward by 1; when the second digit is first set ON, the state counter is set to LOW, forcing the Memory Control Counter to count down, while it has already activated the third number. Therefore, the second number is activated again, and the state counter goes HIGH, forcing the Memory Control Counter count upward, while it has already activated the first digit. Thus, all three digits will be sequentially activated until there is a new measured value from the ADC macrocell.

CNT8/DLY8, CNT12/DLY12/FSM1, and 3-bit LUT7 are used to properly turn on the ADC after the first turn-on when POR arrives, as well as during further operation when the ADC is turned on and off. CNT12/DLY12/FSM1 provides a period of 1.68 s, which results in the thermometer value being updated every 1.68 s.

Memory table filling algorithm

The algorithm below is shown for a VDIV voltage of 1.8 V and a resistive divider of 5.6 kΩ and RT.

First, the resistance value of RT (Ω) at ambient temperature T is calculated using the formula:

Second, the value of the temperature t (°C) for a determined RT value is calculated by:

Then, the calculated t (°C) values are rounded to the first decimal point.

For each VINdec value, three values are assigned in the memory table as follows: each VINdec corresponds to three consecutive values in the memory table 3n, 3n + 1, and 3n + 2, where n = VINdec.

Three separate columns for each of the values of 3n, 3n + 1, and 3n + 2 should be created. They each correspond to the first, second, and third digits of the indicator, respectively. The first column is assigned to the first digit of the rounded t value. The second column is assigned to the second digit, and the third column is assigned to the third digit.

For each digit of each column, a 7-bit binary value is found (m11 – m5), corresponding to the activation of the corresponding digit of the 7-segment display (Table 2).

Table 2 The above data highlights the 7-segment code. Source: Renesas

When the measured tmeas temperature is in range 0.1°C > tmeas > 99.9°C, the 0 – L symbols should be displayed on the indicator. The third digit is not activated in this case.

The next step is to add 5 more bits (m4 – m0) to the right of this value to get a 12-bit number.

The ninth bit (m3) is responsible for turning on the first digit, the tenth bit (m2) is responsible for turning on the second digit, and the eleventh bit (m1) for the third digit. Since a 7-segment indicator with a common cathode is used, turning on the digit is done with a LOW level (0). Therefore, for the first column (with words of type 3n), the ninth bit (m3) will equal 0, while the tenth (m2) and the eleventh (m1) bits will equal 1.

For the second column (with words of type 3n + 1), the tenth bit (m2) will be equal to 0, while the ninth (m3) and eleventh (m1) bits will be equal to 1. For the third column (with words of type 3n + 2), the eleventh (m1) bit will be equal to 0, while the ninth (m3) and tenth (m2) bits will be equal to 1.

The twelfth bit (m0) is not used, so its value does not affect the design. The resulting 3072 binary 12-bit values must then be converted to hex.

The required values for the memory table are already determined, now they need to be sorted in ascending order of the Word index and inserted into the appropriate location in the software. For a better understanding of the connections between the memory table and the width converter, view Figure 4.

Figure 4 The above diagram highlights connections between the memory table and the width converter. Source: Renesas

Test results

Figure 5 shows the result of measuring a temperature of around 17°C with respect to data obtained by a multimeter thermocouple.

Figure 5 Temperature range is set up to room temperature of around 17°C. Source: Renesas

Figure 6 shows the result of measuring a temperature of around 59°C with respect to data obtained by a multimeter thermocouple.

Figure 6 The measurement results show a temperature of around 59°C. Source: Renesas

Figure 7 shows the result of measuring a temperature of around 70°C with respect to data obtained by multimeter thermocouple.

Figure 7 The measurement results show a temperature of around 70°C. Source: Renesas

The mixed-signal integration

This design illustrates a practical approach to implementing a compact digital thermometer using the SLG47011 mixed-signal chip. Its ADC with PGA enables precise indirect temperature measurement, while the memory table and width converter manage dynamic control of the 3-digit 7-segment indicator.

By adjusting the resistive divider and updating the memory table, engineers can easily redefine the measurement range to suit different applications. The result is a straightforward and flexible thermometer design that effectively demonstrates mixed-signal integration in practice.

Myron Rudysh is application engineer at Renesas Electronics.

Nazar Ftomyn is application engineer at Renesas Electronics.

Yaroslav Chornodolskyi is application engineer at Renesas Electronics.

Bohdan Kholod is senior product development engineer at Renesas Electronics.

Related Content

- Thermometers perform calibration checks

- Thermal Imaging Sensors for Fever Detection

- Electronic Thermometer Project by LM35 and LM3914

- Measure temperature precisely with an infrared thermometer

- Electronic Thermometer with CrowPanel Pico 2.8 Inch 320×240 TFT LCD

The post Designing a thermometer with a 3-digit 7-segment indicator appeared first on EDN.