Feed aggregator

Budget 2026-27: Can New PLI Schemes Drive India’s A&D Tech Sovereignty?

As the Union Budget approaches, the spotlight intensifies on India’s aerospace and defence technology sector, a vertical that has transitioned from a heavy importer to a nascent global manufacturing hub. The numbers tell a story of aggressive scaling: under the aegis of “Atmanirbhar Bharat,” domestic defence production surged to a historic ₹1.27 lakh crore in FY 2023-24.

However, for an industry eyeing a $5 trillion economy, this record high is viewed not as a finish line, but as a baseline. The shift toward indigenous manufacturing has fundamentally rewired the nation’s military-industrial complex, replacing foreign dependency with homegrown R&D and high-tech sovereignty. As the government prepares to lay out its fiscal roadmap, the industry is looking for more than just procurement orders; it is looking for deep-tech incentives, streamlined export pathways, and sustained capital outlay.

This budget will be a litmus test for India’s self-reliance commitment. Stakeholders are bracing for announcements that could further catalyse the aerospace ecosystem, ensuring that “Made in India” weaponry and avionics don’t just meet internal security needs but become a cornerstone of India’s global economic footprint.

The Tech-Sovereignty Mandate

As the lines between commercial innovation and battlefield superiority blur, technology has emerged as the definitive fulcrum for India’s tri-service modernisation. Industry experts argue that the upcoming Budget presents a pivotal window to institutionalise this convergence through aggressive structural reforms.

Central to this discourse is the evolution of the Production Linked Incentive (PLI) Scheme. While the current framework has provided a vital tailwind for the drone industry, there is a growing consensus that a “narrow-lens” approach is no longer sufficient. To truly insulate India’s supply chain from global volatility, the PLI umbrella must expand to cover the high-stakes world of dual-use technologies.

In terms of using technology in aerospace and defence technology development, the use of AI and related features will play a significant role.

“Investing in digital twins and simulation technology for testing and research in aviation and defence can boost precision and efficiency in the electronic manufacturing industry. Tecknotrove urges the government to prioritize use of digital twin technology in this financial budget. It’s a strategic move that will amplify innovation, save research and development and manufacturing costs, and drive India’s self-reliance in manufacturing. Digital twins aren’t just a trend—they’re a game-changer. With decades of expertise in digital twins for aviation and defence, we have seen this technology helping in at least 30% reduction in costs,” says Payal Gupta, Co-Founder, Director-Business Development, Tecknotrove Systems India Pvt. Ltd.

The strategic roadmap for the FY 2026-27 fiscal cycle should ideally prioritise:

- The Full Drone Spectrum: Moving beyond basic assembly to incentivise the manufacturing of high-endurance propulsion systems and autonomous flight controllers.

- Electronic Warfare & Surveillance: Bringing Airborne Early Warning (AEW) systems, jamming devices, and advanced radar arrays under the incentive net to neutralise import dependencies.

- The Robotics Frontier: Providing fiscal stimulus for indigenous sensors and robotic systems that will define the future of unmanned combat and deep-space communication.

By widening these incentive corridors, the government can transform the “Make in India” initiative from a manufacturing slogan into a high-tech powerhouse, ensuring that the next generation of aerospace sensors and AI-driven robotics are conceived, designed, and built on Indian soil.

By: Shreya Bansal, Sub-Editor

The post Budget 2026-27: Can New PLI Schemes Drive India’s A&D Tech Sovereignty? appeared first on ELE Times.

How to Build a Hacker-Proof Car: Insights from the Auto EV Tech Summit

Speaking at the Auto EV Tech Vision Summit 2025, Suresh D highlights the major cyber vulnerabilities and the corresponding technologies required to enable a safer and more resilient automotive ecosystem.

Since the electronic components in passenger vehicles are set to increase by 20-40 percent, as the recent studies suggest, including infotainment, ADAS, etc, drawing in a lot of sensors in the near future, automobiles are emerging as the new battlefield for cyber developments. Underlining this growing phenomenon, Suresh D, Group CTO, Minda Corporation, CEO, Spark Minda Tech Centre & Board Member, Spark Minda Green Mobility says, “A passenger vehicle is expected to see a 20–40 percent increase—nearly doubling in some cases—over the next two to three years, bringing in a large number of on-board electronic systems. This will significantly increase software content and complexity,” at the Auto EV Tech Vision Summit 2025 held at KTPO, Bengaluru, on November 18–19, 2025.

He further goes on to add that the phenomenon will make Operating Systems and other software indispensable, escalating the security question in automobiles.

Critical Challenges on the way

He says that the new architectural parameter of SDVs, where the distributed architecture is being replaced by controlled or zonal architecture, also poses certain security challenges. Also, as the new vehicles remain entirely connected, as in V-2-V or V-2-I connection, the proximity of cyber risks escalates.

Further, he touches upon the critical challenges that are to be tackled, including phishing, hacking, snooping, malware, etc. He goes on to underline some of the crucial cyberattacks that the automotive industry has seen in the recent past, ranging from CAN spoofing a Jeep Cherokee in 2014 to the latest TESLAMATE attack on Tesla cars in 2025, underlining how the question of cybersecurity becomes more relevant than ever.

Curious Case of SDVs & EVs

As EVs are on the rise across the world, Suresh D highlights how EV expansion and the need for robust charging systems also aggravate the risk. He explains that if a charging station compromises a supplier’s build server, it can be manipulated to tamper with BMS parameters via a compromised internal bus or a malicious charging station.

While for SDVs, potential risk sources he underlines include attack scenarios ranging from unprivileged root access and pivoting through fleet management backends, to compromised third-party apps and poorly protected cryptographic keys.

How to Tackle this?

In the latter part, he touches upon the important steps that can be taken to avoid the potential risks and create a safer and reliable cyber ecosystem for automotives. First among them is the System Architecture approach. He says, “It refers to developing a robust architecture—understanding the OEM’s architecture and aligning the product accordingly.” He sums it up as thinking way ahead of the OEMs. It also includes encryption and decryption of the hardware to ensure that no vulnerability remains open to exploitation.

Further, he also outlines a distinct approach, which is Embedded Edge Solutions, which means solving the problem at the source. It includes several protections, including secure flashing and secure boot. This is done through the plant server of the OEM that generates distinct private keys for each of the units for further authorization.

For SDVs, he highlights a telematics-based approach which consists of 3 layers, namely Layer 1- In-vehicle security, Layer 2- Vehicle Communication Security & Layer 3- The cloud infrastructure. When Internet Protocol is used for communication, it enables whitelisting of the IPs through encryption and decryption through SSL, enabling a better and safer environment.

High Frequency Options: Granting More Immunity

He also underlines how automobiles these days usually come with smart keys or keyless access to the vehicle. While the technology is referred to as Low-Frequency Radio Frequency (LFRF), it is immune to relay attacks. However, the industry is gradually moving towards safer and more reliable options like Bluetooth and Ultra Wide Bandgap (UWB), with high-frequency technology making decoding highly difficult.

He adds that even these technologies are prone to cyberattacks, either at the server level or the device level. Conclusively, some techniques like channel sounding with Bluetooth-based technology have been developed, which are more precise and help make authentication more secure. It offers a turnkey secure foundation, making automobiles reliable and secure.

The post How to Build a Hacker-Proof Car: Insights from the Auto EV Tech Summit appeared first on ELE Times.

Palo Alto Networks Unifies Observability and Security for the AI Era through Chronosphere Acquisition

As enterprises increasingly rely on AI to run digital operations, protect assets, and drive growth, success depends on one critical factor: trusted, high-quality, real-time data. Palo Alto Networks, the global cybersecurity leader, announced the completion of its acquisition of Chronosphere, addressing a core challenge of the AI era: the inability to see and secure the massive data volumes running modern businesses.

Chronosphere, a Leader in the 2025 Gartner Magic Quadrant for Observability Platforms, was purpose-built to handle this scale. While legacy tools break down in cloud-native environments, Chronosphere gives customers deep visibility across their entire digital estate. With this acquisition, Palo Alto Networks is redefining how organisations run at the speed of AI—by enabling customers to gain deep, real-time visibility into their applications, infrastructure, and AI systems — while maintaining strict control over data cost and value.

The planned integration of Palo Alto Networks Cortex AgentiX with Chronosphere’s cloud-native observability platform will allow customers to apply AI agents that can now find and fix security and IT issues automatically—before they impact the customer or the bottom line. AI security without deep observability is blind; this acquisition delivers the essential context across models, prompts, users, and performance to move from manual guessing to autonomous remediation.

Nikesh Arora, Chairman and CEO, Palo Alto Networks:

“Enterprises today are looking for fewer vendors, deeper partnerships, and platforms they can rely on for mission-critical security and operations. Chronosphere accelerates our vision to be the indispensable platform for securing and operating the cloud and AI. We believe that great security starts with deep visibility into all your data, and Chronosphere provides that foundation for our customers.”

Martin Mao, Co-founder and CEO, Chronosphere, is joining Palo Alto Networks as SVP, GM Observability and comments:

“Chronosphere was built to help the world’s most complex digital organisations operate at scale with confidence. Joining Palo Alto Networks allows us to bring AI-era observability to a global audience. Together, we’re delivering a new standard — where observability, security, and AI come together to give organisations control over their most valuable asset: data.”

The Chronosphere Telemetry Pipeline remains available as a standalone solution, enabling organisations to eliminate the ‘data tax’ associated with modern security operations. By acting as an intelligent control layer, the pipeline filters low-value noise to reduce data volumes by 30% or more while requiring 20x less infrastructure than legacy alternatives. This is key to Palo Alto Networks Cortex XSIAM strategy, ensuring customers can scale their security posture—not their spending—as they transition to autonomous, AI-driven operations.

The post Palo Alto Networks Unifies Observability and Security for the AI Era through Chronosphere Acquisition appeared first on ELE Times.

EEVblog 1732 - 20yo 1000+ Cycle Panasonic Li-Ion Battery TESTED

Учений КПІ Юрій Яворський — лауреат премії Верховної Ради України

Доцент кафедри фізичного матеріалознавства та термічної обробки (ФМТО) Інституту матеріалознавства та зварювання ім. Є. О. Патона (ІМЗ) Юрій Яворський отримав Премію Верховної Ради України молодим ученим — одну з найпрестижніших державних відзнак для молодих науковців.

КПІ та КНДІСЕ посилюють співпрацю у сфері судових експертиз

КПІ ім. Ігоря Сікорського та Київський науково-дослідний інститут судових експертиз (КНДІСЕ) провели робочу зустріч, щоб посилити партнерство та вивести наукову й освітню співпрацю на новий стратегічний рівень.

Wolfspeed unveils TOLT package portfolio

NEC develops high-efficiency compact power amplifier module for sub-6GHz band in 5G base-station radio units

Vishay launches 1200V SiC MOSFET power modules in SOT-227 packages

Successive approximation

Analog-to-digital conversion methods abound, but we are going to take a look at a particular approach as shown in Figure 1.

Figure 1 An analog-to-digital converter where an analog input signal is compared to a voltage reference that has been scaled via a resistive ladder network. (Source: John Dunn)

Figure 1 An analog-to-digital converter where an analog input signal is compared to a voltage reference that has been scaled via a resistive ladder network. (Source: John Dunn)

In this approach, in very simplified language, an analog input signal is compared to a voltage reference that has been scaled via a resistive ladder network. Scaling is adjusted by finding that digital word for which a scaled version of Vref becomes equal to the analog input. The number of bits in the digital word can be chosen pretty much arbitrarily, but sixteen bits is not unusual. However, for illustrative purposes, we will illustrate the use of only seven bits.

Referring to a couple of examples as seen in Figure 2, the process runs something like this.

Figure 2 Two digital word acquisition examples using successive approximation. (Source: John Dunn)

For descriptive purposes, let the analog input be called our “target”. We first set the most significant bit (the MSB) of our digital word to 1 and all of the lower bits to 0. We compare the scaled Vref to the target to see if we have equality. If the scaled Vref is lower than the target, we leave the MSB at 1, or if the scaled Vref is greater than the target, we return the MSB to 0. If the two are equal, we have completion.

In either case, if we do not have completion, we then set the next lower bit to 1, and again we compare the scaled Vref to the target to see if we have equality. If the scaled Vref is lower than the target, we leave this second bit at 1, or if the scaled Vref is greater than the target, we return this second bit back to 0. If the two are equal, we have completion.

Again, in either case, if we do not have completion, we then set the next lower bit to 1, and again we compare the scaled Vref to the target to see if we have equality. If the scaled Vref is lower than the target, we leave this third bit at 1, or if the scaled Vref is greater than the target, we return this third bit to 0. If the two are equal, we have completion.

Sorry for the monotony, but that is the process. We repeat this process until we achieve equality, which can take as many steps as there are bits, and therein lies the beauty of this method.

We will achieve equality in no more steps than there are bits. For the seven-bit examples shown here, the maximum number of steps to completion will be seven. Of course, it’s not that we actually have seven-bit converters offered by any company, but the number “seven” simply allows viewable examples to be drawn below. Fewer bits might not make things clear, while more bits could have us squinting at the page with a magnifying glass.

If we did a simple counting process starting from all zeros, the maximum number of steps could be as high as 27+1 or one-hundred-twenty-eight, which could/would be really slow.

Slow, straight-out counting would be a “tracking” process, which is sometimes used and which does have its own virtues. However, we can speed things up with what is called “successive approximation”.

Please note that the “1”, the “-1”, and the “0” highlighted in blue are merely indicators of which value is greater than, less than, or equal to the other.

A verbal description of this process for the target value of 101 may help shed some light. We then proceed as follows. (Yes, this is going to be verbose, but please trace it through.)

We first set the most significant bit with its weight value of 64 to a logic 1 and discover that the numerical value of the bit pattern is just that, the value 64. When we compare this to our target number of 101, we find that we’re too low. We will leave that bit where it is and move on.

We set the next lower significant bit with its weight value of 32 to a logic 1 and discover that the sum yielding the numerical value is now 64 + 32 = 96. When we compare this to our target number of 101, we find that we’re still too low. We will leave the pair of bits where they are and move on.

We set the next lower bit again with its weight value of 16 to a logic 1 and discover that the sum yielding the numerical value is now 64 + 32 + 16 = 112. When we compare this to our target number of 101, we find that we are now too high. We will leave the first two most significant bits where they are, but we will return the third most significant bit to logic 0 and move on.

We set the next lower bit again with its weight value of 8 to a logic 1 and discover that the sum yielding the numerical value is now 64 + 32 + 0 + 8 = 104. When we compare this to our target number of 101, we find that we are now again too high. We will leave the first three most significant bits where they are, but we will return the fourth most significant bit to logic 0 and move on.

We set the next lower bit again with its weight value of 4 to a logic 1 and discover that the sum yielding the numerical value is now 64 + 32 + 0 + 0 + 4 = 100. When we compare this to our target number of 101, we find that we’re once again too low. We will leave the quintet of bits where they are and move on.

We set the next lower bit again with its weight value of 2 to a logic 1 and discover that the sum yielding the numerical value is now 64 + 32 + 0 + 0 + 4 + 2 = 102. When we compare this to our target number of 101, we find that we are now once again too high. We will leave the first five most significant bits where they are, but we will return the sixth most significant bit to logic 0 and move on.

We set the lowest bit with its weight value of 1 to a logic 1 and discover that the sum yielding the numerical value is now 101, there is no error. We have completed our conversion in only seven counting steps, which is far and away, way less than the number of steps that would have been required in a simple, direct counting scheme.

It may be helpful to look at a larger number of digital word acquisition examples, as in Figure 3.

Figure 3 Digital word acquisitions with number paths. (Source: John Dunn)

Remember the old movie “Seven Brides for Seven Brothers”? For these examples, think “Seven Steps for Seven Bits”.

John Dunn is an electronics consultant and a graduate of The Polytechnic Institute of Brooklyn (BSEE) and of New York University (MSEE).

Related Content

- ADCs for High Dynamic Range: Successive-Approximation or Sigma-Delta?

- ADC Basics, Part 3: Using Successive-Approximation Register ADC in Designs

- Challenges & Requirements: Voltage Reference Design for Precision Successive-Approximation ADCs, Part 4

- “Golden Gloves” A/D Converter Match: Successive-approximation register vs. sigma-delta topology

The post Successive approximation appeared first on EDN.

Apple CarPlay and Google Android Auto: Usage impressions and manufacturer tensions

What happens to manufacturers when your ability to differentiate whose vehicle you’re currently traveling in, far from piloting, disappears?

My wife’s 2018 Land Rover Discovery:

not only now has upgraded LED headlights courtesy of yours truly, I also persuaded the dealer a while ago to gratis-activate the vehicle’s previously latent Apple CarPlay and Google Android Audio facilities for us (gratis in conjunction with a fairly pricey maintenance bill, mind you…). I recently finally got around to trying them both out, and the concept’s pretty cool, with the implementation a close second. Here’s what CarPlay’s UI looks like, courtesy of Wikipedia’s topic entry:

And here’s the competitive Android Auto counterpart:

As you can see, this is more than just a simple mirroring of the default smartphone user interface; after the mobile device and vehicle successfully activate a bidirectional handshake, the phone switches into an alternative UI that’s more vehicle (specifically: mindful of driver-distraction potential) amenable, and tailored for its larger albeit potentially lower overall resolution dashboard-integrated display.

The baseline support for both protocols in our particular vehicle is wired, which means that you plug the phone into one of the USB-A ports located within the storage console located between the front seats. My wife’s legacy iPhone is still Lightning-based, so I’ve snagged both a set of inexpensive ($4.99 for three) coiled Lightning-to-USB-A cords for her:

and a similarly (albeit not quite as impressively) penny-pinching ($6.67 for two) suite of USB-C-to-USB-A coiled cords for my Google Pixel phones:

The wired approach is convenient because a single cord handles both communication-with-vehicle and phone charging tasks. That said, a lengthy strand of wire, even coiled, spanning the gap from the console to the magnetic mount located at the dashboard vent:

is aesthetically and otherwise unappealing, especially considering that the mount at the phone end also already redundantly supports both MagSafe (iPhone) and Qi (Pixel, in conjunction with a magnet-augmented case) charging functions:

Therefore, I’ve also pressed into service a couple of inexpensive (~$10 each, sourced from Amazon’s Warehouse-now-Resale section) wireless adapters that mimic the integrated wireless facilities of newer model-year vehicles and even comprehend both the CarPlay and Android Auto protocols. One comes from a retailer called VCARLINKPLAY:

The other is from the “PakWizz Store”:

The approach here is somewhat more complicated. The phone first pairs with the adapter, already plugged into and powered by the car’s USB-A port, over Bluetooth. The adapter then switches both itself and the phone to a common and (understandably, given the aggregate data payload now involved) beefier 5 GHz Wi-Fi Direct link.

Particularly considering the interference potential from other ISM band (both 2.4 GHz for Bluetooth and 5 GHz for Wi-Fi) occupants contending for the same scarce spectrum, I’m pleasantly surprised at how reliable everything is, although initial setup admittedly wasn’t tailored for the masses and even caused techie-me to twitch a bit.

Encroaching on vehicle manufacturers’ turfAs such, I’ve been especially curious to follow recent news trends regarding both CarPlay and Android Auto. Rivian and Tesla, for example, have long resisted adding support for either protocol to their vehicles, although rumors persist that both companies are continuing to develop support internally for potential rollout in the future.

Automotive manufacturers’ broader embrace (public at least) for next-generation CarPlay Ultra has to date been muted at best. And GM is actively phasing out both CarPlay and Android Auto from new vehicle models, in favor of an internally developed entertainment software-and-display stack alternative.

What’s going on? Consider this direct quote from Apple’s May 2025 CarPlay Ultra press release:

CarPlay Ultra builds on the capabilities of CarPlay and provides the ultimate in-car experience by deeply integrating with the vehicle to deliver the best of iPhone and the best of the car. It provides information for all of the driver’s screens, including real-time content and gauges in the instrument cluster.

Granted, Apple has noted that in developing CarPlay Ultra, it’s “reflecting the automaker’s look and feel” (along with “offering drivers a customizable experience”). But given that all Apple showed last May was an Aston Martin logo next to its own:

I’d argue that Apple’s “partnership” claims are dubious, and maybe even specious. And per comments from Ford’s CEO Jim Farley in a recent interview, he seems to agree (the full interview is excellent and well worth a read):

Are you going to allow OEMs to control the vehicles? How far do you want the Apple brand to go? Do you want the Apple brand to start the car? Do you want the Apple brand to limit the speed? Do you want the Apple brand to limit access?

The bottom line, as I see it, is that Apple can pontificate all it wants that:

CarPlay Ultra allows automakers to express their distinct design philosophy with the look and feel their customers expect. Custom themes are crafted in close collaboration between Apple and the automaker’s design team, resulting in experiences that feel tailor-made for each vehicle.

But automakers like Ford and GM are obviously (and understandably so, IMHO) worried that with Apple and Google already taking over key aspects of the visual, touch (and audible; don’t forget about the Siri and Google Assistant-now-Gemini voice) interfaces, not to mention their even more aggressive aspirations (along with historical behavior in other markets as a guide to future behavior here), the manufacturer, brand and model uniqueness currently experienced by vehicle occupants will evaporate in response.

More to comeI’ll be curious to see (and cover) how this situation continues to develop. For now, I welcome your thoughts in the comments on what I’ve shared so far in this post. And FYI, I’ve also got two single-protocol wireless adapter candidates sitting in my teardown pile awaiting attention: a CarPlay-only unit from the “Luckymore Store”:

And an Android Auto-only unit, the v1 AAWireless, which I’d bought several years back in its original Indiegogo crowdfunding form:

Stay tuned for those, as well!

—Brian Dipert is the Principal at Sierra Media and a former technical editor at EDN Magazine, where he still regularly contributes as a freelancer.

Related Content

The post Apple CarPlay and Google Android Auto: Usage impressions and manufacturer tensions appeared first on EDN.

Is this low-inductance power-device package the real deal?

While semiconductor die get so much of the attention due to their ever-shrinking feature size and ever-increasing substrate size, the ability to effectively package them and thus use them in a circuit is also critical. For this reason, considerable effort is devoted to developing and perfecting practical, technically advanced, thermally suitable cost-effective packages for components ranging from switching power devices to multi-gigahertz RF devices.

Regardless of frequency, package parasitic inductance is a detrimental issue, as it slows down slewing needed for switching crispness of digital devices and responsiveness of analog ones (of course, reality is that digital switching performance is still constrained by analog principles.).

Now, a researcher team at the US Department of Energy’s National Renewable Energy Laboratory (NREL; recently renamed as the National Laboratory of the Rockies) has developed a silicon-carbide half-bridge module that uses organic direct-bonded copper in a novel layout design to enable a high degree of magnetic-flux cancellation, Figure 1.

Figure 1 (left) 3D CAD drawing of new half-bridge inverter module; (right) Early prototype of polyimide-based half-bridge module. Source: NREL

Figure 1 (left) 3D CAD drawing of new half-bridge inverter module; (right) Early prototype of polyimide-based half-bridge module. Source: NREL

Their Ultra-Low Inductance Smart (ULIS) package is a 1200 V, 400 A half bridge silicon carbide (SiC) power module that can be pushed beyond 200-kHz switching frequency at maximum power. The low-cost ULIS also allows the converter to become easier to manufacture, addressing issues related to both bulkiness and costs.

Preliminary results show that it has approximately seven to nine times lower loop inductances and higher switching speeds at similar voltages/current levels, and five times the energy density of earlier designs — while occupying a smaller footprint, Figure 2.

Figure 2 The complete ULIS package is very different than conventional packages and offers far lower loop inductance compared to exiting approaches. Source: NREL

In addition to being powerful and lightweight, the module continuously tracks its own condition and can anticipate component failures before they happen.

In traditional designs, the power modules conduct electricity and dissipate excess heat by bonding copper sheets directly to a ceramic base—an effective, but rigid, solution. ULIS bonds copper to a flexible Dupont Temprion polymer create a thinner, lighter, more configurable design.

Unlike typical power modules which assemble semiconductor devices inside a brick-like package, ULIS winds its circuits around a flat, octagonal design, Figure 3. The disk-like shape allows more devices to be housed in a smaller area, making the overall package smaller and lighter.

Figure 3 This “exploded” drawing of the complete half-bridge power module shows the arrangement of the electrical and structural elements. Source: NREL

At the same time, its novel current routing allows for maximum cancellation of magnetic flux, contributing to the power module’s clean, low-loss electrical output, meaning ultrahigh efficiency.

While conventional power modules rely on bulky and inflexible materials, ULIS takes a new approach. Traditional designs call for power modules to conduct electricity and dissipate excess heat by bonding copper sheets directly to a ceramic base—an effective but rigid solution. ULIS bonds copper to the flexible, electrically insulating Temprion to create a thinner and lighter module.

The stacked module layout greatly improves energy density and reduces parasitic inductance (based on simulation data). Typical half-bridge module inductance is 2.2 to 5.5 nanohenries, compared to 20 to 25 nH for existing designs. Further, reliability is enhanced as the compliance of Temprion reduces the strain caused by the differences in the coefficient of thermal expansion (CTE) between mated materials.

Since the material bonds easily to copper using just pressure and heat, and because its parts can be machined using widely available equipment, the team maintains that the ULIS can be fabricated quickly and inexpensively, with manifesting costs in the hundreds of dollars rather than thousands, Figure 4.

Figure 4 The ULIS can be machined using widely available equipment, thus significantly reducing the manufacturing costs for the power module. Source: NREL

Another innovation allows the ULIS to function wirelessly as an isolated unit that can be controlled and monitored without external cables. A patent is pending for this low-latency wireless communication protocol.

The ULIS design is a good example of the challenges and dead-end paths that innovation can take on its path to a successful conclusion. According to the team’s report, one of the original layouts looked like a flower with a semiconductor at the tip of each petal. Another idea was to create a hollow cylinder with components wired to the inside.

Every idea the team came up with was either too expensive or too difficult to fabricate—until they stopped thinking in three dimensions and flattened the design into nearly two dimensions, which made it possible to build the module balancing complexity with cost and performance.

The details of the work are in their readable and detailed IEEE APEC paper “Organic Direct Bonded Copper-Based Rapid Prototyping for Silicon Carbide Power Module Packaging” but it is behind a paywall. However, there is a nice “poster” summary of their work posted at the NLR site here.

I wonder is this innovation will catch on and be adopted, but I certainly don’t know. What I do know is that some innovations are slow to catch on, and many do not because of real-world problems related to scaling up, volume production unforeseen technical issues, testability…it’s a long list of what can get in the way.

If you don’t think so, just look at batteries: every month, we see news of dramatic advances that will supposedly revolutionize their performance, yet these breakthroughs don’t seem to get traction. Sometimes it is due to technical or implementation problems, but often it is because the actual improvement they provide does not outweigh the disruption they create in getting there.

Bill Schweber is an EE who has written three textbooks, hundreds of technical articles, opinion columns, and product features.

Related content

- Stop blaming the supply for your dissipation woes

- GaN gets game

- New Horizons spacecraft’s power issues make yours look trivial

- Paralleling supplies: good, bad, or ugly?

The post Is this low-inductance power-device package the real deal? appeared first on EDN.

Top 10 edge AI chips

As edge devices become increasingly AI-enabled, more and more chips are emerging to fill every application niche. At the extremes, applications such as speech recognition can be done in always-on power envelopes, while tens of watts will be enough for even larger generative AI models today.

Here, in no particular order, are 10 of EDN’s selections for a range of edge AI applications. These devices range from those capable of handling multimodal large language models (LLMs) in edge devices to those designed for vision processing and minimizing power consumption for always-on applications.

Multiple camera streamsFor vision applications, Ambarella Inc.’s latest release is the CV7 edge AI vision system-on-chip (SoC) for processing multiple high-quality camera streams simultaneously via convolutional neural networks (CNNs) or transformer networks. The CV7 features the latest generation of Ambarella’s proprietary AI accelerator, plus an in-house image-signal processor (ISP), which uses both traditional ISP algorithms and AI-driven features. This family also includes quad Arm Cortex-A73 cores, hardware video codecs on-chip, and a new, 64-bit DRAM interface.

Ambarella is targeting this family for AI-based 8K consumer products such as action cameras, multicamera security systems, robotics and drones, industrial automation, and video conferencing. It will also be suitable for automotive applications such as telematics and advanced driver-assistance systems.

Ambarella’s CV7 vision SoC (Source: Ambarella Inc.)

Fallback CPU

Ambarella’s CV7 vision SoC (Source: Ambarella Inc.)

Fallback CPU

The MLSoC Modalix from SiMa Technologies Inc. is now available in production quantities, along with its LLiMa software framework for deployment of LLMs and generative AI models on Modalix. Modalix is SiMa’s second-generation architecture, which comes as a family of SoCs designed to host full applications.

Modalix chips have eight Arm A-class CPU cores on-chip alongside the accelerator, important for running application-level code, but also allows programs to fall back on the CPU just in case a particular math operation isn’t supported by the accelerator. Also on the SoC are an on-chip ISP and digital-signal processor (DSP). Modalix will come in 25-, 50-, 100-, and 200-TOPS (INT8) versions. The 50-TOPS version will be first to market and can run Llama2-7B at more than 10 tokens per second, with a power envelope of 8–10 W.

Open-source NPUSynaptics Inc.’s Astra series of AI-enabled IoT SoCs range from application processors to microcontroller (MCU)-level parts. This family is purpose-built for the IoT.

The SL2610 family of multimodal edge AI processors is for applications between smart appliances, retail point-of-sale terminals, and drones. All parts in the family have two Arm Cortex-A55 cores, and some have a neural processing unit (NPU) subsystem. The Coral NPU included was developed at Google—it’s an open-source RISC-V CPU with scalar instructions—sitting alongside Synaptics’ homegrown AI accelerator, the T1, which offers 1-TOPS (INT8) performance for transformers and CNNs.

Synaptics’ SL2610 multimodal edge AI processors (Source: Synaptics Inc.)

Raspberry Pi compatibility

Synaptics’ SL2610 multimodal edge AI processors (Source: Synaptics Inc.)

Raspberry Pi compatibility

The Hailo-10H edge AI accelerator from Hailo Technologies Ltd. is gaining a large developer base, as it is available in a form factor that plugs into hobbyist platform Raspberry Pi. However, the Hailo-10H is also used by HP in add-on cards for its point-of-sale systems, and it’s also automotive-qualified.

The 10H is the same silicon as the Hailo-10 but runs at a lower power-performance point: The 10H can run 2B-parameter LLMs in about 2.5 W. The architecture of this AI co-processor is based on Hailo’s second-generation architecture, which has improved support for transformer architectures and more flexible number representation. Multiple models can be inferenced concurrently.

Hailo’s Hailo-10H edge AI accelerator (Source: Hailo Technologies Ltd.)

Analog acceleration

Hailo’s Hailo-10H edge AI accelerator (Source: Hailo Technologies Ltd.)

Analog acceleration

Startup EnCharge AI announced its first product, the EN100. This chip is a 200-TOPS (INT8) accelerator targeted squarely at the AI PC, achieving an impressive 40 TOPS/W. The device is based on EnCharge’s capacitance-based analog compute-in-memory technology, which the company says is less temperature-sensitive than resistance-based schemes. The accelerator’s output is a voltage (not a current), meaning transimpedance amplifiers aren’t needed, saving power.

Alongside the analog accelerator on-chip are some digital cores that can be used if higher precision is required, or floating-point maths. The EN100 will be available on a single-chip M.2 card with 32-GB LPDDR, with a power envelope of 8.25 W. A four-chip, half-height, half-length PCIe card offers up to 1 TOPS (INT8) in a 40-W power envelope, with 128-GB LPDDR memory.

Encharge AI’s EN100 M.2 card (Source: Encharge AI)

SNNs

Encharge AI’s EN100 M.2 card (Source: Encharge AI)

SNNs

For microwatt applications, Innatera Nanosystems B.V. has developed an AI-equipped MCU that can run inference at very, very low power. The Pulsar neuromorphic MCU targets always-on sensor applications: It consumes 600 µW for radar-based presence detection and 400 µW for audio scene classification, for example.

The neural processor uses Innatera’s spiking neural network (SNN) accelerators—there are both analog and digital spiking accelerators on-chip, which can be used for different types of applications and workloads. Innatera says its software stack, Talamo, means developers don’t have to be SNN experts to use the device. Talamo interfaces directly with PyTorch and a PyTorch-based simulator and can enable power consumption estimations at any stage of development.

Innatera’s Pulsar spiking neural processor (Source: Innatera Nanosystems B.V.)

Generative AI

Innatera’s Pulsar spiking neural processor (Source: Innatera Nanosystems B.V.)

Generative AI

Axelera AI’s second-generation chip, Europa, can support both multi-user generative AI and computer vision applications in endpoint devices or edge servers. This eight-core chip can deliver 629 TOPS (INT8). The accelerator has large vector engines for AI computation alongside two clusters of eight RISC-V CPU cores for pre- and post-processing of data. There is also an H.264/H.265 decoder on-chip, meaning the host CPU can be kept free for application-level software. Given the importance of ensuring compute cores are fed quickly with data from memory, the Europa AI processor unit provides 128 MB of L2 SRAM and a 256-bit LPDDR5 interface.

Axelera’s Voyager software development kit covers both Europa and the company’s first-generation chip, Metis, reserved for more classical CNNs and vision tasks. Europa is available both as a chip or on a PCIe card. The cards are intended for edge server applications in which processing multiple 4K video streams is needed.

Butter wouldn’t meltMost members of the DX-M1 series from South Korean chip company DeepX Co. Ltd. provide 25-TOPS (INT8) performance in the 2- to 5-W power envelope (the exception being the DX-M1M-L, offering 13 TOPS). One of the company’s most memorable demos involves placing a blob of butter directly on its chip while running inference to show that it doesn’t get hot enough for the butter to melt.

Delivering 25 TOPS in this co-processor chip is plenty for vision tasks such as pose estimation or facial recognition in drones, robots, or other camera systems. Under development, the DX-M2 will run generative AI workloads at the edge. Part of the company’s secret sauce is in its quantization scheme, which can run INT8-quantized networks with accuracy comparable to the FP32 original. DeepX sells chips, modules/cards, and small, multichip systems based on its technology for different edge applications.

Voice interfaceThe latest ultra-low-power edge AI accelerator from Syntiant Corp., the NDP250, offers 5× the tensor throughput versus its processor. This device is designed for computer vision, speech recognition, and sensor data processing. It can run on as little as microwatts, but for full, always-on vision processing, the consumption is closer to tens of milliwatts.

As with other parts in Syntiant’s range, the devices use the company’s AI accelerator core (30 GOPS [INT8]) alongside an Arm Cortex-M0 MCU core and an on-chip Tensilica HiFi 3 DSP. On-chip memory can store up to 6-million-bit parameters. The NDP250’s DSP supports floating-point maths for the first time in the Syntiant range. The company suggests that the ability to run both automatic speech recognition and text-to-speech models will lend the NDP250 to voice interfaces in particular.

Multiple power modesNvidia Corp.’s Jetson Orin Nano is designed for AI in all kinds of edge devices, targeting robotics in particular. It’s an Ampere-generation GPU module with either 8 GB or 4 GB of LPDDR5. The 8-GB version can do 33 TOPS (dense INT8) or 17 TFLOPS (FP16). It has three power modes: 7-W, 15-W, and a new, 25-W mode, which boosts memory bandwidth to 102 GB/s (from 65 GB/s for the 15-W mode) by increasing GPU, memory, and CPU clocks. The module’s CPU has six Arm Cortex-A78AE 64-bit cores. Jetson Orin Nano will be a good fit for multimodal and generative AI at the edge, including vision transformer and various small language models (in general, those with <7 billion parameters).

Nvidia’s Jetson Orin Nano (Source: Nvidia Corporation)

Nvidia’s Jetson Orin Nano (Source: Nvidia Corporation)

The post Top 10 edge AI chips appeared first on EDN.

Spectral Engineering and Control Architectures Powering Human-Centric LED Lighting

As technological advancements continue to pursue personalisation & customisation at every level, illumination has also transformed from a need to a customisation. Consequently, the LED industry is moving towards a similar yet prominent stride, making customised and occasion-specific solutions, keeping in consideration the human behaviour and lighting changes across the day. Long seen as the constant and uniform thing, illumination is now being reimagined as something dynamic and customisable.

In the same pursuit, the industry has moved towards enabling Human-Centric Lighting(HCL), where lighting is designed and engineered to emulate natural daylight, ranging from dimming them as the Sun goes down, while brightening up as the day begins. Gradually, illumination is now being designed around human biology, visual comfort, and cognitive performance rather than simple brightness or energy efficiency.

But what lies behind this marvel is hardcore engineering. Technically, the result is made possible by the marvels of spectral engineering & control architectures, wherein the former adjusts the light spectrum while the latter enables the intelligence directing the timing changes of the lighting system. Simultaneously, the dual play brings forth today’s human-centric lighting into real-life examples and is also making them more customised and personalised. This ultimately helps in supporting human circadian rhythms, enhancing well-being, mood, and performance.

To enable these engineered outcomes, embedded sensors, digital drivers, and networked control platforms are integrated into the modern-day LED lights, transforming illumination into a responsive, data-driven infrastructure layer. In combination, spectral engineering and intelligent control systems are reshaping the capabilities of LED lighting, transforming it from a passive utility into a dynamic, precision-engineered tool for enhancing human wellbeing, productivity, and performance.

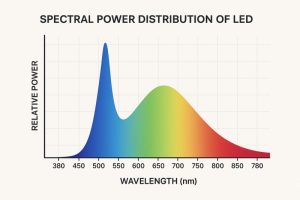

How is Spectral Power Distribution engineered?

When we talk about LED lights, white light is the first thing that comes to our minds. Although the same is not true scientifically. Surprisingly, LEDs inherently emit blue light and not white. To turn the blue light into white, a Phosphor coating is applied over it. Consequently, the blue light mixes with the phosphor to turn some of the light into green, red & yellow simultaneously. These lights eventually mix to turn white.

Spectral Power Distribution (SPD) is simply the profile of the white colour which is not visible to our naked eyes, and how much of each colour is present in the visible white light. The final light can be controlled by various means, such as the type of phosphor, how thick the phosphor layer is, or by adding extra coloured LEDs (like red or cyan).

Spectral Power Distribution is engineered by carefully mixing different colours of light inside an LED, even though it looks white, so that the light feels right for the human body and mind.

Engineering the Spectral Power Distribution of White LEDs

Often, it is seen that the very same white light is sometimes harsh while sometimes soft- all this is because of various variables. Today, from being a static character, SPD has turned into a tunable design parameter,++ becoming a Controllable Design Variable. To this effect, SPD is largely controlled by Phosphor composition (which colours it emits), Particle size and density, and finally Layer thickness and distribution.

That’s why the same 400K LEDs from different manufacturers can feel completely different — their SPDs are different, even if the Correlated Color Temperature (CCT) is the same. But as long as the final color is decided by some application made during manufacturing, the effect remains static. While spectral Power distribution is essential, it is equally important to dictate the given behaviour as per the time of the day.

Multi-Channel LED Configurations for Spectral Tunability

To enable a real-time nature to this Spectral tunability, engineers today use multiple LED channels, including:

- White + Red

- White + Cyan

- RGBW / RGBA

- Tunable white (warm white + cool white)

By precisely varying the current supplied to each LED channel, the spectral power distribution can be reshaped in real time, allowing the system to shift between blue-enriched and blue-reduced lighting modes as required. This level of control allows you to adjust the perceived colour temperature independently of the light’s biological impact, rather than having them locked together. As a result, SPD is no longer a fixed characteristic of the light source but becomes a dynamic, real-time controllable design parameter.

Melanopic Response, Circadian Metrics, and Spectral Weighting

When we talk about light, visibility & brightness make up the primary issue, but that has changed drastically with the emergence of Human Centric Lighting (HCL). With HCL coming into play, photopic lux, the quantification of brightness, is no longer a go-to metric to decide upon the quality of lighting. It is because it explained only one part of the coin, which is visibility, and not how this light or visibility affects human biology.

At the same time, Human Centered Lighting focuses on how light affects the circadian system, alertness, sleep–wake cycles, mood, and hormonal regulation. This phenomenon has brought up new metrics that tell us not only about the brightness or visibility, but also how it biologically acts. One such metric is Melanopic Lux, which weights the spectrum based on melanopsin sensitivity. Melanopsin is a photopigment in our eyes, usually sensitive to Blue-Cyan light.

Interestingly, more melanopic stimulation → increased alertness and circadian activation, while less melanopic stimulation → relaxation and readiness for sleep. That’s where we come to the core of our subject – Light induced behaviuour. The emergence of Melanopic Lux allows engineers to decouple visual brightness from biological effect, giving the right direction to Human Centric Lighting.

While melanopic metrics define what kind of biological response light should produce, control architectures determine when and how that response is delivered. Translating circadian intent into real-world lighting behaviour requires intelligent control systems capable of dynamically adjusting spectrum, intensity, and timing throughout the day. This is where embedded sensors, digital LED drivers, and networked control platforms come into play, enabling lighting systems to modulate melanopic content in real time—boosting circadian stimulation during the day and reducing it in the evening—without compromising visual comfort or energy efficiency.

Other metrics, such as Melanopic Equivalent Daylight Illuminance (EDI) and Circadian Stimulus (CS) are used to quantify how effectively a light source supports circadian activation or melatonin suppression, beyond what photopic lux can describe.

LED Drivers and Power Electronics for Dynamic Spectral Control

In human-centric lighting systems, LED drivers are no longer simple power supplies but precision control elements that translate circadian intent into real-world illumination. Because LEDs are current-driven devices, accurate current regulation is essential to maintain stable brightness and spectral output, especially as temperature and operating conditions change.

Dynamic spectral tuning typically relies on multi-channel LED architectures, making channel balancing a critical requirement. Each LED colour behaves differently electrically and thermally, and without independent, well-balanced current control, the intended spectral profile can drift over time, affecting both visual quality and biological impact.

Equally important is dimming accuracy. Human-centric lighting demands smooth, flicker-free dimming that preserves spectral integrity at all brightness levels, particularly during low-light, evening scenarios. Advanced driver designs enable fine-grained dimming and seamless transitions, allowing lighting systems to dynamically adjust spectrum and intensity throughout the day while maintaining visual comfort and circadian alignment.

System Integration Challenges and Design Trade-Offs

While human-centric lighting promises precise control over both visual and biological responses, delivering this in real-world systems involves significant integration challenges and design trade-offs. Spectral accuracy, electrical efficiency, thermal management, and system cost must all be balanced within tight form-factor and reliability constraints. Multi-channel LED engines increase optical and control complexity, while higher channel counts demand more sophisticated drivers, sensing, and calibration strategies.

Thermal effects further complicate integration, as LED junction temperature directly influences efficiency, colour stability, and lifetime. Without careful thermal design and feedback control, even well-engineered spectral profiles can drift over time. At the same time, adding sensors, networking, and intelligence introduces latency, interoperability, and cybersecurity considerations that must be addressed at the system level.

Ultimately, successful human-centric lighting solutions are defined not by any single component, but by holistic co-design—where optics, power electronics, controls, and circadian metrics are engineered together. The trade-offs made at each layer determine whether a system merely adjusts colour temperature or truly delivers biologically meaningful, reliable, and scalable lighting performance.

The post Spectral Engineering and Control Architectures Powering Human-Centric LED Lighting appeared first on ELE Times.

Dell Technologies Enables NxtGen to Build India’s Largest AI Factory

Story Highlights

Dell AI Factory with NVIDIA to provide scalable and secure infrastructure for NxtGen’s AI platform, India’s first and largest AI factory, enabling national-scale AI development.

This milestone deployment accelerates India’s AI mission, enabling large‑scale generative, agentic, and physical AI while expanding NxtGen’s high‑performance AI services nationwide.

Dell Technologies today announced that NxtGen AI Pvt Ltd, one of India’s foremost sovereign cloud and AI infrastructure providers, has selected Dell AI Factory with NVIDIA solutions for building India’s first and largest dedicated AI factory. This milestone deployment will significantly expand India’s national AI capability, enabling large-scale generative AI, agentic AI, physical AI, and high-performance computing across enterprises, start-ups, and government programs.

Dell will provide the core infrastructure, including Vertiv liquid-cooled Dell PowerEdge XE9685L servers, delivered through Dell Integrated Rack Scalable Systems, for NxtGen’s new AI cluster, empowering the company to meet the growing demand for AI as a Service and large-scale GPU capacity.

Why it matters

This accelerated computing infrastructure is vital for advancing India’s AI mission, significantly expanding NxtGen’s AI cloud services for a diverse range of clients, from start-ups to academia and government. By empowering NxtGen with this advanced foundation, Dell is accelerating India’s next wave of AI development and innovation, ensuring critical access to high-performance AI capabilities across the region.

Powering the future of AI with advanced Dell AI infrastructure

The Dell AI Factory with NVIDIA combines AI infrastructure, software, and services in an advanced, full-stack platform designed to meet the most demanding AI workloads and deliver scalable, reliable performance for training and inference. Leveraging the Dell AI Factory with NVIDIA, NxtGen will deploy Vertiv liquid-cooled, fully integrated Dell IR5000 racks featuring Dell PowerEdge XE9685L servers with the NVIDIA accelerated computing platform to build a cluster with over 4,000 NVIDIA Blackwell GPUs, NVIDIA BlueField-3 DPUs, and NVIDIA Spectrum-X Ethernet networking, all purpose-built for AI. These will be complemented by Dell PowerEdge R670 servers and Dell PowerScale F710 storage.

Dell AI Factory with NVIDIA: Empowering AI for Human Progress

The Dell AI Factory with NVIDIA offers a full stack of AI solutions from data center to edge, enabling organizations to rapidly adopt and scale AI deployments. The integration of Dell’s AI capabilities with NVIDIA’s accelerated computing, networking, and software technologies provides customers with an extensive AI portfolio and an open ecosystem of technology partners. With more than 3,000 customers globally, the Dell AI Factory with NVIDIA reflects Dell’s leadership in enabling enterprises with scalable, secure and high-performance AI infrastructure.

The comprehensive Dell AI Factory with NVIDIA portfolio provides a simplified and reliable foundation for NxtGen to deliver advanced AI capabilities at speed and scale. This allows NxtGen to deliver on its core mission of providing sovereign, cost-effective and powerful AI services that help businesses grow and innovate, while at the same time reinforcing Dell’s commitment to providing the technology that drives human progress.

By equipping organizations like NxtGen with cutting-edge AI infrastructure and services, Dell is helping to unlock new possibilities and create a future where technology empowers everyone to achieve more.

Perspectives

“India’s rapid AI growth demands strong, reliable, and future-ready infrastructure,” said Manish Gupta, president and managing director, India, Dell Technologies. “Dell Technologies is addressing this need through the Dell AI Factory with NVIDIA, designed to simplify and scale AI deployments across industries. As the top AI infrastructure provider, we are enabling this shift by combining storage, compute, networking and software to accelerate AI adoption. Our collaboration with NxtGen brings these capabilities closer to Indian enterprises, helping them deploy AI efficiently and cost-effectively. This marks another step in our commitment to empowering India’s digital future through secure, scalable, and sovereign AI infrastructure.”

“NxtGen is committed to building India’s AI backbone,” said A. S. Rajgopal, managing director and chief executive officer, NxtGen. “This deployment marks a significant milestone for the country: India’s largest AI model-training cluster, built and operated entirely within India’s sovereign cloud framework. Dell Technologies has been critical in enabling this scale, performance, and reliability. Together, we are unlocking the infrastructure that will power the next generation of Indian AI models and applications.”

“India’s ambitious AI mission requires a foundation of secure, high-performance accelerated computing infrastructure to enable model and AI application development,” said Vishal Dhupar, managing director, Asia South, NVIDIA. “Dell’s integration of NVIDIA AI software and infrastructure, including NVIDIA Blackwell GPUs and NVIDIA Spectrum-X networking, provides the AI factory resources to help NxtGen accelerate this critical national capability.”

The post Dell Technologies Enables NxtGen to Build India’s Largest AI Factory appeared first on ELE Times.

Quest Global Appoints Richard Bergman as Global Business Head of its Semiconductor Division

Bengaluru, India, January 28th, 2026 – Quest Global, the world’s largest independent pure-play engineering services company, today announced the appointment of Richard (Rick) Bergman as President & Global Business Head of its Semiconductor vertical.

As the Global Business Head, Rick will focus on shaping the division’s long-term strategy, accelerating revenue growth, and deepening relationships with global customers. His responsibilities include defining a multi-year growth roadmap, supporting clients’ success through high-impact and transformational solutions, especially in AI, automotive, and industrial sectors, and fostering a culture of innovation and operational excellence to meet next-generation engineering demands.

“The semiconductor industry is at a turning point, fueled by AI, system innovation, and shifting supply chains,” says Ajit Prabhu, Co-Founder and CEO, Quest Global. “Rick is a fantastic addition to our team. He brings incredible leadership across semiconductors and computing, plus a real talent for scaling organizations and building genuine, long-term relationships with customers. Bringing him on board is a clear sign of our commitment to growing this vertical and making sure Quest Global remains a humble, trusted partner for engineering and transformation in this space.”

“Semiconductors are the foundational enablers of innovation across AI, high-performance computing, automotive, communications, and industrial systems,” said Rick Bergman, President & Global Business Head – Semiconductor, Quest Global. “What attracted me to Quest Global is the company’s unique combination of deep engineering DNA, global scale, and a long-term partnership mindset with customers. As the industry navigates increasing complexity, my focus will be on helping customers solve their most critical engineering challenges while building a scalable, high-impact business.”

Rick brings more than two decades of leadership experience across semiconductors, computing, graphics, and advanced technology platforms. Most recently, he served as President and CEO of Kymeta Corporation. Previously, he held senior leadership roles at AMD, Synaptics, and ATI Technologies. Throughout his career, Rick has led multi-billion-dollar businesses, overseen major acquisitions, and built high-performing global teams.

This appointment underscores Quest Global’s commitment to building category-leading leadership and scaling its Semiconductor business, aligned with evolving customer needs.

About Quest Global

At Quest Global, it’s not just what we do but how and why we do it that makes us different. We’re in the business of engineering, but what we’re really creating is a brighter future. For over 25 years, we’ve been solving the world’s most complex engineering problems. Operating in over 18 countries, with over 93 global delivery centers, our 21,500+ curious minds embrace the power of doing things differently to make the impossible possible. Using a multi-dimensional approach, combining technology, industry expertise, and diverse talents, we tackle critical challenges faster and more effectively. And we do it across the Aerospace & Defense, Automotive, Energy, Hi-Tech, MedTech & Healthcare, Rail and Semiconductor industries. For world-class end-to-end engineering solutions, we are your trusted partner.

The post Quest Global Appoints Richard Bergman as Global Business Head of its Semiconductor Division appeared first on ELE Times.

VIS licenses TSMC’s 650V and 80V GaN technology

Round pegs, square holes: Why GPGPUs are an architectural mismatch for modern LLMs

The saying “round pegs do not fit square holes” persists because it captures a deep engineering reality: inefficiency most often arises not from flawed components, but from misalignment between a system’s assumptions and the problem it is asked to solve. A square hole is not poorly made; it’s simply optimized for square pegs.

Modern large language models (LLMs) now find themselves in exactly this situation. Although they are overwhelmingly executed on general-purpose graphics processing units (GPGPUs), these processors were never shaped around the needs of enormous inference-based matrix multiplications.

GPUs dominate not because they are a perfect match, but because they were already available, massively parallel, and economically scalable when deep learning began to grow, especially for training AI models.

What follows is not an indictment of GPUs, but a careful explanation of why they are extraordinarily effective when the workload is rather dynamic and unpredictable, such as graphic processing, and disappointedly inefficient when the workload is essentially regular and predictable, such as AI/LLM inference execution.

The inefficiencies that emerge are not accidental; they are structural, predictable, and increasingly expensive as models continue to evolve.

Execution geometry and the meaning of “square”

When a GPU renders a graphic scene, it deals with a workload that is considerably irregular at the macro level, but rather regular at the micro level. A graphic scene changes in real time with significant variations in content—changes in triangles and illumination—but in an image, there is usually a lot of local regularity.

One frame displays a simple brick wall, the next, an explosion creating thousands of tiny triangles and complex lighting changes. To handle this, the GPU architecture relies on a single-instruction multiple threads (SIMT) or wave/warp-based approach where all threads in a “wave” or “warp,” usually between 16 and 128, receive the same instruction at once.

This works rather efficiently for graphics because, while the whole scene is a mess, local patches of pixels are usually doing the same thing. This allows the GPU to be a “micro-manager,” constantly and dynamically scheduling these tiny waves to react to the scene’s chaos.

However, when applied to AI and LLMs, the workload changes entirely. AI processing is built on tensor math and matrix multiplication, which is fundamentally regular and predictable. Unlike a highly dynamic game scene, matrix math is just an immense but steady flow of numbers. Because AI is so consistent, the GPU’s fancy, high-speed micro-management becomes unnecessary. In this context, that hardware is just “overhead,” consuming power and space for a flexibility that the AI doesn’t actually use.

This leaves the GPGPU in a bit of a paradox: it’s simultaneously too dynamic and not dynamic enough. It’s too dynamic because it wastes energy on micro-level programming and complex scheduling that a steady AI workload doesn’t require. Yet it’s not dynamic enough because it is bound by the rigid size of its “waves.”

If the AI math doesn’t perfectly fit into a warp of 32, the GPU must use “padding,” effectively leaving seats empty on the bus. While the GPU is a perfect match for solving irregular graphics problems, it’s an imperfect fit for the sheer, repetitive scale of modern tensor processing.

Wasted area as a physical quantity

This inefficiency can be understood geometrically. A circle inscribed in a square leaves about 21% of the square’s area unused. In processing hardware terms, the “area” corresponds to execution lanes, cycles, bandwidth, and joules. Any portion of these resources that performs work that does not advance the model’s output is wasted area.

The utilization gap (MFU)

The primary way to quantify this inefficiency is through Model FLOPs Utilization (MFU). This metric measures how much of the chip’s theoretical peak math power is actually being used for the model’s calculations versus how much is wasted on overhead, data movement, or idling.

For an LLM like GPT-4 running on GPGPT-based accelerators operating in interactive mode, the MFU drops by an order of magnitude with the hardware busy with “bookkeeping,” which encompasses moving data between memory levels, managing thread synchronization, or waiting for the next “wave” of instructions to be decoded.

The energy cost of flexibility

The inefficiency is even more visible in power consumption. A significant portion of that energy is spent powering the “dynamic micromanagement,” namely, the logic gates that handle warp scheduling, branch prediction, and instruction fetching for irregular tasks.

The “padding” penalty

Finally, there is the “padding” inefficiency. Because a GPGPU-based accelerator operates in fixed wave sizes (typically 32 or 64 threads), if the specific calculation doesn’t perfectly align with those multiples, often happening in the “Attention” mechanism of the LLM model, the GPGPU still burns the power for a full wave while some threads sit idle.

These effects multiply rather than add. A GPU may be promoted with a high throughput, but once deployed, may deliver only a fraction of its peak useful throughput for LLM inference, while drawing close to peak power.

The memory wall and idle compute

Even if compute utilization was perfect, LLM inference would still collide with the memory wall, the growing disparity between how fast processors can compute and how fast they can access memory. LLM inference has low arithmetic intensity, meaning that relatively few floating-point operations are performed per byte of data fetched. Much of the execution time is spent reading and writing the key-value (KV) cache.

GPUs attempt to hide memory latency using massive concurrency. Each streaming multiprocessor (SM) holds many warps and switches between them while others wait for memory. This strategy works well when memory accesses are staggered and independent. In LLM inference, however, many warps stall simultaneously while waiting for similar memory accesses.

As a result, SMs spend large fractions of idle time, not because they lack instructions, but because data cannot arrive fast enough. Measurements commonly show that 50–70% of cycles during inference are lost to memory stalls. Importantly, the power draw does not scale down proportionally since clocks continue toggling and control logic remains active, resulting in poor energy efficiency.

Predictable stride assumptions and the cost of generality

To maximize bandwidth, GPUs rely on predictable stride assumptions; that is, the expectation that memory accesses follow regular patterns. This enables techniques such as cache line coalescing and memory swizzling, a remapping of addresses designed to avoid bank conflicts and improve locality.

LLM memory access patterns violate these assumptions. Accesses into the KV cache depend on token position, sequence length, and request interleaving across users. The result is reduced cache effectiveness and increased pressure on address-generation logic. The hardware expends additional cycles and energy rearranging data that cannot be reused.

This is often described as a “generality tax.”

Why GPUs still dominate

Given these inefficiencies, it’s natural to ask why GPUs remain dominant. The answer lies in history rather than optimality. Early deep learning workloads were dominated by dense linear algebra, which mapped reasonably well onto GPU hardware. Training budgets were large enough that inefficiency could be absorbed.

Inference changes priorities. Latency, cost per token, and energy efficiency now matter more than peak throughput. At this stage, structural inefficiencies are no longer abstract; they directly translate into operational cost.

From adapting models to aligning hardware

For years, the industry focused on adapting models to hardware such as larger batches, heavier padding, and more aggressive quantization. These techniques smooth the mismatch but do not remove it.

A growing alternative is architectural alignment: building hardware whose execution model matches the structure of LLMs themselves. Such designs schedule work around tokens rather than warps, and memory systems are optimized for KV locality instead of predictable strides. By eliminating unused execution lanes entirely, these systems reclaim the wasted area rather than hiding it.

The inefficiencies seen in modern AI data centers—idle compute, memory stalls, padding overhead, and excess power draw—are not signs of poor engineering. They are the inevitable result of forcing a smooth, temporal workload into a rigid, geometric execution model.

GPUs remain masterfully engineered square holes. LLMs remain inherently round pegs. As AI becomes a key ingredient in global infrastructure, the cost of this mismatch becomes the problem itself. The next phase of AI computing will belong not to those who shave the peg more cleverly, but to those who reshape the hole to match the true geometry of the workload.

Lauro Rizzatti is a business advisor to VSORA, a technology company offering silicon semiconductor solutions that redefine performance. He is a noted chip design verification consultant and industry expert on hardware emulation.

Special Section: AI Design

- The AI design world in 2026: What you need to know

- AI workloads demand smarter SoC interconnect design

- AI’s insatiable appetite for memory

- The AI-tuned DRAM solutions for edge AI workloads

- Designing edge AI for industrial applications

The post Round pegs, square holes: Why GPGPUs are an architectural mismatch for modern LLMs appeared first on EDN.

📰 Газета "Київський політехнік" № 3-4 за 2026 (.pdf)

Вийшов 3-4 номер газети "Київський політехнік" за 2026 рік

Def-Tech CON 2026: India’s Biggest Conference on Advanced Aerospace, Defence and Space Technologies to Take Place in Bengaluru.

The two-day international technology conference is focused on promoting innovation in the Aerospace, Defence, and Space sectors, in conjunction with DEF-TECH Bharat 2026, held in Bengaluru.

With a strong India-centric focus, DefTech CON 2026 features high-impact keynote sessions, expert panels, technology showcases, and interactive QA sessions, covering areas such as AI & autonomous systems, cyber defence, unmanned systems, advanced materials, space tech, next-generation battlefield solutions, advanced sensors, secure communication networks, AI-driven command and control, electronic warfare systems, autonomous platforms, space-based surveillance, next-generation missile defence, and more. These technologies enable faster decision-making, enhanced interoperability, and greater operational dominance across land, air, sea, cyber, and space.

Designed as a venue for engineers, researchers, defence laboratories, industry leaders, startups, and system integrators, the conference unites India’s most brilliant minds to investigate emerging trends, groundbreaking solutions, and essential capabilities that are influencing the strategic future of the nation.

Click here to visit the website for more details!

The post Def-Tech CON 2026: India’s Biggest Conference on Advanced Aerospace, Defence and Space Technologies to Take Place in Bengaluru. appeared first on ELE Times.