Feed aggregator

TDK Boosts DC Voltage of SMT Gate Driver Transformers

Пам'яті Поповича Олексія Валерійовича

На війні загинув випускник нашого університету Попович Олексій Валерійович (17.07.1982 – 30.08.2025)...

Олексій закінчив університет 2006 року за спеціальністю «Адміністративний менеджмент» (на той час Факультет соціології).

Take Our 2025 EETech Engineering Insights Survey

My 3$ VFD (Vacuum fluorescent display) driver

| I bought this display from Alibaba, and then created PCB with JLCPCB. Refresh rate 60Hz with STM32. [link] [comments] |

An e-mail delivery problem, Part 2

For decades, I have used my IEEE alias address for both incoming and outgoing emails with no difficulties; however, this is no longer the case. The IEEE alias address is no longer workable for outgoing e-mails that are destined for any “gmail.com” recipient.

If I put ambertec@ieee.org in the “From” line of such an outgoing message, I get an immediate message rejection reply that looks like this:

If the content of the “From” line does not match the actual sending address, rejection occurs. In this case, the intended recipient was my own cell phone, but this kind of message comes my way when trying to send any email to any Gmail.com user.

I have neither the time nor the energy to wade into the bureaucratic techno-drivel of the “DMARC policy” or of the “DMARC initiative.” I simply cite my own experience as a signal that you and other IEEE members who read this will know that you are not alone.

John Dunn is an electronics consultant and a graduate of The Polytechnic Institute of Brooklyn (BSEE) and of New York University (MSEE).

Related Content

- An e-mail delivery problem

- What it means to be an IEEE HKN member

- The IEEE Code of Ethics

- Why do problems come in pairs?

- The First Spam Email: History & Fun Facts

The post An e-mail delivery problem, Part 2 appeared first on EDN.

Nichia launches µPLS Mini and DominoPLS at ISAL 2025

Lumileds’ LUXEON HL1Z Color Line simplifies multi-color LED application development with chip-scale packaging and uniform focal length

CSA Catapult appoints Caroline O’Brien as CEO

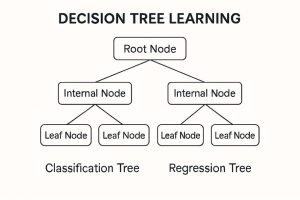

Decision Tree Learning Architecture Definition, Types and Diagram

Decision Tree Learning’s architecture is a tree-like, hierarchical structure employed in both classification and regression in supervised machine learning. It starts with a root node, which is the complete dataset and the starting point of the first split according to a chosen feature. From there, the tree splits into internal decision nodes, where each of them is a test on an attribute, and branches, which represent the results of those tests. The algorithm repeats recursively, splitting the data into subsets until reaching leaf nodes, where the terminal output is represented as either a class label or a numeric value.

Such an architecture is constructed based on algorithms such as CART (Classification and Regression Trees), which select the optimal splits based on evaluation of criteria such as Gini impurity or entropy. The aim is to produce a model imitating human decision-making by posing a series of questions that progressively give more particular conclusions. The ease of interpretability and simplicity of this organization make decision trees widely used in predictive analytics and data mining.

Types of Decision Tree Learning:

- Classification Tree

A Classification Tree is created to solve problems where the output variable is a category, i.e., it is a member of a particular class or category. The tree divides the data based on feature values that can best distinguish the categories. For each node, the algorithm selects the feature that gives the maximum information gain or decreases Gini impurity most. This goes on until the data has been separated into pure subsets, or leaf nodes, which are the final class prediction. For instance, it can distinguish between emails and non-spams.

- Regression Tree

A Regression Tree is employed when the target variable is continuous, i.e., it has numerical values. Rather than dividing data into categories, it estimates a numeric value by averaging the values in each leaf node. The tree splits data according to features that reduce the variance or mean squared error in the target variable. Each split is designed to produce subsets as homogeneous as possible based on the numerical output. For example: Predicting house prices, forecasting sales.

Decision Tree Learning Diagram:

The figure shows the decision tree learning architecture, a supervised learning machine model that applies to both classification and regression learning. At the apex is the root node, which symbolizes the entire data set and makes the first decision based on a chosen feature. It divides into internal nodes, each symbolizing a point of decision which further divides the data along specific feature values. These internal nodes subsequently branch out to leaf nodes that give the terminal output either a class label for a classification tree or a numerical value for a regression tree. The left half of the diagram illustrates a classification tree where the decisions end up in discrete categories, and the right half illustrates a regression tree where the outputs are continuous values. The framework is binary and symmetrical, highlighting the way data recursively splits in order to make a predictive judgment. The graphical framework serves to demystify how decision trees work through the gradual elimination of possibilities based on feature divisions.

Conclusion:

Decision trees are not only model they’re reasoning frameworks. Their readability, interpretableness, and flexibility make them a starting point for data science, particularly when understanding and actionable results are paramount. From classifying emails to forecasting real estate values, decision trees provide a step-by-step, logical process to comprehend the data.

The post Decision Tree Learning Architecture Definition, Types and Diagram appeared first on ELE Times.

Custom hardware helps deliver safety and security for electric traction

Electric traction has become a critical part of a growing number of systems that need efficient motion and position control. Motors do not just provide the driving force for vehicles, from e-bikes to cars to industrial and agricultural machinery. They also enable a new generation of robots, whether they use wheels, propellers or legs for motion.

The other common thread for many of these systems lies in the way they are expected to operate in a highly connected environment. For instance, wireless connectivity has enabled novel business models for e-bike rental and delivers positioning and other vital data to robots as they move around.

But the same connections to the Internet open avenues of attack in ways that previous generations of motion-control systems have not had to deal with. It complicates the tasks of designing, certifying, and maintaining systems that ensure safe operation.

To guarantee the actuators do not cause injury, designers must implement safeguards for their control systems to prevent them being bypassed and creating unsafe situations. They also need to ensure that corruption by hackers does not disrupt the system’s behavior. Security, therefore, now plays a major role in the design of the motor-control subsystems.

Figure 1 Connectivity in warehouse robots also opens vulnerabilities in motor control systems. Source: EnSilica

Algorithmic demands drive architectural change

Complexity in the motor control also arises from the novel algorithms that designers are using to improve energy efficiency and to deliver more precise positioning. The drive algorithms have moved away from simple strategies such as analog controllers that simply relate power delivered to the motor windings to the motors rotational speed.

They now employ far more sophisticated techniques such as field-oriented control (FOC) that are better able to deliver precise changes in torque and rotor position. With FOC, a mathematical model predicts with high precision when power transistors should activate to supply power to each of the stator windings in order to control rotor torque.

The maximum torque results when the electric and magnetic fields are offset by 90°, delivering highly efficient motion control. It also ensures high positioning accuracy with no need for expensive sensors or encoders. Instead, the mathematical model uses voltage and current inputs from the motor winding to provide the data needed to estimate position and state accurately.

Figure 2 The use of techniques like FOC delivers highly efficient motion control, which ensures greater positioning accuracy without expensive sensors or encoders. Source: EnSilica

In robotics, these algorithms are being supplemented by techniques such as reinforcement learning. Using machine learning to augment motion control has proven highly effective at delivering precise traction control for both wheeled vehicles and legged robots. Dusty or slippery surfaces can be problematic for any automated traction control systems. Training the system to cope with these difficult surfaces delivers greater stability than conventional model-based techniques.

Such control strategies often call for the use of extensive software-based algorithms running on digital signal processors (DSPs) and other accelerators alongside high-performance microprocessors in a layered architecture because of the different time horizons of each of the components.

An AI model trained using a reinforcement learning model, for example, will typically operate with a longer cycle time than the FOC algorithms and the pulse-width modulation (PWM) control signals below them that ensure the motors follow the response needed. As a result, DSP-based models with long time horizons will be supported by algorithms and peripherals that use hardware assistance to operate and meet the deadlines required for real-time operation.

The case for custom hardware

The hard real-time functions are those that have direct control over the power transistors that deliver power to the motor windings, usually implemented in an “inverter” comprising a half-bridge circuit for each of the motor phases. Traditionally, such half-bridge controllers have focused on the implementation of timing loops for PWM.

The switching frequencies are often too high to be supported reliably by software running even on a dedicated microprocessor without needing the processor to be clocked at excessive frequencies. The state machines used to implement PWM switching also take care of functions such as dead-time insertion, which is used to ensure that each transistor doesn’t turn on before its counterpart transistor in the half-bridge inverter is turned off.

The timing gap prevents the shoot-through of current that would result if both transistors were active at the same time. The excess current can damage the motor windings and the drive circuit board. These subsystems are so important that they are often provided as standard building blocks for industrial microcontrollers.

However, in the context of increased threats from hackers and the need to support advanced algorithms, the inverter controller can become a vital component in supporting overall system resilience. By customising the inverter controller, implementors can more easily guarantee safety and security, as well as protect core traction-control IP. Partitioning of the inverter and the rest of the drive subsystem need not just support all three aims, which can also reduce the cost of implementation and verification.

A major advantage of hardware in terms of security is its relative immutability compared to software code. Attackers cannot replace important parts of the hardware algorithm if they gain access. This simplifies some aspects of security certification in addition. Techniques such as formal verification can determine whether the circuitry can ever enter a particular state. Future updates to the system will not directly affect that circuitry.

It’s possible for code changes to alter the interactions between the microcontroller-based subsystems and the lower-level hardware. However, this relationship provides opportunities for the designer to improve their ability to guarantee safe operation, even under the worst-case conditions where a hacker has gained access and replaced the firmware.

Hardware-based lockout mechanisms and security checks can ensure that if the upper-level software of the system is compromised, the system will place itself into a safe state. The lockouts can include support for mechanisms such as secure boot. This ensures that only the software that passes the ASIC’s own checks can activate the motor.

Using hardware for safety and security protection can help reduce the cost of software assurance, which is now subject to legislation such as the European Union’s Cybersecurity Resilience Act (CRA). The new law demands that manufacturers and service operators issue software updates for critically compromised systems.

By moving key elements of the system design into hardware and minimizing the implications of a hack, the designer can reduce the need for frequent updates if new vulnerabilities are found in upper-level software. Similarly, moving interlocks into hardware simplifies the task of demonstrating safe operation for standards such as ISO 26262 compared with purely software-based implementations.

Physical attacks can often involve power interruptions, which provides a way to design an ASIC that protects against such tampering. For example, if power monitoring circuitry detects a brownout, it can reset the microprocessor and place the rest of the system in a safe, quiescent state.

Hardware choices that support compliance and control

Alongside the additional functions, an ASIC inverter controller can host more extensive parts of the motor-control subsystem and reduce the cost of the microprocessor components. For example, FOC relies on trigonometric and other computationally expensive transforms.

Moving these into a coprocessor block in the ASIC can streamline the design. This combination can also reduce control latency by connecting inputs from current and voltage sensors to the low-level DSP functions.

The functions need not all be fixed. Modern ASICs may include configurable blocks such as programmable filters, gain stages, and parameterizable logic to offer a level of adaptability. The use of programmable functions can let a single ASIC design control various motor configurations across an entire product range.

The programming of these elements illustrates one of the many safety and security trade-offs that design teams can make. Incorporating non-volatile memory into the ASIC can provide the greatest security. Putting the programmable elements into an ASIC that can be locked by blowing fuses after manufacturing is more secure than a design where a host microcontroller writes configuration values during the boot process.

The MCU-based control chips require a silicon process suitable for storing the firmware code, normally based on flash memory. This implies some additional processing masks, which increase the cost of the final product, a factor especially sensitive if the production volume is high.

If the design calls for the high-voltage capability offered by Bipolar-CMOS-DMOS (BCD) processes for the motor-drive circuitry, a second die may be needed for non-volatile memory. But the flash CMOS process will normally support a higher logic density than the BCD-based parts, which allows the overall cost to be optimized.

Thanks to its ability to support deterministic control loops and support verification techniques that can ease security and safety certification, the use of hardware is becoming increasingly important to e-mobility and robotics designs.

Through careful architecture selection, such hardware can enable the use of software for flexibility and its own ability to support novel control strategies as they evolve. The result is an environment where ASIC use can offer the best of both worlds to design teams.

David Tester, chief engineer at EnSilica, has 30+ years of experience in the development of analogue, digital and mixed-signal ICs across a wide range of semiconductor products.

Related Content

- Learning the Basics of Motor Control

- Optimizing motor control for energy efficiency

- Five trends to watch in automotive motor control

- MCUs specialize in motor control and power conversion systems

- High-Performance Motor Control Chip with Multi-Core Architecture

The post Custom hardware helps deliver safety and security for electric traction appeared first on EDN.

Перемога КПІшниць у кіберзмаганнях!

🏆 Вітаємо жіночу команду гуртка dcua-school з перемогою у CTF for Women — кіберзмагань, які проводять у межах національної ініціативи Національного координаційного центру кібербезпеки «Шлях жінок у кібербезпеці: історії, виклики, успіх» задля посилення ролі жінок у кібербезпеці.

Vishay Intertechnology Automotive Grade MKP1848e DC Link Film Capacitor Delivers High Temp. Operation Up to +125 °C and High Robustness Under High Humidity

Designed for Automotive, Energy, and Industrial Applications, AEC-Q200 Qualified Device Withstands Grade III THB Testing

Vishay Intertechnology, Inc. introduced a new AEC-Q200 qualified DC-Link metallized polypropylene film capacitor designed for the harsh conditions of automotive, energy, and industrial applications. Offering high temperature operation up to +125 °C, the Vishay Roederstein MKP1848e delivers ripple current up to 44.5 A and withstands temperature humidity bias (THB) in accordance with Grade III of IEC60384-16 ed.3 – 60 °C / 93 % R.H for 1344 hours at rated voltage.

With its high temperature operation and resistance to high humidity, the Automotive Grade capacitor released, is ideal for automotive power conversion applications such as on-board chargers (OBC), power trains, HVAC systems, e-compressors, and DC/DC converters. This next-generation DC-Link capacitor also addresses the stringent needs for energy and industrial power conversion applications such as fast chargers, solar inverters, rectifiers for hydrogen electrolyzers, battery storage systems, motor drives, and UPS.

The MKP1848e offers rated capacitance from 1 µF to 140 µF and low ESR down to 1.0 mΩ, in rated voltages from 500 VDC to 1300 VDC. The devices provide 25 % higher ripple current density than previous-generation solutions with the same volume, while its compact footprint and pitch options down to 22.5 mm enable volume reductions up to 40 % and 15 %, respectively, at 500 VDC and 900 VDC.

To meet the standard high voltage levels of electric (EV) and plug-in hybrid electric vehicles (PHEV), the MKP1848e withstands operating voltages from 250 VDC to 800 VDC at +125 °C for a limited time. It also features high thermal shock capabilities — withstanding 1000 temperature cycles from -40 °C to +125 °C, with a 30-minute dwell time for each temperature extreme.

The post Vishay Intertechnology Automotive Grade MKP1848e DC Link Film Capacitor Delivers High Temp. Operation Up to +125 °C and High Robustness Under High Humidity appeared first on ELE Times.

Exclusive Insights: Kaynes Semicon & Emerson India to Deploy NI Test Systems at Sanand OSAT, Confirmed at Semicon India 2025

In the backdrop of Semicon India 2025, Kaynes Semicon announces a strategic partnership with Emeron’s NI Semiconductor Test Systems (STS). Under the strategic partnership, Kaynes will deploy Emerson’s NI STS as the preferred platform across its expanding semiconductor test facilities.

“We have partnered in the sense that we have invested in those testers, and those would be a part of our ecosystem that we build,” says Mr Raghu Panicker, CEO of Kaynes Semicon Private Limited, in an exclusive conversation with ELE Times. “They have already given us their best possible prices for the testers, and we will deploy them in the products that we will assemble and test in Sanand, Gujarat,” he adds.

Scope of Work

The collaboration will unify test infrastructure across Kaynes’ analog, mixed-signal, RF, power, and MEMS devices—enhancing production speed, ensuring test flexibility, and shortening time-to-market. This move reinforces Emerson’s vision of establishing itself as a trusted Test-as-a-Service partner for the semiconductor industry.

Emergence of Partnerships

Underlining the need for partnerships as India strives to achieve its semiconductor ambitions, Shitendra Bhattacharya, Country Head and Director, India, Emerson Test and Measurement Buseiness Group says, “ The great value add that we were able to offer and where we see a synergy is the fact that our hardware and software capabilities have come together in modular, flexible, and scalable system” in an exclusive conversation with ELE Times at Semicon India 2025.

Adding to the business aspect of securing investments, he says, “NI Testers are the most preferred because of the modularity, flexibility, and scalability. These platforms can evolve into different kinds of chips that they will be testing in the future.”

About the systems

The NI STS is a PXI-based test solution offering compact form factor, reconfigurable architecture, and software integration through LabVIEW and TestStand, enabling reuse of instruments and multi-site execution. This helps manufacturers like Kaynes to reduce equipment redundancy, streamline workflow, and respond quickly to changing test requirements.

The partnership is supported by Emerson’s strong India presence, including field engineers, application support, and training resources, ensuring seamless implementation and long-term success for Kaynes’ test operations.

As India ramps up semiconductor manufacturing, Emerson’s NI test platforms are well-positioned to support emerging OSATs and fabs with high-speed, mixed-signal testing. With up to 10x faster test speeds, these systems help reduce capital costs and enable scalable, efficient production—making them ideal for the country’s growing semiconductor ecosystem.

The post Exclusive Insights: Kaynes Semicon & Emerson India to Deploy NI Test Systems at Sanand OSAT, Confirmed at Semicon India 2025 appeared first on ELE Times.

Numitron Clock I made

| submitted by /u/DenkJu [link] [comments] |

BrainChip’s Cloud Platform Lets Developers Use Its Neuromorphic Tech

Харчова безпека та доступ до їжі в КПІ ім. Ігоря Сікорського

У КПІ ім. Ігоря Сікорського впроваджено комплексну систему заходів для забезпечення харчової безпеки серед студентів, співробітників і курсантів.

Nexperia Targets USB With New PD Controllers and ESD Protection Diodes

VisIC unveils Gen 2 D3GaN 650V power devices

HV reed relays are customizable to 20 kV

Series 600 high-voltage reed relays from Pickering Electronics offer over 2500 combinations of rating and connection options. They are customizable from 3.5 kV to 12.5 kV, with standoff voltages from 5 kV to 20 kV and switching power up to 200 W. Switch-to-coil isolation reaches 25 kV, safely separating control circuitry from high-voltage paths even in demanding environments.

Built with vacuum-sealed, instrumentation-grade reed switches, the relays are available with 1 Form A (NO), 1 Form B (NC), and 1 Form C (Changeover) contacts and 5-V, 12-V, or 24-V coils. An optional diode or Zener-diode combination suppresses back EMF, while mu-metal screening reduces magnetic interference. Insulation resistance exceeds 1013 Ω, ensuring minimal leakage and maximum isolation.

A variety of case sizes, connection types (turrets, flying leads, PCB pins), and potting materials helps engineers meet thermal, mechanical, and environmental requirements. Series 600 relays support many high-voltage test and switching applications, including EV BMS and charge-point testing, inverter or insulation-resistance testing in solar systems, and isolation in medical equipment.

Request free pre-production samples, access the datasheet, or try the configuration tool via the product page link below.

The post HV reed relays are customizable to 20 kV appeared first on EDN.

WM-Bus modules enable flexible sub-GHz metering

Quectel has announced the KCMCA6S series of Wireless M‑Bus (WM‑Bus) modules, capable of sub-1 GHz operation for smart metering. Based on Silicon Labs’ EFR32FG23 wireless SoC, featuring a 73‑MHz Arm Cortex‑M33 processor, the modules operate in the 868‑MHz, 433‑MHz, and 169‑MHz bands.

The devices comply with EN 13757‑4, the European standard for wireless metering, and support the WM‑Bus protocol and other proprietary sub‑GHz protocols. Their built-in software stack and flexible configuration modes eliminate the need for third-party protocol integration.

Modules include an optional integrated SAW filter to limit interference from cellular signals, an important factor for devices combining WM-Bus with cellular technologies such as NB-IoT or LTE Cat 1. They feature 32 KB of RAM and 256 KB of flash memory.

Availability for the KCMCA6S series was not provided at the time of this announcement.

The post WM-Bus modules enable flexible sub-GHz metering appeared first on EDN.