Feed aggregator

Emerging Technology Trends in EV Motors

Electric Vehicles (EVs), central to the global climate transition, are also becoming crucial drivers of engineering innovation. At the heart of this transformation lies the electric motor, an area now attracting intense R&D focus as automakers chase higher efficiency, lower material dependency, and superior driving performance.

Conventional Motor Choices: IM, PMSM, and BLDC

Most EVs today rely on three key motor architectures:

– Induction Motors (IM): Rugged but less efficient.

– Permanent Magnet Synchronous Motors (PMSM): Highly efficient and used in high-performance vehicles.

– Brushless DC Motors (BLDC): Lightweight and ideal for scooters and bikes, using electronic commutation instead of brushes.

While these motors have served well, next-generation EV demands—compact packaging, higher power density, optimized cooling, and smarter control—are pushing the industry toward more advanced technologies.

What’s Driving the Next Wave of Motor Innovation

Manufacturers today are actively pursuing:

– Reduction in installation space

– Higher power-to-weight ratios

– Improved thermal management

– Lower reliance on rare-earth materials

– Greater efficiency through refined control electronics

These needs are shaping emerging motor technologies that promise major shifts in EV design.

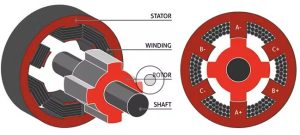

Axial Flux Motors: Compact Powerhouses of the FutureAxial flux motors—often called “pancake motors”—use disc-shaped stators and rotors. Unlike traditional radial flux machines, their magnetic field flows parallel to the shaft.

Key strengths:

– Extremely compact

– Exceptionally high power density

– Ideal for performance-focused EVs

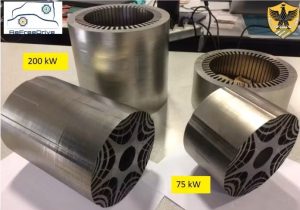

A standout example is YASA, a Mercedes-owned company whose prototype axial flux motor delivers 550 kW (737 hp) at just 13.1 kg, achieving a record 42 kW/kg specific power.

Key challenge: Maintaining a uniform air gap is difficult due to strong magnetic attraction, making heat dissipation more demanding.

Switch Reluctance Motors (SRM): Simple, Strong, Magnet-Free

Switch Reluctance Motors (SRM): Simple, Strong, Magnet-Free

Switch reluctance motors operate using reluctance torque, relying solely on magnetic attraction rather than electromagnetic induction or permanent magnets. The rotor contains no windings or magnets, significantly reducing rare-earth dependence.

Advantages:

– Robust and simple construction

– Low material cost

– High torque potential

Companies like Enedym, Turnitude Technologies, and Advanced Electric Machines (AEM) are actively advancing SRM technology.

Challenges:

– High torque ripple

– Noise and vibration

– More complex control electronics due to trapezoidal DC waveforms

Increasing the number of stator/rotor teeth can reduce ripple but adds manufacturing complexity.

Synchronous Reluctance Motors (SynRM): Tackling Torque Ripple

Synchronous Reluctance Motors (SynRM): Tackling Torque Ripple

SynRMs were developed to overcome the noise and vibration issues of SRMs. Their rotor design uses multiple layered air gaps, creating a shaped flux path that enhances torque production.

Key benefits:

– Operates on sinusoidal waveforms

– Much lower torque ripple

– No magnets required

– Improved noise characteristics

A well-known adaptation is seen in the Tesla Model 3, which uses a SynRM with internal segmented permanent magnets to reduce eddy-current losses and thermal buildup.

In-Wheel Motors: Reinventing Torque Delivery at the Wheels

In-Wheel Motors: Reinventing Torque Delivery at the Wheels

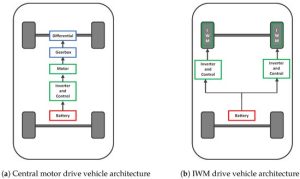

In-wheel motor technology places a dedicated motor inside each wheel, eliminating conventional drivetrains.

Advantages:

– Increased interior space

– Reduced transmission losses

– Precise torque vectoring for improved handling

– Lower mechanical maintenance

GEM Motors, a Slovenian startup, has developed compact, modular in-wheel motor systems that claim up to 20% increased driving range without additional battery capacity.

Challenge:

In-wheel placement increases unsprung mass, affecting ride quality and requiring highly compact yet high-torque designs.

The Road Ahead: Designing Motors for a Resource-Constrained Future

The Road Ahead: Designing Motors for a Resource-Constrained Future

With rising pressure on rare-earth supply chains and the push for higher efficiency, the next generation of EV motors must strike a balance between performance, sustainability, manufacturability, and cost. Technologies minimizing rare-earth usage, improving thermal robustness, and reducing weight will define the industry’s trajectory. As innovation accelerates, electric motors will not just power vehicles—they will shape the future of clean, intelligent, and resource-efficient mobility.

The post Emerging Technology Trends in EV Motors appeared first on ELE Times.

Terahertz Electronics for 6G & Imaging: A Technical Chronicle

As the demand for more spectrum increased with the extensive usage of mobile data, XR/VR, sensing, and autonomous systems, the sub-THz region (100–300 GHz and beyond) emerges as a compelling frontier. In effect, we are approaching the limits of what mm Wave alone can deliver at scale. The THz band promises immense contiguous spectrum, enabling links well above 100 Gbps, and the possibility of co-designing communication and high-resolution sensing (imaging/radar) in a unified platform.

Yet this promise confronts severe physical obstacles: high path loss, molecular absorption, component limitations, packaging losses, and system complexity. This article traces how the industry is navigating those obstacles, what is working now, what remains open, and where the first real systems might land.

The Early Milestones: Lab Prototypes That MatterA landmark announcement came in October 2024 from NTT: a compact InP-HEMT front-end (FE) that achieved 160 Gbps in the 300 GHz band by integrating mixers, PAs, LNAs, and LO PAs in a single IC.

Key technical innovations in that work include:

- A fully differential configuration to cancel local-oscillator (LO) leakage, critical at THz frequencies.

- Reduction of module interconnections (thus insertion loss) by integrating discrete functions into a monolithic chip.

- Shrinking module size from ~15 cm to ~2.8 cm, improving form factor while widening operational bandwidth.

More recently, in mid-2025, NTT (with Keysight and its subsidiary NTT Innovative Devices) demonstrated a power amplifier module capable of 280 Gbps (35 GBaud, 256-QAM) in the J-band (≈220–325 GHz), albeit at 0 dBm output power. This points toward simultaneous scaling of both bandwidth and linear output power, a crucial step forward.

On the standardization/architectural front, partnership experiments like Keysight + Ericsson’s “pre-6G” prototype show how new waveforms and stacks might evolve. In 2024, they demonstrated a base station + UE link (modified 5G stack) over new frequency bands, signaling industry interest in evolving existing layers to support extreme throughput. Ericsson itself emphasizes that 6G will mix evolved and new concepts spectrum aggregation, ISAC, spatial awareness, and energy-efficient designs.

These milestones are not “toy results” they validate that the critical component blocks can already support high-throughput, multi-GHz signals, albeit in controlled lab settings.

Technical Foundations: Devices, Architectures, and PackagingTo move from prototypes to systems, several technical foundations must be matured in parallel:

Device and Front-End Technologies- InP / III–V HEMTs and HBTs remain leading candidates for mixers, LNAs, and PAs at high frequencies, thanks to superior electron mobility and gain.

- SiGe BiCMOS bridges the gap, often handling LO generation, control logic, and lower-frequency blocks, while III–V handles the toughest RF segments.

- Schottky diodes, resonant tunneling diodes (RTDs), and nonlinear mixers play roles for frequency translation and LO generation.

- Photonic sources such as UTC photodiodes or photomixing supplement generation in narrowband, coherent applications. For example, a modified uni-traveling-carrier photodiode (MUTC-PD) has been proposed for 160 Gbps over D-band in a fiber-THz hybrid link.

The challenge is achieving sufficient output power, flat gain over multi-GHz bandwidth, linearity, and noise performance, all within thermal and size constraints.

Architectures and Signal Processing- Multiplication chains (cascaded frequency multipliers) remain the standard path for elevating microwave frequencies into THz.

- Harmonic or sub-harmonic mixing eases LO generation but while managing phase noise is critical.

- Beamforming / phased arrays are essential. Directive beams offer path-loss mitigation and interference control. True-time delay or phase shifting (with very fine resolution) is a design hurdle at THz.

- Waveforms must tolerate impairments (phase noise, CFO). Hybrid schemes combining single-carrier plus OFDM and FMCW / chirp waveforms are under study.

- Joint sensing-communication (ISAC): Using the same waveform for data and radar-like imaging is central to future designs.

- Channel modeling, beam training, blockage prediction, and adaptive modulation are crucial companion software domains.

At THz, packaging and interconnect losses can kill performance faster than device limitations.

- Antenna-in-package (AiP) and antenna-on-substrate (e.g. silicon lens, meta surfaces, dielectric lens) help reduce the distance from active devices to radiating aperture.

- Substrate-integrated waveguides (SIW), micromachined waveguides, quasi-optical coupling replace lossy microstrip lines and CPWs.

- Thermal spreaders, heat conduction, and material selection (low-loss dielectrics) are critical for sustaining device stability.

- Calibration and measurement: On-wafer TRL/LRM up to sub-THz, over-the-air (OTA) test setups, and real-time calibration loops are required for production test.

Propagation in THz is unforgiving:

- Free-space path loss (FSPL) scales with frequency. Every additional decade in frequency adds ~20 dB loss.

- Molecular absorption, especially from water vapor, introduces frequency-specific attenuation notches; engineers must choose spectral windows (D-band, G-band, J-band, etc.).

- Blockage: Humans, objects, and materials often act as near-total blockers at THz.

- Multipath is limited — channels tend toward sparse tap-delay profiles.

Thus, THz is suited for controlled, short-range, high-throughput links or co-located sensing+ communication. Outdoor macro coverage is generally impractical unless beams are extremely narrow and paths well managed. Backhaul and hotspot links are more feasible use cases than full wide-area coverage.

Imaging and Sensing Use CasesUnlike pure communication, imaging demands high dynamic range, spatial resolution, and sometimes passive operation. THz enables:

- Active coherent imaging (FMCW, pulsed radar) for 3D reconstruction, industrial NDT, and package inspection.

- Passive imaging / thermography for detecting emissivity contrasts.

- Computational imaging via coded apertures, compressed sensing, and meta surface masks to reduce sensor complexity.

In system designs, the same front-end and beam infrastructure may handle both data and imaging tasks, subject to power and SNR trade-offs.

Roadmap & Open ProblemsWhile lab successes validate feasibility, many gaps remain before field-ready systems:

- Watt-class, efficient THz sources at room temperature (particularly beyond 200 GHz).

- Low-loss, scalable passives and interconnects (waveguide, delay lines) at THz frequencies.

- Robust channel models across environments (indoor, outdoor, humidity, mobility) with validation data.

- Low-cost calibration / test methodologies for mass production.

- Integrated ISAC signal processing and software stacks that abstract complexity from system integrators.

- Security and coexistence in pencil-beam, high-frequency environments.

The next decade will see THz systems not replacing, but supplementing existing networks. They will begin in enterprise, industrial, and hotspot contexts (e.g. 100+ Gbps indoor links, wireless backhaul, imaging tools in factories). Over time, integrated sensing + communication systems (robotics, AR, digital twins) will leverage THz’s ability to see and talk in the same hardware.

The core enablers: heterogeneous integration (III-V + CMOS/BiCMOS), advanced packaging and optics, robust beamforming, and tightly coupled signal processing. Lab records such as 160 Gbps in the 300 GHz front-end by NTT, and 280 Gbps in a J-band PA module show that neither bandwidth nor throughput is purely theoretical — the next steps are scaling power, cost, and reliability.

The post Terahertz Electronics for 6G & Imaging: A Technical Chronicle appeared first on ELE Times.

When Tiny Devices Get Big Brains: The Era of Edge and Neuromorphic AI

From data-center dreams to intelligence at the metal

Five years ago “AI” largely meant giant models running in faraway data centers. However, today the story is different, where intelligence is migrating to the device itself, in phones, drones, health wearable’s, factory sensors. This shift is not merely cosmetic, instead it forces the hardware designers to ask: how do you give a tiny, thermally constrained device meaningful perception and decision-making power? As Qualcomm’s leadership puts it, the industry is “in a catbird seat for the edge AI shift,” and the battle is now about bringing capable, power-efficient AI onto the device.

Why edge matters practical constraints, human consequences

There are three blunt facts that drive this migration: latency (milliseconds matter for robots and vehicles), bandwidth (you can’t stream everything from billions of sensors), and privacy (health or industrial data often can’t be shipped to the cloud). The combination changes priorities: instead of raw throughput for training, the trophy is energy per inference and predictable real-time behavior.

How the hardware world is responding

Hardware paths diverge into pragmatic, proven accelerators and more speculative, brain-inspired designs.

- Pragmatic accelerators: TPUs, NPUs, heterogeneous SoCs.

Google’s Edge TPU family and Coral modules demonstrate the pragmatic approach: small, task-tuned silicon that runs quantized CNNs and vision models with tiny power budgets. At the cloud level Google’s new TPU generations (and an emerging Ironwood lineup) show the company’s ongoing bet on custom AI silicon spanning cloud to edge. - Mobile/SoC players double down: Qualcomm and others are reworking mobile chips for on-device AI, shifting CPU micro architectures and embedding NPUs to deliver generative and perception workloads in phones and embedded devices. Qualcomm’s public positioning and product roadmaps are explicit: the company expects edge AI to reshape how devices are designed and monetized.

- In-memory and analog compute: to beat the von Neumann cost of moving data. Emerging modules and research prototypes put compute inside memory arrays (ReRAM/PCM) to slash energy per operation, an attractive direction for always-on sensing.

The wild card: neuromorphic computing

If conventional accelerators are an evolutionary path, neuromorphic chips are a more radical reimagination. Instead of dense matrix math and clocked pipelines, neuromorphic hardware uses event-driven spikes, co-located memory and compute, and parallel sparse operations — the same tricks biology uses to run a brain on ~20 W.

Intel, one of the earliest movers, says the approach scales: Loihi research chips and larger systems (e.g., the Hala Point neuromorphic system) show how neuromorphic designs can reach hundreds of millions or billions of neurons while keeping power orders of magnitude lower than conventional accelerators for certain tasks. Those investments signal serious industrial interest, not just academic curiosity.

Voices from the field: what leaders are actually saying

- “We’re positioning for on-device intelligence not just as a marketing line, but as an architecture shift,” paraphrase of Qualcomm leadership describing the company’s edge AI strategy and roadmap.

- “Neuromorphic systems let us explore ultra-low power, event-driven processing that’s ideal for sensors and adaptive control,” Intel’s Loihi programme commentary on the promise of on-chip learning and energy efficiency.

- A recent industry angle: big platform moves (e.g., companies making development boards and tighter dev ecosystems available) reflect a desire to lower barriers. The Qualcomm–Arduino alignment and new low-cost boards aim to democratize edge AI prototyping for millions of developers.

Where hybrid architecture wins: pragmatic use cases

Rather than “neuromorphic replaces everything,” the likely near-term scenario is hybrid systems:

- Dense pretrained CNNs (object detection, segmentation) run on NPUs/TPUs.

- Spiking neuromorphic co-processors handle always-on tasks: anomaly detection, low-latency sensor fusion, prosthetic feedback loops.

- Emerging in-memory modules reduce the energy cost of massive matrix multiplies where appropriate.

Practical example: an autonomous drone might use a CNN accelerator for scene understanding while a neuromorphic path handles collision avoidance from event cameras with microsecond reaction time.

Barriers: the messy middle between lab and product

- Algorithmic mismatch: mainstream ML is dominated by backpropagation and dense tensors; mapping these workloads efficiently to spikes or in-memory analog is still an active research problem.

- Tooling and developer experience: frameworks like PyTorch/TensorFlow are not native to SNNs; toolchains such as Intel’s Lava and domain projects exist but must mature for broad adoption.

- Manufacturing & integration: moving prototypes into volume production and integrating neuromorphic blocks into SoCs poses yield and ecosystem challenges.

Market dynamics & the investment climate

There’s heavy capital flowing into edge AI and neuromorphic startups, and forecasts project notable growth in neuromorphic market value over the coming decade. That influx is tempered by a broader market caution — public leaders have noted hype cycles in AI investing but history shows that even bubble phases can accelerate technological foundations that persist.

Practical advice for engineering and product teams

- Experiment now prototype with Edge TPUs/NPUs and cheap dev boards (Arduino + Snapdragon/Dragonwing examples are democratizing access) to validate latency and privacy requirements.

- Start hybrid design thinking split workloads into dense inference (accelerator) vs event-driven (neuromorphic) buckets and architect the data pipeline accordingly.

- Invest in tooling and skill transfer train teams on spiking networks, event cameras, and in-memory accelerators, and contribute to open frameworks to lower porting costs.

- Follow system co-design unify hardware, firmware, and model teams early; the edge is unforgiving of mismatches between model assumptions and hardware constraints.

Conclusion: what will actually happen

Expect incremental but practical wins first: more powerful, efficient NPUs and smarter SoCs bringing generative and perception models to phones and industrial gateways. Parallel to that, neuromorphic systems will move from research novelties into niche, high-value roles (always-on sensing, adaptive prosthetics, extreme low-power autonomy).

The real competitive winners will be organizations that build the whole stack: silicon, software toolchains, developer ecosystems, and use-case partnerships. In short: intelligence will increasingly live at the edge, and the fastest adopters will design for hybrid, energy-aware systems where neuromorphic and conventional accelerators complement not replace each other.

The post When Tiny Devices Get Big Brains: The Era of Edge and Neuromorphic AI appeared first on ELE Times.

Inside the Hardware Lab: How Modern Electronic Devices Are Engineered

The engineering of contemporary electronic devices reflects a convergence of system thinking, material maturity, multidisciplinary collaboration, and accelerated development cycles. In laboratories across the world, each new product emerges from a structured, iterative workflow that integrates architecture, hardware, firmware, testing, and manufacturing considerations into a cohesive design process. As electronic systems become more compact, intelligent, and operationally demanding, the pathway from concept to certified production device requires a high level of methodological discipline.

This article outlines how modern electronics are engineered, focusing on workflows, design considerations, and the interdependencies that define professional hardware development today.

Requirements Engineering: Establishing the Foundation

The design of any electronic device begins with a comprehensive articulation of requirements. These requirements typically combine functional objectives, performance targets, environmental constraints, safety expectations, and compliance obligations.

Functional objectives determine what the system must achieve, whether sensing, processing, communication, actuation, or power conversion. Performance parameters such as accuracy, latency, bandwidth, power consumption, and operating lifetime define the measurable boundaries of the design. Environmental expectations—temperature range, ingress protection, shock and vibration tolerance, electromagnetic exposure, and mechanical stresses—shape the system’s robustness profile.

Regulatory frameworks, including standards such as IEC, UL, BIS, FCC, CE, and sector-specific certifications (automotive, medical, aerospace), contribute additional constraints. The initial requirement set forms the reference against which all subsequent design decisions are evaluated, creating traceability between intent and implementation.

System Architecture: Translating Requirements into Structure

System architecture bridges conceptual requirements and concrete engineering design. The process involves defining functional blocks and selecting computational, sensing, power, and communication strategies capable of fulfilling the previously established criteria.

The architecture phase typically identifies the processing platform—ranging from microcontrollers to SoCs, MPUs, or FPGAs—based on computational load, determinism, power availability, and peripheral integration. Communication subsystems are established at this stage, covering interfaces such as I²C, SPI, UART, USB, CAN, Ethernet, or wireless protocols.

The power architecture also takes shape here, mapping energy sources, conversion stages, regulation mechanisms, and protection pathways. Considerations such as thermal distribution, signal isolation, noise-sensitive regions, and preliminary enclosure constraints influence the structural arrangement. The architectural framework becomes the guiding reference for schematic and PCB development.

Component Selection: Balancing Performance, Reliability, and Lifecycle

Modern device design is deeply influenced by semiconductor availability, lifecycle predictability, and performance consistency. Component selection involves more than identifying electrically suitable parts; it requires an understanding of long-term supply chain stability, tolerance behaviour, temperature performance, reliability data, and compatibility with manufacturing processes.

Processors, sensors, regulators, discrete, passives, communication modules, and protection components are evaluated not only for electrical characteristics but also for de-rating behaviours, thermal performance, and package-level constraints. Temperature coefficients, impedance profiles, safe-operating-area characteristics, clock stability, and signal integrity parameters become central evaluation factors.

The resulting bill of materials represents an intersection of engineering decisions and procurement realities, ensuring the device can be produced reliably throughout its intended lifespan.

Schematic Design: The Logical Core of the Device

Schematic design formalizes the architectural plan into detailed electrical connectivity. This stage defines logical relationships, reference paths, power distribution, signal conditioning, timing sequences, and safety structures.

Circuit blocks—analog conditioning, digital logic, power conversion, RF front-ends, sensor interfaces, and display or communication elements—are designed with full consideration of parasitic behaviour, noise propagation, and functional dependencies. Power distribution requires careful sequencing, decoupling strategies, transient response consideration, and ripple management. Signal interfaces require appropriate level shifting, impedance alignment, and termination strategies.

Test points, programming headers, measurement references, and diagnostic interfaces are defined at this stage to ensure observability during validation. The schematic ultimately serves as the authoritative source for layout and firmware integration.

PCB Layout: Integrating Electrical, Mechanical, and Thermal Realities

PCB layout transforms the schematic into a physical system where electrical performance, manufacturability, and thermal behaviour converge. The arrangement of components, routing topology, layer stack-up, ground referencing, and shielding determines the system’s electromagnetic and thermal characteristics.

High-speed interfaces require controlled impedance routing, differential pair tuning, length matching, and clear return paths. Power networks demand minimized loop areas, appropriate copper thickness, and distribution paths that maintain voltage stability under load. Sensitive analog signals are routed away from high-noise digital or switching-power regions. Thermal dissipation—achieved through copper pours, thermal vias, and heat-spreading strategies—ensures the system can sustain continuous operation.

Mechanical constraints, such as enclosure geometry, connector placement, mounting-hole patterns, and assembly tolerances, influence layout decisions. The PCB thus becomes a synthesized embodiment of electrical intent and mechanical feasibility.

Prototyping and Hardware Bring-Up: Validating the Physical Implementation

Once fabricated, the prototype enters hardware bring-up, a methodical verification process in which the design is examined against its expected behavior. Validation typically begins with continuity and power integrity checks, ensuring that supply rails meet voltage, ripple, and transient requirements.

System initialization follows, involving processor boot-up, peripheral activation, clock stability verification, and interface-level communication checks. Subsystems are evaluated individually—power domains, sensor blocks, RF modules, analog interfaces, digital buses, and storage components.

Observations from oscilloscopes, logic analyzers, current probes, and thermal imagers contribute to a detailed understanding of the device’s operational profile. Any deviations from expected behavior guide iterative optimization in subsequent revisions.

Firmware Integration: Achieving Functional Cohesion

Firmware integration establishes coordination between hardware capabilities and system functionality. Board-support packages, peripheral drivers, middleware stacks, and application logic are aligned with the hardware’s timing, power, and performance characteristics.

Real-time constraints influence the choice of scheduling structures—whether bare-metal loops, cooperative architectures, or real-time operating systems. Communication stacks, sensor acquisition pipelines, memory management, and power-state transitions are implemented and tested on the physical hardware.

Interaction between firmware and hardware exposes edge cases in timing, voltage stability, electromagnetic sensitivity, or analog behavior, which often inform refinements in both domains.

Validation and Testing: Confirming Performance, Robustness, and Compliance

Comprehensive testing examines a device’s functionality under nominal and boundary conditions. Functional validation assesses sensing accuracy, communication stability, user-interface behavior, control logic execution, and subsystem interoperability. Reliability evaluation includes thermal cycling, vibration exposure, mechanical stress tests, humidity conditioning, and operational aging.

Electromagnetic compatibility testing examines emissions and immunity, including radiated and conducted profiles, ESD susceptibility, fast transients, and surge resilience. Pre-compliance evaluation during early prototypes reduces the probability of redesign during final certification stages.

Data collected during validation ensures that the system behaves predictably throughout its expected operating envelope.

Manufacturing Readiness: Transitioning from Prototype to Production

Production readiness involves synchronizing design intent with assembly processes, quality frameworks, and cost structures. Design-for-manufacturing and design-for-assembly considerations ensure that the device can be fabricated consistently across multiple production cycles.

Manufacturing documentation—including fabrication drawings, Gerber files, pick-and-place data, test specifications, and assembly notes—forms the reference package for contract manufacturers. Automated test equipment, in-circuit test fixtures, and functional test jigs are developed to verify each assembled unit.

Bill-of-materials optimization, yield analysis, and component sourcing strategies ensure long-term production stability.

Compliance and Certification: Meeting Regulatory Obligations

Final certification ensures that the device adheres to the safety, electromagnetic, and environmental requirements of the markets in which it will be deployed. Testing laboratories evaluate the system against regulatory standards, verifying electrical safety, electromagnetic behaviour, environmental resilience, and user-level protections.

The certification phase formalizes the device’s readiness for commercial deployment, requiring complete technical documentation, traceability data, and repeatable test results.

Lifecycle Management: Sustaining the Design Beyond Release

After the product reaches the market, lifecycle management ensures its sustained usability and manufacturability. Engineering change processes address component obsolescence, firmware enhancements, mechanical refinements, or field-observed anomalies.

Long-term reliability data, manufacturing feedback, and supplier updates contribute to ongoing revisions. In connected systems, firmware updates may be deployed over the air, extending functionality and addressing vulnerabilities.

Lifecycle management closes the loop between deployment and continuous improvement.

Conclusion

The design of a modern electronic device is a coordinated engineering endeavour that integrates requirements analysis, architectural planning, hardware design, firmware development, validation, manufacturing readiness, and lifecycle stewardship. Each stage influences the next, forming a continuous chain of interdependent decisions.

As technological expectations expand, the engineering methodologies supporting electronic design continue to mature. The result is a disciplined, multi-phase workflow that enables the creation of devices that are reliable, certifiable, scalable, and aligned with the complex operational demands of contemporary applications.

The post Inside the Hardware Lab: How Modern Electronic Devices Are Engineered appeared first on ELE Times.

Transitioning from Industry 4.0 to 5.0: It’s not simple

The shift from Industry 4.0 to 5.0 is not an easy task. Industry 5.0 implementation will be complex, with connected devices and systems sharing data in real time at the edge. It encompasses a host of technologies and systems, including a high-speed network infrastructure, edge computing, control systems, IoT devices, smart sensors, AI-enabled robotics, and digital twins, all designed to work together seamlessly to improve productivity, lower energy consumption, improve worker safety, and meet sustainability goals.

(Source: Adobe Stock)

(Source: Adobe Stock)

In the November/December issue, we take a look at evolving Industry 4.0 trends and the shift to the next industrial evolution: 5.0, building on existing AI, automation, and IoT technologies with a collaboration between humans and cobots.

Technology innovations are central to future industrial automation, and the next generation of industrial IoT technology will leverage AI to deliver productivity improvements through greater device intelligence and automated decision-making, according to Jack Howley, senior technology analyst at IDTechEx. He believes the global industry will be defined by the integration of AI with robotics and IoT technologies, transforming manufacturing and logistics across industries.

As factories become smarter, more connected, and increasingly autonomous, MES, digital twins, and AI-enabled robotics are redefining smart manufacturing, according to Leonor Marques, architecture and advocacy director of Critical Manufacturing. These innovations can be better-interconnected, contributing to smarter factories and delivering meaningful, contextualized, and structured information, she said.

One of those key enabling technologies for Industry 4.0 is sensors. TDK SensEI defines Industry 4.0 by convergence, the merging of physical assets with digital intelligence. AI-enabled predictive maintenance systems will be critical for achieving the speed, autonomy, and adaptability that smart factories require, the company said.

Edge AI addresses the volume of industrial data by embedding trained ML models directly into sensors and devices, said Vincent Broyles, senior director of global sales engineering at TDK SensEI. Instead of sending massive data streams to the cloud for processing, these AI models analyze sensor data locally, where it’s generated, reducing latency and bandwidth use, he said.

Robert Otręba, CEO of Grinn Global, agrees that industrial AI belongs at the edge. It delivers three key advantages: low latency and real-time decision-making, enhanced security and privacy, and reduced power and connectivity costs, he said.

Otręba thinks edge AI will power the next wave of industrial intelligence. “Instead of sending vast streams of data off-site, intelligence is brought closer to where data is created, within or around the machine, gateway, or local controller itself.”

AI is no longer an optional enhancement, and this shift is driven by the need for real-time, contextually aware intelligence with systems that can analyze sensor data instantly, he said.

Lisa Trollo, MEMS marketing manager at STMicroelectronics, calls sensors the silent leaders driving the industrial market’s transformation, serving as the “eyes and ears” of smart factories by continuously sensing pressure, temperature, position, vibration, and more. “In this industrial landscape, sensors are the catalysts that transform raw data into insights for smarter, faster, and more resilient industries,” she said.

Energy efficiency also plays a big role in industrial systems. Power management ICs (PMICs) are leading the way by enabling higher efficiency. In industrial and industrial IoT applications, PMICs address key power challenges, according to contributing writer Stefano Lovati. He said the use of AI techniques is being investigated to further improve PMIC performance, with the aim of reducing power losses, increasing energy efficiency, and reducing heat dissipation.

Don’t miss the top 10 AC/DC power supplies introduced over the past year. These power supplies focus on improving efficiency and power density for industrial and medical applications. Motor drivers are also a critical component in industrial design applications as well as automotive systems. The latest motor drivers and development tools add advanced features to improve performance and reduce design complexity.

The post Transitioning from Industry 4.0 to 5.0: It’s not simple appeared first on EDN.

Expanding power delivery in systems with USB PD 3.1

The Universal Serial Bus (USB) started out as a data interface, but it didn’t take long before progressing to powering devices. Initially, its maximum output was only 2.5 W; now, it can deliver up to 240 W over USB Type-C cables and connectors, processing power, data, and video. This revision is known as Extended Power Range (EPR), or USB Power Delivery Specification 3.1 (USB PD 3.1), introduced by the USB Implementers Forum. EPR uses higher voltage levels (28 V, 36 V, and 48 V), which at 5 A will deliver power of 140 W, 180 W, and 240 W, respectively.

USB PD 3.1 has an adjustable voltage supply mode, allowing for intermediate voltages between 9 V and the highest fixed voltage of the charger. This allows for greater flexibility by meeting the power needs of individual devices. USB PD 3.1 is backward-compatible with previous USB versions including legacy at 15 W (5 V/3 A) and the standard power range mode of below 100 W (20 V/5 A).

The ability to negotiate power for each device is an important strength of this specification. For example, a device consumes only the power it needs, which varies depending on the application. This applies to peripherals, where a power management process allows each device to take only the power it requires.

The USB PD 3.1 specification found a place in a wide range of applications, including laptops, gaming stations, monitors, industrial machinery and tools, small robots and drones, e-bikes, and more.

Microchip USB PD demo boardMicrochip provides a USB PD dual-charging-port (DCP) demonstration application, supporting the USB PD 3.1 specification. The MCP19061 USB PD DCP reference board (Figure 1) is pre-built to show the use of this technology in real-life applications. The board is fully assembled, programmed, and tested to evaluate and demonstrate digitally controlled smart charging applications for different USB PD loads, and it allows each connected device to request the best power level for its own operation.

Figure 1: MCP19061 USB DCP board (Source: Microchip Technology Inc.)

Figure 1: MCP19061 USB DCP board (Source: Microchip Technology Inc.)

The board shows an example charging circuit with robust protections. It highlights charge allocation between the two ports as well as dynamically reconfigurable charge profile availability (voltage and current) for a given load. This power-balancing feature between ports provides better control over the charging process, in addition to delivering the right amount of power to each device.

The board provides output voltages from 3 V to 21 V and output currents from 0.5 A to 3 A. Its maximum input voltage range is from 6 V to 18 V, with 12 V being the recommended value.

The board comes with firmware designed to operate with a graphical user interface (GUI) and contains headers for in-circuit serial programming and I2C communication. An included USB-to-serial bridging board (such as the BB62Z76A MCP2221A breakout board USB) with the GUI allows different configurations to be quickly tested with real-world load devices charging on the two ports. The DCP board GUI requires a PC with Microsoft Windows operating system 7–11 and a USB 2.0 port. The GUI then shows parameter and board status and faults and enables user configuration.

DCP board componentsBeing a port board with two ports, there are two independent USB PD channels (Figure 2), each with their own dedicated analog front end (AFE). The AFE in the Microchip MCP19061 device is a mixed-signal, digitally controlled four-switch buck-boost power controller with integrated synchronous drivers and an I2C interface (Figure 3).

Figure 2: Two independently managed USB PD channels on the MCP19061-powered DCP board (Source: Microchip Technology Inc.)

Figure 2: Two independently managed USB PD channels on the MCP19061-powered DCP board (Source: Microchip Technology Inc.)  Figure 3: Block diagram of the MCP19061 four-switch buck-boost device (Source: Microchip Technology Inc.)

Figure 3: Block diagram of the MCP19061 four-switch buck-boost device (Source: Microchip Technology Inc.)

Moreover, one of the channels features the Microchip MCP22350 device, a highly integrated, small-format USB Type-C PD 2.0 controller, whereas the other channel contains a Microchip MCP22301 device, which is a standalone USB Type-C PD port controller, supporting the USB PD 3.0 specification.

The MCP22350 acts as a companion PD controller to an external microcontroller, system-on-chip or USB hub. The MCP22301 is an integrated PD device with the functionality of the SAMD20 microcontroller, a low-power, 32-bit Arm Cortex-M0+ with an added MCP22350 PD media access control and physical layer.

Each channel also has its own UCS4002 USB Type-C port protector, guarding from faults but also protecting the integrity of the charging process and the data transfer (Figure 4).

Traditionally a USB Type-C connector embeds the D+/D– data lines (USB2), Rx/Tx for USB3.x or USB4, configuration channel (CC) lines for charge mode control, sideband-use (SBU) lines for optional functions, and ground (GND). The UCS4002 protects the CC and D+/D– lines for short-to-battery. It also offers battery short-to-GND (SG_SENS) protection for charging ports.

Integrated switching VCONN FETs (VCONN is a dedicated power supply pin in the USB Type-C connector) provide overvoltage, undervoltage, back-voltage, and overcurrent protection through the VCONN voltage. The board’s input rail includes a PMOS switch for reverse polarity protection and a CLC EMI filter. There are also features such as a VDD fuse and thermal shutdown, enabled by a dedicated temperature sensor, the MCP9700, which monitors the board’s temperature.

Figure 4: Block diagram of the UCS4002 USB port protector device (Source: Microchip Technology Inc.)

Figure 4: Block diagram of the UCS4002 USB port protector device (Source: Microchip Technology Inc.)

The UCS4002 also provides fault-reporting configurability via the FCONFIG pin, allowing users to configure the FAULT# pin behavior. The CC, D+/D –, and SG_SENS pins are electrostatic-discharge-protected to meet the IEC 61000-4-2 and ISO 10605 standards.

The DCP board includes an auxiliary supply based on the MCP16331 integrated step-down switch-mode regulator providing a 5-V voltage and an MCP1825 LDO linear regulator providing a 3.3-V auxiliary voltage.

Board operationThe MCP19061 DCP board shows how the MCP19061 device operates in a four-switch buck-boost topology for the purpose of supplying USB loads and charging them with their required voltage within a permitted range, regardless of the input voltage value. It is configured to independently regulate the amount of output voltage and current for each USB channel (their individual charging profile) while simultaneously communicating with the USB-C-connected loads using the USB PD stack protocols.

All operational parameters are programmable using the two integrated Microchip USB PD controllers, through a dynamic reconfiguration and customization of charging operations, power conversion, and other system parameters. The demo shows how to enable the USB PD programmable power supply fast-charging capability for advanced charging technology that can modify the voltage and current in real time for maximum power outputs based on the device’s charging status.

The MCP19061 device works in conjunction with both current- and voltage-sense control loops to monitor and regulate the load voltage and current. Moreover, the board automatically detects the presence or removal of a USB PD–compliant load.

When a USB PD–compliant load is connected to the USB-C Port 1 (on the PCB right side; this is the higher one), the USB communication starts and the MCP19061 DCP board displays the charging profiles under the Port 1 window.

If another USB PD load is connected to the USB-C Port 2, the Port 2 window gets populated the same way.

The MCP19061 PWM controllerThe MCP19061 is a highly integrated, mixed-signal four-switch buck-boost controller that operates from 4.5 V to 36 V and can withstand up to 42 V non-operating. Various enhancements were added to the MCP19061 to provide USB PD compatibility with minimum external components for improved calibration, accuracy, and flexibility. It features a digital PWM controller with a serial communication bus for external programmability and reporting. The modulator regulates the power flow by controlling the length of the on and off periods of the signal, or pulse widths.

The operation of the MCP19061 enables efficient power conversion with the capability to operate in buck (step-down), boost (step-up), and buck-boost topologies for various voltage levels that are lower, higher, or the same as the input voltage. It provides excellent precision and efficiency in power conversions for embedded systems while minimizing power losses. Its features include adjustable switching frequencies, integrated MOSFET drivers, and advanced fault protection. The operating parameters, protection levels, and fault-handling procedures are supervised by a proprietary state machine stored in its nonvolatile memory, which also stores the running parameters.

Internal digital registers handle the customization of the operating parameters, the startup and shutdown profiles, the protection levels, and the fault-handling procedures. To set the output current and voltage, an integrated high-accuracy reference voltage is used. Internal input and output dividers facilitate the design while maintaining high accuracy. A high-accuracy current-sense amplifier enables precise current regulation and measurement.

The MCP19061 contains three internal LDOs: a 5-V LDO (VDD) powers internal analog circuits and gate drivers and provides 5 V externally; a 4-V LDO (AVDD) powers the internal analog circuitry; and a 1.8-V LDO supplies the internal logic circuitry.

The MCP19061 is packaged in a 32-lead, 5 × 5-mm VQFN, allowing system designers to customize application-specific features without costly board real estate and additional component costs. A 1-MHz I2C serial bus enables the communication between the MCP19061 and the system controller.

The MCP19061 can be programmed externally. For further evaluation and testing, Microchip provides an MCP19061 dedicated evaluation board, the EV82S16A.

The post Expanding power delivery in systems with USB PD 3.1 appeared first on EDN.

Нові щербини на старих стінах

Нові щербини з'явилися під час одного з ракетно-дронових обстрілів Києва. А будівля, що отримала ці пошкодження, – це корпус №4 КПІ ім. Ігоря Сікорського, де містяться хіміко-технологічний факультет і факультет біотехнології і біотехніки.

Simple state variable active filter

The state variable active filter (SVAF) is an active filter you don’t see mentioned much today; however, it’s been a valuable asset for us old analog types in the past. This became especially true when cheap dual and quad op-amps became common place, as one can “roll their own” SVAF with just one IC package and still have an op-amp left over for other tasks!

Wow the engineering world with your unique design: Design Ideas Submission Guide

The unique features of this filter are having low-pass (LP), high-pass (HP), and band-pass (BP) filter results simultaneously available, with low component sensitivity, and an independent filter “Q” while creating a quadratic 2nd order filter function with 40-dB/decade slope factors. The main drawback is requiring three op-amps and a few more resistors than other active filter types.

The SVAF employs dual series-connected and scaled op-amp integrators with dual independent feedback paths, which creates a highly flexible filter architecture with the mentioned “extra” components as the downside.

With the three available LP, HP, and BP outputs, this filter seemed like a nice candidate for investigating with the Bode function available in modern DSOs. This is especially so for the newer Siglent DSO implementations that can plot three independent channels, which allows a single Bode plot with three independent plot variables: LP, HP, and BP.

Creating a SVAF with a couple of LM358 duals (didn’t have any DIP-type quad op-amps like the LM324 directly available, which reminds me, I need to order some soon!!), a couple of 0.01-µF mylar Caps, and a few 10 kΩ and 1 kΩ resistors seemed like a fun project.

The SVAF natural frequency corner is simply 1/RC, as shown in the notebook image in Figure 1 as ~1.59 kHz with the mentioned component values. The filter’s “Q” was set by changing R4 and R5.

Figure 1 The author’s hand-drawn schematic with R1=R2, R3=R6, and C1=C2, resistor values are 1 kΩ and 10 kΩ, and capacitors are 0.01 µF.

Figure 1 The author’s hand-drawn schematic with R1=R2, R3=R6, and C1=C2, resistor values are 1 kΩ and 10 kΩ, and capacitors are 0.01 µF.

This produced plots of a Q of 1, 2, and 4 shown in Figure 2, Figure 3, and Figure 4, respectively, along with supporting LTspice simulations.

The DSO Bode function was set up with DSO CH1 as the input, CH2 (red) as the HP, CH3 (cyan) as the LP, and CH4 (green) as the BP. The phase responses can also be seen as the dashed color lines that correspond to the colors of the HP, LP, and BP amplitude responses.

While it is possible to include all the DSO channel phase responses, this clutters up the display too much, so on the right-hand side of each image, the only phase response I show is the BP phase (magenta) in the DSO plots.

Figure 2 The left side shows the Q =1 LTspice plot of the SVAF with the amplitude and phase of the HP (magenta + dashed magenta), the amplitude and phase of the LP (cyan + dashed cyan), and the amplitude and phase of the BP (green + dashed green). The right side shows the Q =1 DSO plot of the SVAF with HP (red), LP (cyan), BP (green), and phase of the BP (magenta).

Figure 3 The left side shows the Q =2 LTspice plot of the SVAF with the amplitude and phase of the HP (magenta + dashed magenta), the amplitude and phase of the LP (cyan + dashed cyan), and the amplitude and phase of the BP (green + dashed green). The right side shows the Q =2 DSO plot of the SVAF with HP (red), LP (cyan), BP (green), and phase of the BP (magenta).

Figure 4 The left side shows the Q =4 LTspice plot of the SVAF with the amplitude and phase of the HP (magenta + dashed magenta), the amplitude and phase of the LP (cyan + dashed cyan), and the amplitude and phase of the BP (green + dashed green). The right side shows the Q =4 DSO plot of the SVAF with HP (red), LP (cyan), BP (green), and phase of the BP (magenta).

The Bode frequency was swept with 33 pts/dec from 10 Hz to 100 kHz using a 1-Vpp input stimulus from a LAN-enabled arbitrary waveform generator (AWG). Note how the three responses all cross at ~1.59 kHz, and the BP phase, or the magenta line for the images on the right side, crosses zero degrees here.

If we extend the frequency of the Bode sweep out to 1 MHz, as shown in Figure 5, well beyond where you would consider utilizing an LM358. The simulation and DSO Bode measurements agree well, even at this range. Note how the simulation depicts the LP LM358 op-amp output resonance ~100 kHz (cyan) and the BP Phase (magenta) response.

Figure 5 The left side shows the Q =7 LTspice plot of the SVAF with the amplitude and phase of the HP (magenta + dashed magenta), the amplitude and phase of the LP (cyan + dashed cyan), and the amplitude and phase of the BP (green + dashed green). The right side shows the Q =7 DSO plot of the SVAF with HP (red), LP (cyan), BP (green), and phase of the BP (magenta).

I’m honestly surprised the simulation agrees this well, considering the filter was crudely assembled on a plug-in protoboard and using the LM358 op-amps. This is likely due to the inverting configuration of the SVAF structure, as our experience has shown that inverting structures tend to behave better with regard to components, breadboard, and prototyping, with all the unknown parasitics at play!

Anyway, the SVAF is an interesting active filter capable of producing simultaneous LP, HP, and BP results. It is even capable of producing an active notch filter with an additional op-amp and a couple of resistors (requires 4 total, but with the LM324, a single package), which the interested reader can discover.

Michael A Wyatt is a life member with IEEE and has continued to enjoy electronics ever since his childhood. Mike has a long career spanning Honeywell, Northrop Grumman, Insyte/ITT/Exelis/Harris, ViaSat and retiring (semi) with Wyatt Labs. During his career he accumulated 32 US Patents and in the past published a few EDN Articles including Best Idea of the Year in 1989.

Related Content

- Unusual 2N3904 transistor circuit

- Simple diff-amp extension creates a square-law characteristic

- DIY isolation transformer enhances Bode analysis with modern DSOs

- Injection locking acts as a frequency divider and improves oscillator performance

The post Simple state variable active filter appeared first on EDN.

Візит школярів

КПІ ім. Ігоря Сікорського відвідали учні 10–11 класів закладів середньої освіти Тетіївської міської територіальної громади. Під час екскурсії старшокласники оглянули Бібліотеку КПІ, кампус університету та навчальний корпус №1.

💎 Грантові стипендії для викладачів КПІ ім. Ігоря Сікорського від MacPaw AI Lab в КПІ

MacPaw AI Lab пропонує грантові стипендії для викладачів КПІ ім. Ігоря Сікорського.

8 000$ рівномірно протягом 6 місяців

+ 2 000$ за прийняті матеріали на конференцію top-tier рівня

Для участі необхідно:

EDOM Seminar Explores the Next Generation of Physical AI Robots Powered by NVIDIA Jetson Thor

The wave of innovation driven by generative AI is sweeping the globe, and AI’s capabilities are gradually extending from language understanding and visual recognition to action intelligence closer to real-world applications. This change makes physical AI, which integrates “perception, reasoning, and action,” the next important threshold for robotics and smart manufacturing. To help Taiwanese industries grasp this multimodal trend, EDOM Technology will hold the “AI ×Multimodal Robotics: New Era of Industrial Intelligence Seminar” on December 3, showcasing NVIDIA Jetson Thor, the ultimate platform for physical AI and robotics, and featuring insights from ecosystem partners who will share innovative applications spanning smart manufacturing, autonomous machines, and education.

As AI technology rapidly advances, robotics is shifting from the traditional perception and response model to a new stage where they can autonomously understand and participate in complex tasks. The rise of multimodal AI enables machines to simultaneously integrate image, voice, semantic, and spatial information, making more precise judgments and actions in the real world, making it possible to “know what to do” and “know how to do it.” As AI capabilities extend from the purely digital realm to the real world, physical AI has become a core driving force for industrial upgrading.

Multimodal × Physical AI: The Next Key Turning Point in Robotics

The seminar focuses on the theme of “Physical AI Driving the Intelligent Revolution of Robotics”, explores how AI, through multimodal perception and autonomous action capabilities, is reshaping the technical architecture and application scenarios of human-machine collaboration. Through technical sharing and case analysis, the seminar will help companies grasp the next turning points of smart manufacturing.

This event will focus on NVIDIA Jetson Thor and its software ecosystem, providing a panoramic view of future-oriented multimodal robotics technology. The NVIDIA Jetson Thor platform combines high-performance GPUs, edge computing, and multimodal understanding to complete perception, inference, decision-making, and action planning all at the device level, significantly improving robot autonomy and real-time responsiveness. Simultaneously, the platform is deeply integrated with NVIDIA Isaac, NVIDIA Metropolis, and NVIDIA Holoscan, creating an integrated development environment from simulation, verification, and testing to deployment, thus accelerating the implementation of intelligent robots and edge AI solutions. NVIDIA Jetson Thor also supports LLM, visual language models (VLMs), and various generative AI models, enabling machines to interpret their surroundings, interact, and take action more naturally, becoming a core foundation for advancing physical AI.

In addition to the core platform analysis, the event features multiple demonstrations and exchange sessions. These includes a showcase of generative AI-integrated robotic applications, highlighting the latest capabilities of the model in visual understanding and action collaboration; an introduction to the ecosystem built by EDOM, sharing cross-field cooperation experiences from education and manufacturing to hardware and software integration; and a hands-on technology experience zone, where attendees can see the practical applications of NVIDIA Jetson Thor in edge AI and multimodal technology.

From technical analysis to industry exchange, Cross-field collaboration reveals new directions for smart machines:

- Analyses of the core architecture of NVIDIA Jetson Thor and the latest developments in multimodal AI by NVIDIA experts.

- Case studies on how Nexcobot introduces AI automation in smart manufacturing.

- Ankang High School, which achieved excellent results at the 2025 FIRST Robotics Competition (FRC) World Championship, showcases how AI and robotics courses can cultivate students’ interdisciplinary abilities in education.

- Insights into LLM and VLM applications in various robotic tasks given by Avalanche Computing.

Furthermore, EDOM will introduce its system integration approaches and deployment cases powered by NVIDIA IGX Orin and NVIDIA Jetson Thor, presenting the complete journey of edge AI technology from simulation to application implementation.

The event will conclude with an expert panel. Featuring leading specialists, the discussion covers collaboration, challenges, and international trends brought by multimodal robotics, helping industries navigate and anticipate the next phase of smart machine innovation.

Driven by physical AI and multimodal technologies, smart machines are entering a new phase of growth. The “AI × Multimodal Robotics: New Era of Industrial Intelligence Seminar” will not only showcase the latest technologies but also aim to connect the supply chain in Taiwan, enabling the manufacturing and robotics industries to seize opportunities in multimodal AI. The event will take place on Wednesday, December 3, 2025, at the Taipei Fubon International Convention Center, with registration and demonstration beginning at 12:30 PM. Enterprises and developers focused on AI, robotics, and smart manufacturing are welcome to join and stay at the forefront of multimodal technology. For more information, please visit https://www.edomtech.com/zh-tw/events-detail/jetson-thor-tech-day/

The post EDOM Seminar Explores the Next Generation of Physical AI Robots Powered by NVIDIA Jetson Thor appeared first on ELE Times.

Зустріч КПІшників із Ахметом Тораном Оздеміром — генеральним директором технологічної компанії ASPILSAN Enerji

Під час другого візиту делегації турецької компанії ASPILSAN Enerji до КПІ ім. Ігоря Сікорського студенти Факультету електроенерготехнiки та автоматики (ФЕА) та Хіміко-технологічного факультету (ХТФ) долучилися до лекції «Технології батарей та енергетичні рішення, які формують майбутнє».

Navitas sampling 3300V and 2300V UHV silicon carbide product portfolio

NUBURU agrees to acquire Italian laser specialist LYOCON

Zener diode (5.1 V) voltage regulator circuit

| Zener voltage = 5.1 V, Input voltage = 9 V, Resistance = 500 ohm [link] [comments] |

Nuvoton Releases Compact High-Power Violet Laser Diode (402nm, 1.7W)

Nuvoton Technology announced today the launch of its compact high-power violet laser diode (402nm, 1.7W), which achieves industry-leading optical output power in the industry-standard TO-56 CAN package. This product realizes compact size, high output power, and long-life, which were previously considered difficult, through our proprietary chip design and thermal management technologies. As a result, it contributes to space-saving and long-life optical systems for a wide range of optical applications.

Achievements:

1. Achieves industry-leading optical output power of 1.7W at 402nm in the industry-standard TO-56 CAN package, contributing to the miniaturization of optical systems.

2. Realizes long-life through proprietary chip design and thermal management technologies, reducing the running costs of optical systems.

3. Expands the lineup of mercury lamp replacement solutions, improving flexibility in product selection according to application.

Latest Addition

In addition, this product is newly added to their lineup of mercury lamp replacement solutions using semiconductor lasers, providing customers with new options. This enables flexible product selection according to application, installation environment, and required performance, improving the freedom of system design.

Its applications include:

・ Laser Direct Imaging (LDI)

・ Resin curing

・ Laser welding

・ 3D printing

・ Biomedical

・ Display

・ Alternative light source for mercury lamps, etc.

Nuvoton Technology Corporation Japan (NTCJ) joined the Nuvoton Group in 2020. As a dedicated global semiconductor manufacturer, NTCJ provides technology and various products cultivated over 60 years since its establishment, and solutions that optimally combine them. We value relationships with our customers and partners, and by providing added value that exceeds expectations, we are working as a global solution company that solves various issues in society, industry, and people’s lives.

The post Nuvoton Releases Compact High-Power Violet Laser Diode (402nm, 1.7W) appeared first on ELE Times.

Powering the Chip Chain, Part 03: “AI is Transforming the Semiconductor Value Chain End-to-End,” Says RS Components’ Amit Agnihotri

| India’s semiconductor ambitions are backed by initiatives like the ₹76,000 crore ISM and the ₹1,000 crore DLI scheme, which focuses on fostering a strong design ecosystem. A critical part of this effort is ensuring design engineers get timely access to quality components.

To highlight how distributors are enabling this, we present our exclusive series — “Powering the Chip Chain” — featuring conversations with key industry players. |

As India solidifies its position in the global electronics manufacturing landscape, the role of distribution has evolved from merely supplying components to enabling rapid, AI-driven innovation. This shift demands hyper-efficient inventory, advanced technical support, and flexible commercial policies.

In an exclusive interaction for the ‘Powering the Chip Chain’ series, Amit Agnihotri, Chief Operating Officer at RS Components & Controls (I) Ltd., shares his perspective on the exponential growth of AI-centric component demand and how digital transformation is equipping distributors to accelerate time-to-market for a new generation of Indian engineers.

AI: The New Core of Product Discovery

The integration of AI is no longer a future concept but a foundational element of distribution platforms. Mr. Agnihotri confirms that RS Components India is integrating AI into both its customer-facing systems and internal operations.

The primary objective is to make product discovery simpler, faster, and more intuitive. By leveraging AI-driven analytics, the company analyzes customer trends and buying patterns to anticipate future needs, ensuring the most relevant products are recommended with greater precision and speed. In line with this vision, RS is also investing heavily in enhancing its website recommendation engine through advanced AI, enabling customers to easily find the right products that best suit their specific applications.

“On our digital platform, AI-powered features guide users in identifying the right product based on their specific needs and selection criteria, significantly improving turnaround time and enhancing the overall experience,” says Agnihotri. This capability also extends internally, allowing RS India to optimize inventory management and ensure offerings remain aligned with volatile market demand.

Exponential Demand for Edge Intelligence

The rapid advancement of AI is fundamentally restructuring component demand, particularly accelerating the need for specialized silicon. This is most evident in the shift of high-performance components away from only high-end data centers.

Mr. Agnihotri notes that RS Components is witnessing exponential growth in AI adoption across core sectors such as automotive, electronics manufacturing, and industrial automation.

This growth is driving demand for specialized parts such as edge AI chips, neural network accelerators, and high-performance GPUs. These solutions, which support AI-centric applications across healthcare devices, autonomous systems, and smart mobility, enable customers to achieve higher processing speeds, ultra-low latency, and greater energy efficiency in their designs.

“The scale and speed at which AI technologies are being integrated into these industries indicate a clear shift in product development priorities—towards high-speed processing capabilities, ultra-low latency architectures, and energy-efficient AI hardware,” he explains.

Empowering R&D with Flexibility and Tools

To support this rapid prototyping and iteration, RS Components focuses on providing R&D teams with both technical enablement and commercial flexibility.

The support spans the entire design cycle, from concept to validation, anchored by the DesignSpark platform. This platform provides an integrated suite of free design tools, including PCB design and simulation, which accelerates the transition from concept to prototype.

Furthermore, all product listings are enriched with technical data. “All listings are enriched with datasheets, footprints, 3D models, parametric filters, and application notes so design engineers can perform compatibility checks and Design For Manufacture (DFM) assessments early in the process,” Agnihotri says.

Crucially, the company has adapted its commercial policies to match the low-volume needs of R&D work:

“Recognising that R&D and PoC work often requires small quantities of the latest components, we operate with No MOQ [Minimum Order Quantity] and No MOV [Minimum Order Value] policies on many products, and we add approximately 5,000 NPIs [New Product Introductions] to our portfolio each month.”

These practices ensure that startups, academic labs, and enterprise R&D teams can source cutting-edge parts in small batches without heavy inventory commitments.

The Policy Tailwinds and Supply Chain Agility

Government initiatives, most notably the Semicon India programme and national AI policies, are playing a material role in creating market readiness.

Amit states, “By incentivizing local manufacturing, design centers and skilling, these programs shorten lead times, attract investment and create predictable demand for AI accelerators, advanced chips and supporting components.” This policy support, he adds, allows distributors to implement deeper localization of inventory and expand value-added services.

To ensure supply chain agility in the face of this growing complexity, RS Components utilizes AI and predictive analytics. Machine-learning models ingest purchase history and market signals to produce more accurate short- and medium-term forecasts.

“AI-driven SKU segmentation and safety-stock algorithms prioritize high-demand electronic components, while predictive lead-time modelling and allocation analytics enable proactive vendor coordination,” he explains. This systemic use of AI helps manage potential foundry constraints and allocation volatility, which remains a persistent challenge in the global semiconductor ecosystem.

Conclusion: The Distributor as an Innovation Partner

Mr. Agnihotri concludes by emphasizing that AI will continue to transform the semiconductor value chain end-to-end—from component design (using AI for simulation) to distribution (through predictive analytics and personalized recommendations).

RS Components’ strategy is clear: by embedding AI into its DesignSpark toolchain, leveraging predictive models to localize inventory, and providing flexible commercial terms, the company is positioning itself as a strategic partner. This integrated approach enables engineers and manufacturers to iterate quickly, source the right components, and scale with confidence, fundamentally accelerating innovation across the Indian market.

The post Powering the Chip Chain, Part 03: “AI is Transforming the Semiconductor Value Chain End-to-End,” Says RS Components’ Amit Agnihotri appeared first on ELE Times.

Екскурсія до R&D центру компанії ТОВ "ПлазмаТек"

Спочатку було слово – оголошення на сторінці профбюро студентів НН ІМЗ (https://t.me/pbikpiii/1) з перепостом на сторінці студентського профкому КПІ (https://t.me/pskpi) про те, що профспілкова організація Інституту запрошує студентів усіх факультетів 7 листопада взяти участь в екскурсії до R&D центру (Центру досліджень і розробок) компанії ТОВ "ПлазмаТек".

Avicena’s LightBundle optical links operating at 4Gbps per lane with transmitter current as low as 100µA per LED

A budget battery charger that also elevates blood pressure

At the tail end of my September 1 teardown of EBL’s first-generation 8-bay battery charger:

I tacked on a one-paragraph confession, with an accompanying photo that as usual, included a 0.75″ (19.1 mm) diameter U.S. penny for size comparison purposes:

I’ll wrap up with a teaser photo of another, smaller, but no less finicky battery charger that I’ve also taken apart, but, due to this piece as-is ending up longer-than-expected (what else is new?), I have decided to instead save for another dedicated teardown writeup for another day:

That day is today. And by “finicky”, as was the case with its predecessor, I was referring to its penchant for “rejecting batteries that other chargers accepted complaint-free.”

Truth be told, I can’t recall how it came into my possession in the first place, nor how long I’ve owned it (aside from a nebulous “really long time”). Whatever semblance of an owner’s manual originally came with the charger is also long gone; tedious searches of both my file cabinet and online resources were fruitless. There’s not even a company name or product code to be found anywhere on the outer device labeling, just a vague “Smart Timer Charger” moniker:

The best I’ve been able to do, thanks to Google Image Search, is come across similar-looking device matches from a company called “Vidpro Power2000” (with the second word variously alternatively referred to as “Power 2000”) listed on Amazon under multiple different product names, such as the XP-333 when bundled with four 2900 mah AA NiMH batteries:

and the XP-350 with four accompanying 1000mAh AAA batteries, again NiMH-based:

My guess is that neither “Vidpro Power2000” nor whatever retail brand name was associated with this particular charger was actually the original manufacturer. And by the way, those three plastic “bumps” toward the top of the front panel, above the battery compartment and below the “Power2000” mark, aren’t functional, only cosmetic. The only two active LEDs are the rectangular ones at the front panel’s bottom edge, seen in action in an earlier photo.

Anyhoo, after some preparatory top, bottom, and side chassis views as supplements to the already shared front and back perspectives:

Let’s work our way inside, beginning (and ending?) with the visible screw head in between the two foldable AC plug prongs:

Nope, that wasn’t enough:

Wonder what, if anything, is under the back panel sticker? A-ha:

There we are:

“Nice” unsightly blob of dried glue in the upper left corner there, eh?

No more screws, clips, or other retainers left; the PCB lifts away from the remainder of the plastic chassis straightaway:

As I noted earlier, those “three bumps” are completely cosmetic, with no functional purpose:

And speaking of cosmetics, the two-tone two-sided PCB is an unexpected aesthetic bonus:

As you may have already noticed from the earlier glimpse of the PCB’s backside, the trace regions are sizeable, befitting their hefty AC and DC power routing purposes and akin to those seen last time (where, come to think of it, the PCB was also two-tone for the two sides). But the PCB itself is elementary, seemingly with no embedded trace layers, therein explaining the between-regions routing jumpers that through-hole feed to the other side:

We’ve also finally found a product name: the “TL2000S” from “Samyatech”. My Google search results on the product code were fruitless; let me know in the comments if you had any better luck (I’m particularly interested in finding a PDF’d user manual). My research on the company was more fruitful, but only barely so. There are (or perhaps more accurately in this case, were) two companies that use(d) the “Samyatech” abbreviation, both named “Samya Technology” in full. One is based in Taiwan, the other is in South Korea. The former, I’m guessing, is our candidate:

Samya Technology is a manufacturer of charging solutions for consumer products. The company manufactures power banks, emergency chargers, mobile phone battery chargers, USB charging products, Solar based chargers, Secondary NiMH Batteries, Multifunction chargers, etc. The company has two production bases, one in Taiwan and the other in China.

The website associated with the main company URL, www.samyatech.com, is currently timing out for me. Internet Archive Wayback Machine snapshots suggest two more information bits:

- The main URL used to redirect to samyatech.com.tw, which is also timing out, and

- More generally, although I can’t read Chinese, so don’t take what I’m saying as “gospel”, it seems the company shut down at the start of the COVID-19 lockdown and didn’t reopen.

Up top is the AC-to-DC conversion circuitry, along with other passives:

And at the bottom are the aforementioned LEDs and their attached light pipes:

Back to the PCB backside, this time freed of its previous surrounding-chassis encumbrance:

That blotch of dried glue sure is ugly (not to mention, unlike its same-color counterparts on the other side that keep various components in place, of no obvious functional value), isn’t it?

The IC nexus of the design was a surprise (at least to me, perhaps less so to others who are already more immersed in the details of such designs):

At left is the AZ324M, a quad low-power op amp device from (judging by the company logo mark) Advanced Analog Circuits, part of BCD Semiconductor Manufacturing Limited, and subsequently acquired by Diodes Incorporated.

And at right? When I first saw the distinctive STMicroelectronics mark on one end of the package topside, I assumed I was dealing with a low-end firmware-fueled microcontroller. But I was wrong. It’s the HCF4060, a 14-stage ripple carry binary counter/divider and oscillator. As the Build Electronics Circuits website notes, “It can be used to produce selectable time delays or to create signals of different frequencies.”

This all ties to, as I’ve been able to gather from my admittedly limited knowledge and research, how basic battery chargers like this one work in the first place (along with why they tend to be so fickle). Perhaps obviously, it’s important upfront for such a charger to be able to discern whether the batteries installed in it are actually the intended rechargeable NiMH formulation.

So, it first subjects the cells to a short-duration, relatively high current pulse (referencing the HCF4060’s time delay function), then reads back their voltages. If it discerns that a cell has a higher-than-expected resistance, it assumes that this battery’s not rechargeable or is instead based on an alternative chemistry such as alkaline or NiCd…and terminates the charge cycle.

That said, rechargeable NiMH cells’ internal resistance also tends to increase with use and incremental recharge cycles. And batteries that are in an over-discharge state, whether from sitting around unused (a particular problem with early cells that weren’t based on low self-discharge architectures) or from being excessively drained by whatever device they were installed in, tend to be intolerant of elementary recharging algorithms, too.

That said, I’ve conversely in the past sometimes been able to convince this charger to accept a cell that it initially rejected, even if the battery was already “full” (if I’ve lost premises power and the charger acts flaky when the electricity subsequently starts flowing again later, for example) by popping it into an illuminated flashlight for a few minutes to drain off some of the stored electrons.

So… And again, as I mentioned back in September, a more “intelligent” (albeit also more expensive) charger such as my La Crosse Technology BC-9009 AlphaPower is commonly much more copacetic with (including being capable of resurrecting) cells that simplistic chargers comparatively reject:

And again, as I mentioned back in September, a more “intelligent” (albeit also more expensive) charger such as my La Crosse Technology BC-9009 AlphaPower is commonly much more copacetic with (including being capable of resurrecting) cells that simplistic chargers comparatively reject:

Some side-view shots in closing, including closeups: