Feed aggregator

Rio Tinto to progress gallium R&D project by constructing pilot plant in Québec

НН ІАТЕ. Історія та сьогодення

Цього року Навчально-науковий інститут атомної та теплової енергетики (НН ІАТЕ ), створений на базі теплоенергетичного факультету КПІ ім. Ігоря Сікорського, відзначає своє 95-річчя. Адже засновано його було ще 1931 року, коли у складі Київського енергетичного інституту (КЕІ) організували дві кафедри: парових двигунів і теплосилових установок, які стали основою для створення теплотехнічного факультету (ТФ), який з часом став теплоенергетичним (ТЕФ).

Soitec and NTU Singapore reporting results of research program into 6G connectivity

Emergency Screaming Detection: How AI Recognizes Human Screams and Saves Lives

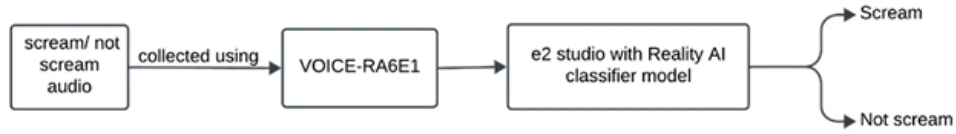

Courtesy: Renesas

Detecting human screams for help is important in disaster relief, security, and healthcare applications. Imagine being stuck in an elevator when the usual means of communication failed. An emergency screaming detection system can recognise the distress signal and immediately activate emergency protocols, such as alerting security personnel or triggering an alarm, to efficiently get help and save lives.

Renesas’ Reality AI Emergency Scream Detection is a machine learning (ML) model designed to identify human screams. This model isn’t just about recognising any loud noise; it’s finely tuned to discern distress calls (as a scream) from background sounds. This system will enable immediate dispatch for help, especially important in enclosed or isolated environments where safety is critical.

How does Emergency Screaming Detection work?

The emergency scream detection system is trained to differentiate different audio sounds based on the data collected. The steps involved in developing this machine learning model are as follows:

- Data Collection and Training: The model’s training begins with comprehensive data collection. A public dataset including a variety of audio samples is used. The “Scream” class, featuring intense nonverbal screaming sounds and screaming with words, is used to train the emergency scream detection system. To ensure the model distinguishes what isn’t a scream, a diverse range of sounds such as wind, ambient noise, normal conversation, singing, music, and clapping is also used from the same dataset.

- Feature Extraction: The next step is to extract meaningful features from the audio files that help the model recognise scream-specific patterns amidst various noises.

- Model Training: After selecting the best feature, a machine learning classifier is trained to distinguish between “scream” and “non-scream” audios. The training process involves adjusting the model parameters to minimise errors and enhance its performance.

By using these methods, the emergency scream detection system can be built to ensure emergency responses are swift, providing a vital safeguard in various environments.

Application Example

Audio signals are collected from the real-world environment to create the Renesas VOICE-RA6E1 Voice User Demonstration Kit. These audio signals are then processed by Renesas’ Reality AI-trained classifier model, which helps in distinguishing between “scream” and “non-scream” audio sounds.

The live testing of Renesas’ Emergency Scream Detection model is benchmarked with ≥90% accuracy for screams at a maximum distance of 2 meters from the testing board. The testing conditions also included background noises such as wind, elevator music, human conversations, baby cries, and ringing phones to determine distress signals while maintaining accuracy.

Easily Build the Application Example

Users can collect audio signals with Renesas’ e² studio IDE and integrate any AI model generated from Renesas’ Reality AI software. After collecting data from a public dataset*, deploy the Reality AI software’s tools to perform feature extraction, model training, and deployment of the model to C code.

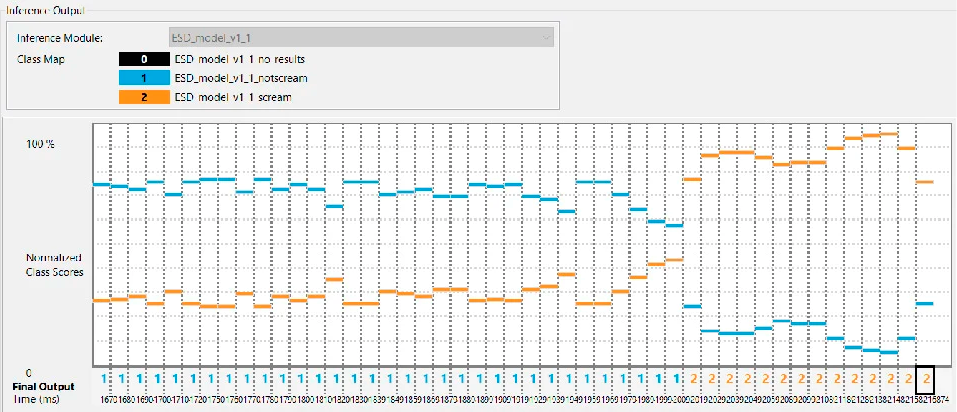

The deployed model can be integrated for live testing using the e² studio IDE. After integration, the model can be extensively tested in a live setting using the VOICE-RA6E1 board, and the live results can be visualised using the AI live monitor.

Experience the seamless and fast integration capabilities of Renesas’ Reality AI software and e² studio IDE in model training, deployment, and testing of an application.

Conclusion

The Reality AI Emergency Scream Detection application exemplifies the potential of machine learning in enhancing safety measures in various settings and demonstrates how users can employ Renesas’ technology to integrate advanced feature extraction, model training, and deployment with real-time response capabilities. The scalable Reality AI Tools can generate ML models for a wide range of Renesas MCU and MPU devices.

The post Emergency Screaming Detection: How AI Recognizes Human Screams and Saves Lives appeared first on ELE Times.

India’s Electronics Push: Ambition Is Clear. Execution Will Decide the Outcome

India’s electronics story has entered a decisive phase. The policy announcements of February 2026 — combined with export milestones and strategic partnerships — suggest that the country is attempting something far larger than incremental industrial growth. It is trying to reposition itself in the global technology hierarchy. But ambition alone will not secure that position. Execution will.

The Union Budget 2026–27 allocated ₹40,000 crore to strengthen domestic component manufacturing under the Electronics Components Manufacturing Scheme. This is a necessary correction. For years, India has excelled at assembling finished goods while importing critical components.

Simultaneously, India Semiconductor Mission 2.0 signalled a deeper commitment to building semiconductor capability across fabrication, assembly, and materials. The intent is clear: India does not want to remain at the lower end of the value chain.

The export data reinforces this shift. Smartphone exports have touched roughly $30 billion, with global leaders such as Apple and Samsung Electronics scaling manufacturing operations in India. This is not a small achievement. In less than a decade, India has moved from a peripheral manufacturing base to a meaningful node in global electronics supply chains.

Yet, the central question remains: Is India building depth — or scale without control?

Assembly success does not automatically translate into technological sovereignty. True leverage lies in advanced semiconductor fabrication, high-end equipment manufacturing, precision materials, and ownership of intellectual property. On these fronts, India still trails global leaders by a wide margin.

The partnership between Qualcomm and Tata Electronics in automotive electronics demonstrates progress in value-added manufacturing. But automotive modules, while strategically important, are not the same as owning leading-edge fabrication technology.

There is also a structural reality policymakers must confront: semiconductor ecosystems take decades to mature. They require uninterrupted capital flow, stable policy frameworks, reliable power, water security, efficient logistics, and depth in engineering. Any inconsistency could stall momentum.

The global semiconductor race is no longer an economic contest. It is a geopolitical war — one fought with export controls, subsidy regimes, technology blockades, and supply chain realignments. The United States has weaponised semiconductor policy through export controls and industrial subsidies. China has doubled down on domestic chip independence. Europe is pouring billions into sovereign fabrication capacity. Taiwan remains indispensable. South Korea protects its giants as strategic assets.

Semiconductors have become the oil of the digital century — and nations are securing supply at any cost.

What India is attempting is bold — and necessary. Electronics today underpin defence systems, AI infrastructure, mobility platforms, and digital economies. Countries that control semiconductor depth control strategic autonomy.

The danger is complacency born from export success. Hitting $30 billion in smartphone exports is impressive. But if core chips, advanced lithography systems, and high-value IP remain imported, strategic vulnerability persists.

India’s electronics sector is at a crossroads. The past month shows strong policy intent and rising industrial confidence. The next five years will test whether this momentum can be translated into irreversible capability.

The world is reorganising supply chains. India has an opportunity to claim a durable position. But the window will not remain open indefinitely. Ambition has been declared. Now comes the harder task — building capability that the world cannot bypass.

The next ten years will determine whether India becomes: a swing state in the global tech war, a protected assembly corridor or a sovereign semiconductor power. The chip war is not theoretical. It is unfolding in export controls, trade negotiations, and defence alliances.

The question now is whether it is prepared to fight at the highest technological tier — or remain a strategic subcontractor in someone else’s supply chain.

History will not remember the announcements. It will remember who controlled the chips.

Devendra Kumar

Editor

The post India’s Electronics Push: Ambition Is Clear. Execution Will Decide the Outcome appeared first on ELE Times.

India on the Road to Semicon Self-Reliance with Three More Plants

India to welcome three more semiconductor plants after PM Modi inaugurated Micron’s plant last week, on February 28.

Since the commencement of the India Semiconductor Mission in 2021, India has developed its semiconductor ecosystem exponentially, with four out of ten plants already approved and three more to be inaugurated in 2026 itself. The government further accelerated this by introducing catalyst initiatives like the PLI scheme.

With semiconductors being the core of any modern technology, the demand has grown multifold, and India is pioneering to become a competitive manufacturer for semiconductor to meet the global demand.

India has given approval to ten semiconductor plants in six states with an investment of about Rs 1.60 lakh crore.

As per government records, the approved list of semiconductor plants other than the recently inaugurated Micron plant is as follows:-

- Tata Electronics (Dholera, Gujarat): Semiconductor fab in partnership with PSMC, Taiwan.

- CG Power (Sanand, Gujarat): OSAT facility in partnership with Renesas & Stars.

- Tata Semiconductor Assembly and Test (TSAT) (Morigaon, Assam): Semiconductor packaging facility.

- Kaynes Semicon Pvt Ltd (Sanand, Gujarat): OSAT facility.

- HCL-Foxconn JV (Location TBD): Semiconductor packaging and testing.

- SiCSem Private Limited: Compound semiconductor manufacturing.

- 3D Glass Solutions Inc.: Advanced substrate manufacturing.

- Advanced System in Package (ASIP) Technologies: Assembly and testing.

- Continental Device India Private Limited (CDIL): Discrete semiconductor fab.

The evolving semiconductor landscape in India is expected to generate over two lakh jobs, secure supply chains, as well as strengthen the AI, EV, and defence sectors.

By: Shreya Bansal, Sub-Editor

The post India on the Road to Semicon Self-Reliance with Three More Plants appeared first on ELE Times.

Veeco books multi-system Lumina and Spector orders for InP datacom laser manufacturing

Board-in interconnects

| submitted by /u/1Davide [link] [comments] |

ams OSRAM completes sale of Entertainment & Industry Lamps business to Ushio for €114m

First Solar’s US GDP contribution to grow from $5.8bn in 2025 to $7.8bn in 2027

EPC highlights Gen 7 GaN for AI infrastructure and GaN ICs for robotics at APEC

A defunct Amazon Echo: Where did its acumen go?

A multi-day weather-induced, utility-instigated electricity cutoff thankfully left this engineer’s residence and its contents largely unscathed…with one geriatric smart speaker exception.

Last December’s high-wind-induced extended power outage thankfully didn’t cause notable damage to our home or its contents. But to say we escaped completely unscathed would still be a (slight) overstatement. When we returned home after Xcel Energy restored power, I noticed that several of our Amazon Echo devices—two second-generation Echo Dots:

and a first-generation Echo:

exhibited perpetually rotating topside-light patterns characteristic of an imperfect bootup:

I’ve occasionally encountered this misbehavior before with various Echo-family devices, and as in the past, power-cycling the two Echo Dots got them going again. But despite multiple attempts, both power- and reset switch-based, I couldn’t convince the Echo to resurrect itself:

Oddly enough, albeit presumably indicative of an underlying distributed-processing system architecture, the top-panel microphone mute button still seemed to operate as expected, at least from an LED-illumination response standpoint:

But the Echo never came online or, more broadly, was responsive to voice-command attempts. Not to mention the perpetually rotating topside light whose video you’ve already seen. That said, I’d been using it for a long time, and they’re apparently prone to such misbehavior sooner or later. And that said, its two same-generation siblings in the residence were still working fine, and the first-generation Echo doesn’t support Amazon’s latest Alexa+ enhancements anyway (the second-generation Echo I replaced it with, conversely, is Alexa+-cognizant).

At this point, I’ll reiterate something you’ve read from me in variously worded ways plenty of times before: when a device dies, it frequently then turns into a teardown candidate. I’d already disassembled the first-gen Echo before, for publication more than a decade ago, to be exact:

But as with my Tile Mate teardown a few months back, trying to figure out why a device has died is often reason enough for me to entertain a dissection revisit. Plus, in re-reading my earlier coverage, I was reminded that my teardown presentations have become more verbose (whether that word choice translates into “comprehensive” or “long-winded” is up to you to decide) in the last decade. And although I’m still primarily snapping photos using a smartphone, the integrated camera has gotten a significant upgrade in the intervening years. So…here goes!

Foot firstYou’ve already seen the reset switch accessible via a hole in the device’s rubberized “foot”:

Here’s another bottom-side closeup, this time of the various product markings, including the always-informative FCC ID (ZWJ-0823):

As was also the case last time, the “foot” (both here and in subsequent photos accompanied by a 0.75″ (19.1 mm) diameter U.S. penny for size comparison purposes) peeled right off:

exposing to view the circuit testing (and firmware programming, I’m also guessing) conductive pad array, along with four screw heads:

I suspect you already know what comes next:

Voilà. Our first, but definitely not our last, PCB is now exposed for visual perusal:

Its functions include internal power generation and management, along with analog-to-digital audio conversion and subsequent amplification for the main (combined midrange and tweeter) and subwoofer speakers. Not to mention the aforementioned hardware reset switch. Let’s next disconnect the associated cabling:

thereby enabling completion of the bottom assembly’s separation from the remainder of the device. To wit, keep in mind in viewing and analyzing both this and subsequent images that the Amazon Echo is currently oriented upside-down, i.e., it’s resting on its top edge:

A few more initial images of the PCB from various perspectives and proximities follow:

A bottom assembly flip-over first-time reveals the external power input connector:

And before continuing, I’ll supply a few additional power-related images and comments (power…supply…get it? Ahem). First off, here’s the “wall wart”:

also including closeups of its specs and “barrel” connector:

I’ve had a few second-generation “Dot” devices’ external power supplies fail in the past; the end result is either a flat-out refusal to start at all or a perpetual repetition of partial boots followed by abrupt restarts. In those cases, the consistent “fix” was straightforward and non-wasteful. Since the AC/DC converter with USB-A output was distinct from the USB-A to microUSB cable that fed the device, I could just swap in a replacement for the former and be up and running again in no time. Every time I did this, by the way, I wondered how many Echo Dots prematurely ended up in the landfill due to typical-consumer ignorance of both the exhibited issue’s root cause and simple resolution solution.

The Amazon Echo, as with subsequent-generation Echo Dots, is different: the AC/DC converter and power cable are one integrated unit. And I’d also yet to encounter an Echo-family power supply failure that presented itself as a partial boot followed by a “hang”. Nevertheless, my obvious first step was still to tether a multimeter to the power connector and confirm that I was measuring the expected voltage. And then, since this preliminary outcome wasn’t in and of itself definitive (the power supply could still be peak current-compromised, to the earlier partial-boot-and-restart scenario, and something that the light power supply loading by the multimeter wouldn’t expose), I borrowed a power supply from one of the other first-generation Echoes in the house and sadly confirmed that I still saw the same “hang” behavior as before.

IC detailsBack to the bottom of the device. Next, let’s remove the PCB from the assembly, an easily accomplished task:

Here, for comparisons sake, is the comparable PCB (and vantage point view) from my initial February 2016 teardown of the Amazon Echo:

Quoting from that earlier writeup:

At top is the DC power input jack. At bottom is the ribbon cable connector. On the right are the two speaker connectors, one white and the other black. Near the center is a Texas Instruments TLV320DAC3203 stereo audio codec (PDF). On the far left is Texas Instruments’ TPS53312 step-down converter. And the PCB is otherwise covered with assorted large inductors, “can” capacitors, and other passives.

The only thing I might add on revisit of my earlier prose is mention of the multi-LED cluster at center of the PCB, which works in conjunction with the clear plastic lightpipe you probably noticed in the earlier device interior shot, taken post-bottom assembly removal:

to route the device’s power and connectivity status to a backside indicator located above the indent for the power cord. In retrospect, I wish I would have noted not only the perpetually rotating LED pattern up top but also the information communicated (or not) by this secondary LED set, as it might have assisted in diagnosing whatever had gone awry with the Echo.

Next are some side views:

And now for the PCB’s other side:

once again accompanied by that of its decade-plus ago predecessor:

along with a requote of my prior prose:

Flip the PCB over and the comparatively sparse underside contains several notable elements, beyond even more passives. At top is, again, the dual screw-reinforced backside of the DC power input jack. At bottom is the system reset button. In between them are the previously mentioned test points. And in the middle of the left half of the PCB is the audio amplifier, again from Texas Instruments (the TPA3110D2 Class D Stereo device, to be precise).

You more recently saw mention of the TPA3110’s higher power, PFFB-supportive successor, Texas Instruments’ TPA3255, within a class D-based audio amplifier teardown I did last fall.

Symmetrical sound redirectionOnward. With the lightpipe out of the way, the conical black plastic piece underneath it (as currently oriented; above it in normal operation) slides right out:

Below it is the main full-range speaker, handling all but the lowest audio frequencies, which instead route to the subwoofer we’ll see shortly:

The plastic piece’s contours, with the cone end pointed toward the speaker (which normally points downward), uniformly redirect generated sound out the mesh sides of the device:

At this point, speaking of “mesh”, let’s press “pause” on the speaker and redirect our attention to sliding that metal mostly-mesh outer chassis off instead:

Take the inner assembly:

Rotate it horizontally by 180°, and another PCB appears:

The connector at bottom in this upside-down (versus norm) orientation mates to a flex cable that also routes to the top assembly:

And the one at the other end mates to the earlier-seen flex cable that also ends up at the bottom assembly:

Let’s cut away the foam surrounding much of the insides, so we can see what’s underneath it:

That’s more like it:

There’s that RFID tag again, which I’d first showcased a decade-plus ago:

Here’s our first glimpse of the subwoofer which, like the full-range speaker you saw earlier, points downward in the device’s normal operating orientation. The full-range speaker’s rear housing, which you’ll see shortly, is rounded, and akin to the cone-shaped piece ahead of the full-range speaker, similarly redirects the subwoofer’s primary output out the sides:

And here once again is what I’m calling the “digital PCB”, now free of any foam obscurant:

See those four screw heads? Buh-bye:

In removing one of them, which promptly and firmly re-attached itself to the side of the internal assembly, I was reminded that there’s a sizeable subwoofer-inclusive magnet inside:

As before, I’ll start with the PCB’s outside:

Next is its decade-plus ago, still attached, 90°-rotated-in-comparison counterpart’s image:

And a reprint of the prior associated prose (perhaps obviously referencing locations in the initial teardown’s photo orientation):

In the middle, toward the top is Texas Instruments’ DM3725CUS100 “digital media processor” SoC. It’s fairly diminutive in processing chops, compared to the application processors in modern smartphones and tablets, containing only a single-core 1 GHz ARM Cortex-A8 CPU. My best guess, therefore, is that it primarily handles the Echo’s speech recognition features, with “heavier lifting” redirected to Amazon’s servers via the device’s Wi-Fi connection. Speaking of which, the shiny-packaged IC below the DM3725CUS100 is a Qualcomm Atheros QCA6234X-AM2D Wi-Fi and Bluetooth module, also found in Amazon’s Fire TV and Fire HD tablet. The corresponding antennas are etched into the PCB, on either side.

Volatile and nonvolatile memory are a necessity, of course, and in this case they respectively take the form of a Samsung K4X2G323PD-8GD8 1 Gbit 200 MHz x32 mobile DDR SRAM (in the upper left corner) and Sandisk SDIN7DP2-4G 4 GByte iNAND embedded flash memory drive (below it). A standalone power management IC is also pretty much a guarantee in a product like this, and the Echo doesn’t disappoint; on the right edge of the PCB is a Texas Instruments TPS65910A1.

Next is another set of PCB side shots; note that as with its bottom-located predecessor, this particular board is impressively “meaty” from a thickness standpoint:

Finally, what’s underneath? A decade back, I wrote, “I didn’t bother showing you the underside of this PCB, by the way, because there’s nothing really to see … unless you’re into a bunch of additional passives, that is.” As you’ll see, “a bunch of” was arguably even overstating reality:

To the summitOne more PCB to go; the seemingly still-functional one up top, starting with the removal of a side screw:

The top assembly’s now gone:

More accurately, I’d just momentarily set it aside:

Four more screws to remove (how many times have I already said that in this piece?):

And now a pictorial sequence of the steps necessary to fully-as-possible expose the PCB to view:

Last time, I wrote: “I didn’t bother with a shot of the underside of the PCB; the only contents of note are switches corresponding to the top-side microphone-mute and device-setup buttons.” This time, I’m instead going the extra mile for you, dear readers:

See, like I said before; just switches:

The other side of the PCB, of which you’ve already caught several glimpses, is more interesting:

Here’s the image of that same PCB (and side of it) from last time, once again notably rotated 90 degrees as compared to the new version:

Regarding the gear structure in one corner, I previously said that “Echo contains a rotating upper “cuff” which, among other things, acts as a manually operated alternative to voice command-driven volume up/down operations.” And the gear? It “provides cuff position and speed-of-rotation information.”

And what about the various visible ICs? Again, I requote (again, with location references to the original version of the photo, not the newer one):

Toward the top is a humble Texas Instruments SN74LVC74A dual positive-edge-triggered D-Type flip-flop (ironically the largest IC on this particular PCB). Toward the center are four Texas Instruments TLV320ADC3101 stereo ADCs. They surround one of the seven microphones, at center in gold. And they are surrounded by four Texas Instruments LP55231 9-output LED drivers. The other six microphones are symmetrically located along the rim of the PCB; one of them isn’t visible in the photo, obscured by the ribbon cable. And on either side of each of those edge-located microphones is an LED, twelve total in the design.

Transducers reduxNow let’s return to those two speakers—main and subwoofer—that you initially saw earlier. A decade-plus ago and regarding the foam seen surrounding the internal assembly after removing the mostly-mesh metal outer chassis, I wrote:

Underneath the thin black fabric layer surrounding the chassis is the woofer, along with its corresponding bass reflex port. To see them in detail, check out iFixit’s website; the electronics aspects of the design were my primary focus. The fabric’s purpose may be at least in part to diffuse the speakers’ outputs, thereby delivering the 360º sound that Amazon promotes. It may also dampen vibration at high volume.

This time, curiosity got the better of me, and I decided to peruse them for myself, sharing the images with you in the process. The first step, however, was to finish removing the main speaker. Hey, look. Four more screws!

The rounded rear of the main speaker’s acoustic suspension enclosure, as mentioned earlier, uniformly redirects the subwoofer’s primary sound output around the mesh sides of the device.

Speaking of the subwoofer…

And, last but not least, the curiously shaped (as you’ll soon see) bass reflex structure, intended to boost the subwoofer’s low frequency efficiency:

You’ve actually seen its associated port already, in one of the post-foam-removal internal assembly side shots. Here’s a closeup:

Remove the two screws whose heads are visible in the prior photo:

And the bass reflex structure then slips right out the Echo’s now-speakers-less bottom end (in normal operation; top as currently upside-down oriented):

Wutdunit?

(why yes, I did just create my own word)…

Unfortunately, unless you saw an old-vs-new teardown disparity I’d overlooked in any of the PCB photos I’ve shared here (a bulging capacitor, perhaps?), we’re left with the same question I posed at the start of this writeup: what caused this Amazon Echo to fail? The power subsystem in the bottom assembly seems to still be intact, given that the top assembly’s various LEDs and microphone mute switch continue to function (likely removing the top assembly from the root-cause list as well). I doubt that a failure in either/both the bottom assembly’s audio subsystem digital-to-analog and amplification stages would suffice to bring the device completely to its knees, either.

That leaves what I previously referred to as the “digital PCB”. A corrupted firmware image, perhaps the result of power loss mid-update, is one possibility. While the Echo was still present in my list of activated (albeit in this case, not found) devices, before I removed it in an ultimately fruitless attempt to fully factory-reset and then revive it, its settings in the Alexa app indicated that a firmware update was pending. I initially discounted this firmware-corruption possibility because:

- Amazon certainly wouldn’t design a device that “bricked” so easily, absent any sort of user-friendly recovery scheme…would it?(??!!!!)

- And at the time, my other two, still-functional first-generation Echoes’ settings displayed the exact same “firmware update available” messages. I therefore assumed they were bogus remnants of the first-generation Echo’s dearth of Alexa+ support.

But in re-looking at their settings just now, those messages are now gone. There’s no user-controlled way to manually initiate a firmware update; Amazon automatically “pushes” them (presumably at a time when it senses that a given device isn’t in use, for example). So…maybe?

The other, more benign possibility is simply that some circuit on that particular (or another) board has “gone south”, taking the entire device down with it. Nearing 3,000 words in, I’m going to wrap up at this point and turn the keyboard over to you for your theories and broader thoughts on this teardown in the comments!

—Brian Dipert is the Principal at Sierra Media and a former technical editor at EDN Magazine, where he still regularly contributes as a freelancer.

Related Content

- Preemptive utilities shutdown oversight: Too much, too little, or just right?

- Amazon and Google: Can you AI-upgrade the smart home while being frugal?

- Teardown: Amazon’s Echo voice-activated virtual assistant

- A hard-life Tile Mate goes under the knife

The post A defunct Amazon Echo: Where did its acumen go? appeared first on EDN.

"Снігові барси" з Київської політехніки

"Сніговий барс" в альпінізмі – це почесне звання, що з середини 1960-х присвоювалося в срср за сходження на найвищі вершини країни – семитисячники. Без балонів з киснем, без носильників, з неоковирним важким спорядженням, у валянках і в самотужки пошитому одязі ентузіасти долали льодові кілометри гірських схилів. Лише в 1990-х з'явилося легке і надійне оснащення, інноваційні матеріали. Серед володарів жетона "Підкорювач найвищих гір" – і плеяда випускників Київської політехніки. Назвемо їх.

eevBLAB 139 - The Youtube Copyright System is BROKEN

Upcoming years to Bring Boom for Semiconductors and Electronics

Union Minister for Electronics and Information Technology Ashwini Vaishnaw on Sunday encouraged Gujarat to develop itself as a global hub for data-centres to capture data-hosting opportunities from across the world while speaking at the Gujarat SemiConnect Conference 2026 in Gandhinagar.

The Minister highlighted the growing importance of the AI, Semiconductors, and Electronics Manufacturing trio in the coming years. With the world surging in the production of advanced electronics, the above three are beginning to take centre stage, and India must grasp this opportunity to leverage its advantage of skilled population, clubbed with the fertile ecosystem for growth.

Gujarat has great potential to grow as a data centre for the world with its surplus power and availability of clean energy, presenting a bright opportunity for the establishment of such facilities in the state.

The event was attended by other prominent dignitaries like Chief Minister of Gujarat, Shri Bhupendra Patel and Deputy Chief Minister Shri Harsh Sanghvi. The three leaders unveiled the new ‘Science, Technology and Innovation (STI) 2026–31’ Policy at the event.

Organised by the state government’s Department of Science and Technology, and inspired by the Prime Minister’s vision, the conference carried the theme “Gujarat: India’s Silicon Gateway”, aimed at fostering strategic collaboration between high-tech chip manufacturers and local industry.

The Chief Minister described the conference as the “right job at the right time,” highlighting how Prime Minister Modi’s inauguration of the Micron plant at Sanand has ignited a technological revolution for the country. He added that the conference, which was launched immediately after that historic milestone, will demonstrate the state’s readiness to build a semiconductor ecosystem, attract global partners, and fulfil the vision of an Aatmanirbhar Bharat through research, innovation, and supply chain localisation.

India is developing its semiconductor atmosphere, with Dholera Special Investment Region (SIR) in Gujarat being developed as India’s premier ‘Semicon City’ and a global hub for electronics manufacturing. Located near Ahmedabad, it is the site of India’s first commercial semiconductor fabrication unit by Tata Electronics.

By: Shreya Bansal, Sub-Editor

The post Upcoming years to Bring Boom for Semiconductors and Electronics appeared first on ELE Times.

R&S Propels 6G Readiness With FR1–FR3 Carrier Demonstration

Rohde & Schwarz and Qualcomm Technologies, Inc. have reached another pivotal milestone in 6G research and ecosystem readiness, successfully demonstrating carrier aggregation across FR1 and FR3 frequency ranges. The joint achievement is showcased live at MWC Barcelona 2026.

At MWC Barcelona, Rohde & Schwarz and Qualcomm Technologies present a live demonstration at the Rohde & Schwarz booth (5A80) that aggregates a mid-band channel around 2.5 GHz (FR1) with an upper mid-band channel around 7 GHz (FR3), using 4×4 MIMO on both bands and higher-order modulation. With this setup, the two companies validate end-to-end device behaviour across the aggregated spectrum.

At the heart of the test setup is the CMX500 one-box signalling tester from Rohde & Schwarz, extended with the new RFU18 board to provide coverage up to 18 GHz. RFU18 is a modular hardware upgrade for the CMX500 platform, giving customers a straightforward, cost-effective path to extend existing testers towards 6G. As the device under test (DUT), Qualcomm Technologies provided a Mobile Test Platform (MTP) powered by the Qualcomm® Modem-RF System, enabling comprehensive validation of RF performance and protocol behaviour across the aggregated FR1 and FR3 bands.

The FR3 frequency range (7.125 to 24.25 GHz) has been identified by industry and research as a “sweet spot” for combining wide-area coverage with high capacity. FR3 in terrestrial networks (TN) and non-terrestrial networks (NTN) is expected to support demanding applications such as eXtended Reality (XR), connected and autonomous vehicles and industrial automation. By validating FR3 as an additional frequency range for future networks, the partners are helping accelerate 6G development and ecosystem readiness.

Goce Talaganov, Vice President Mobile Radio Testers at Rohde & Schwarz, said: “Through our ongoing collaboration with Qualcomm Technologies, we continue to push the boundaries of wireless communications. As the ecosystem moves toward 6G, we’re showing how easy innovation can be with our test equipment. In response to customer demand, we are extending the CMX500 platform to 18 GHz – so that our customers gain headroom for FR3 evolution and higher-frequency emissions and harmonic testing.”

Tingfang Ji, Vice President of Engineering and Head of 6G Research at Qualcomm Technologies, Inc., said: “Our collaboration with Rohde & Schwarz highlights the importance of aggregating existing spectrum bands with new 6G spectrum in FR3 to establish 6G as the high-efficiency digital infrastructure for the 2030s. By validating new spectrum layers and advanced RF capabilities using our MTP powered by Qualcomm Modem-RF System, we are accelerating innovation across the ecosystem and helping prepare devices and networks for the next-generation of services.”

Future-ready CMX500 platform for 6G:

The CMX500 is a modular, powerful and future-proof one-box signalling tester enabling comprehensive multi-technology testing – from RF to protocol – across all relevant frequency ranges (FR1, FR2 and FR3). All existing CMX500 platforms can be enhanced with the new RFU18 board to extend frequency coverage and capabilities without replacing the entire system, offering users a simple upgrade path.

Engineered for data rates up to 20 Gbps, the CMX500 is one of the most versatile mobile device test platforms, supporting wide dynamic range, 4096QAM and up to 16 device antenna ports for advanced spatial multiplexing. With its multi-band capabilities, it covers LTE and NR in SA/NSA modes, NR-NTN, NB-NTN, Direct-to-Cell (D2C/DTC) testing, and WLAN, including Wi‑Fi 7 and future Wi‑Fi 8.

The post R&S Propels 6G Readiness With FR1–FR3 Carrier Demonstration appeared first on ELE Times.

КПІ на «Дистанції безпеки»: дистанційні системи для гуманітарного розмінування

КПІ ім. Ігоря Сікорського став майданчиком і активним учасником заходу «Дистанція безпеки», де йшлося про застосування дистанційних систем для виявлення вибухонебезпечних предметів у протимінній діяльності. Такі технології мінімізують ризики для людей і пришвидшують обстеження територій.

Navitas exhibiting solutions for AI data-center, grid and energy infrastructure, performance computing, and industrial electrification

🚀 Інженерний конкурс «Збудуй свою мрію» для учнів 8–11 класів

Мрієш створити власний літальний апарат? Час діяти! Навчаєшся у 8–11 класі та цікавишся технікою або авіацією? Інженерний конкурс «Збудуй свою мрію» — це можливість розробити та зібрати власний літальний апарат разом із досвідченими менторами.

ROHM and Suchi Semicon Establish a Strategic Semicon Manufacturing Partnership in India

ROHM and Suchi Semicon have announced the establishment of a strategic semiconductor manufacturing partnership in India.

This collaboration reflects a shared commitment to strengthening semiconductor manufacturing capabilities in India while supporting the requirements of both domestic and global markets. By combining ROHM’s device technology expertise and global semiconductor leadership with Suchi Semicon’s manufacturing capabilities and operational execution, the companies aim to build a reliable and scalable manufacturing framework aligned with evolving industry needs.

This partnership supports the expansion of semiconductor manufacturing capabilities in India (aligned with the “Make in India” objective) while maintaining global standards of manufacturing excellence. The collaboration aims to enhance supply chain resilience and provide customers with trusted manufacturing solutions.

Specifically, ROHM is considering the outsourcing of back-end processes for power devices and IC products to Suchi Semicon and has begun technical evaluations toward potential mass production shipments starting in 2026. Through these efforts, ROHM aims to build, in collaboration with Suchi Semicon, an early-stage manufacturing framework in India that aligns with the expected industry ramp-up in the coming years.

Furthermore, ROHM and Suchi Semicon will share a roadmap to expand the range of locally manufactured packages, thereby broadening the scope of collaboration between the two companies.

The partnership between ROHM and Suchi Semicon will extend beyond semiconductor manufacturing. Both companies recognise the growing expectations from customers across diverse sectors for locally manufactured semiconductors for the Indian market and will jointly pursue new business development opportunities to meet this demand. In addition, the collaboration will leverage Suchi Semicon’s strong local marketing expertise to conduct joint marketing initiatives that enhance visibility and customer engagement. Importantly, the alliance is not limited to these areas alone; ROHM and Suchi Semicon are committed to exploring further avenues of cooperation, ensuring that the partnership evolves into a comprehensive and long-term alliance that supports the sustainable growth of India’s semiconductor industry over time.

The post ROHM and Suchi Semicon Establish a Strategic Semicon Manufacturing Partnership in India appeared first on ELE Times.