Новини світу мікро- та наноелектроніки

Wifi Controlled, LED Matrix via Pico W, Only one GPIO pin required!

| The website used to control the LED Matrix Source code for the circuit board (via tscircuit) Server and MicroPython Source: https://github.com/tscircuit/led-matrix-server/tree/main [link] [comments] |

CES 2025: Moving towards software-defined vehicles

Major CES 2025 theme: SDVs

Major CES 2025 theme: SDVs

Software-defined vehicles (SDVs) are a big theme at CES this year, shifting vehicles from hardware-centric upgrades to over the air (OTA) software upgrades. In order to do this, vehicle subsystems must rely on a, more or less, generic processing platform that can perform a wide variety of functions to serve the various aspects of a car. As shown in Figure 1, TI’s approach to this is shifting from a “domain” architecture to a “zonal” one where ECUs that were once custom-tailored to specific domains (e.g., powertrain, ADAS, infotainment, body electronic and lighting, passive safety) are now more location, or zone-, -based to reduce weighty wire harnessing and improve processor speeds.

Figure 1 Traditional domain versus zone architecture. Source: Texas Instruments

TI’s radar sensor, audio processors, Class-D amplifierTI’s automotive innovations are currently focused in powertrain systems; ADAS; in-vehicle infotainment (IVI); and body electronics and lighting. The recent announcements fall into the ADAS with the AWRL6844 radar sensor as well as IVI with the AM275 and AM62D processors and the class-D audio amplifier.

ADAS: passenger safety solutionThe AWRL6844 radar sensor uses 60-GHz millimeter-wave (mm-wave) with a 4×4 antenna array and edge AI models running on an on-chip TI-specific accelerator and DSP to support several in-vehicle safety measures including occupancy monitoring for seat belt reminders, child presence detection, and intrusion (Figure 2). Presently, OEMs resort to a combination of in-seat weight sensors, two UWB sensors for front-row and back-row child presence detection, and an ultrasonic intrusion module for the same direct-sensing safety measures, directly tracking human activity such as respiration, heartbeat, movement, etc.). The technology is designed to assist OEMs in meeting evolving regulatory safety requirements such as the Euro new car assessment program (NCAP) advanced that offers rewards to manufacturers for implementing advanced safety technologies as a means to complement its established star rating system. Yariv Raveh, the vice president and business unit management of radar stated, “In 2025 the Euro NCAP requirement for child presence detection will only award points for a direct sensing system and in the near future, the in-cabin sensing system must accurately distinguish between a child and an adult in order to provide a good user experience.”

Figure 2 A block diagram of TI’s AWRL6844 radar sensor and the three vehicle modes that the sensor can assist with (seat belt reminder, child presence detection, and intrusion detection). Source: Texas Instruments

IVI: Premium audio solutionSome of the features of the new AM275x-Q1 and AM62D-Q1 processors are the integration of two vector-based C7x DSP cores, multiple Arm cores, on-chip memory, an NPU accelerator, and audio networking with Ethernet AVB. The differences between the processors is highlighted in Figure 3. “Tier 1 suppliers must elect the appropriate processing components to meet all of their customer needs across their fleets. So, our answer is to provide two different architectures to give engineers the flexibility to choose across the range of use cases, all using the same audio processing family where engineers can design standalone and integrated premium audio systems across a range of performance levels with minimal additional hardware and software investment,” said Sonia Ghelani, TI’s product line manager for signal processing MCUs. The company is actively working with customers to incorporate AI into the audio signal chain for unique solutions in applications such as active noise cancellation (ANC) and road noise cancellation (RNC).

Figure 3 The AM275x DDR-less MCU and AM62D DDR-based process for premium audio in IVI applications. Source: Texas Instruments

IVI: Class-D audio amplifierThe TAS6754-Q1 class-D amplifier (Figure 4) is meant to assist engineers with implementing TI’s “1L” modulation scheme, a technology that lowers the inductor count per audio channel to one (hence the phrase “1L”). Modern vehicles can embed well over 20 speakers and, in an effort to reduce size, weight, and cost, class-D amplifiers are being used for their higher power efficiency and lower thermal dissipation. However, these amplifiers generally require two LC filters per audio channel to attenuate high frequency noise. “1L maintains class-D performance while reducing component count and cost, allowing the premium audio system to grow in terms of speakers and mics,” added Sonia Ghelani.

Figure 4 Sample vehicle speaker and mic distribution as well as a sample block diagram of an audio signal chain including TI’s class-D amplifier. Source: Texas Instruments

Blurring the lines between IVI and ADASOne major discussion during the press briefing involved the industry trend of integrating ADAS and IVI functions on a single SoC. “So today we see that they’re in two separate boards, however, more and more we’re seeing that they end up being in the same board,” said Mark Ng, TI’s director of automotive systems. Sonia Ghelani added with an example of an overlap between ADAS and IVI functions, “these chimes and seat belt reminders are ADAS requirements that fall into the audio domain. As we move into a world of software-defined cars with more zonal architectures, you’ll continue to see an overlap between the two.” She continued, “For TI it’s important that we understand exactly what the customer is trying to build so that we don’t silo these systems in one bucket or another, but rather understand what problems the customer is trying to solve.”

Aalyia Shaukat, associate editor at EDN, has worked in the design publishing industry for six years. She holds a Bachelor’s degree in electrical engineering from Rochester Institute of Technology, and has published works in major EE journals as well as trade publications.

Related Content

- Power Tips #136: Design an active clamp circuit for rectifiers at a high switching frequency

- Collaboration drives innovation in software-defined vehicles

- AI algorithms on MCU demo progress in automated driving

The post CES 2025: Moving towards software-defined vehicles appeared first on EDN.

A two transistor sine wave oscillator

Figure 1 shows a variation on a sine wave oscillator, it uses just two transistors and a single variable resistor to set the frequency.

Figure 1 Just a couple of components are needed for a simple tunable sine wave oscillator.

Figure 1 Just a couple of components are needed for a simple tunable sine wave oscillator.

Wow the engineering world with your unique design: Design Ideas Submission Guide

The section around Q1 is a multiple-feedback-bandpass-filter (MFBF). The usual embodiment of this type of filter is shown in Figure 2.

Figure 2 A standard implementation of a MFBF.

The formulas for these filter can be found in almost any textbook (where C = C1 = C2):

![]()

![]()

Please note that the center frequency, among others, is determined by the resistance of R3. The gain of the filter is determined by the ratio of R2/R1 in such a way that Av = -R2/(2*R1). Usually this filter is implemented around an operational amplifier, it can also be implemented around an inverting transistor amplifier. However, because of the limited open-loop gain of the latter, the gain will be lacking at the higher frequencies.

The section around Q2 is an inverting amplifier, with an unloaded gain set by R8/R7. D1 and D2 together with R8 form a clipper to make sure that the signal offered to the MFBF is of constant level.

At the center frequency of the filter, the phase-shift is 180°. Together with the 180° phase shift of Q2 there is a total 360° phase shift at this frequency.The loop gain is >1 due to the ample gain of Q2. Thus, Barkhausen’s criteria are met.

The relative soft clipping of D1 and D2 together with the filtering of Q1 limits the amount of harmonics in the output signal. The passive components around Q1 determine the center frequency.

With the current values, the frequency can be set between 498 Hz and 1230 Hz by changing R3 between 1k and 6k. At the same time the output amplitude changes from 1.28 Vpp to 0.68 Vpp. The output shows around ~1% distortion (Figure 3).

Figure 3 The scope image shows the oscillator output at circa 1 kHz.

A variation in the supply voltage from 9 V to 12 V causes a frequency variation of only 2 Hz and a variation of output amplitude from 0.80 Vpp to 0.86 Vpp.

Cor van Rij blew his first fuse at 10 under the close supervision of his father who promptly forbade him to ever work on the house mains again. He built his first regenerative receiver at the age of 12 and his boys bedroom was decorated with all sorts of antennas and a huge collection of disassembled radios took up every horizontal plane. He studied electronics and graduated cum laude. He worked as a data design engineer and engineering manager in the telecom industry. And is working for almost 20 years as a principal electrical design engineer, specializing in analog and RF electronics and embedded firmware. Every day is a new discovery!

Related Content

- Simple 5-component oscillator works below 0.8V

- Ultra-low distortion oscillator, part 1: how not to do it.

- Clapp oscillator

- Oscillators: How to generate a precise clock source

- Clapp versus Colpitts

The post A two transistor sine wave oscillator appeared first on EDN.

CES 2025’s sensor design highlights

Sensing solutions—a vital ingredient in automotive, consumer and industrial applications—are prominent features in the offerings displayed at CES 2025 held in Las Vegas, Nevada on from 7 to 10 January. That encompasses sensing solutions packed into system-on-chip (SoC) devices as well as hardware components meshed with sensor fusion algorithms.

But the most exciting foray in this year’s sensor parade at CES 2025 relates to how artificial intelligence (AI) content is incorporated into sensing designs.

Read the full story published at EDN’s sister publication, Planet Analog.

Related Content

- MEMS group targets IoT sensor design

- Key design considerations, future of IoT sensors

- A new era in electrochemical sensing technology

- High-Performance Design for Ultrasound Sensors

- Designer’s Guide to Industrial IoT Sensor Systems

The post CES 2025’s sensor design highlights appeared first on EDN.

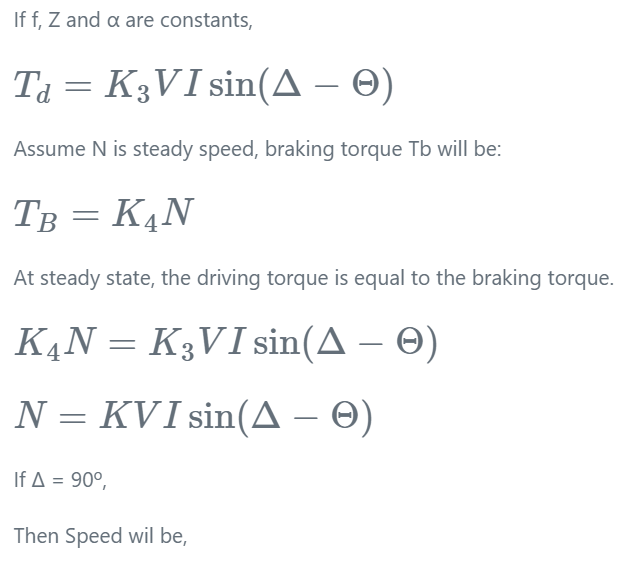

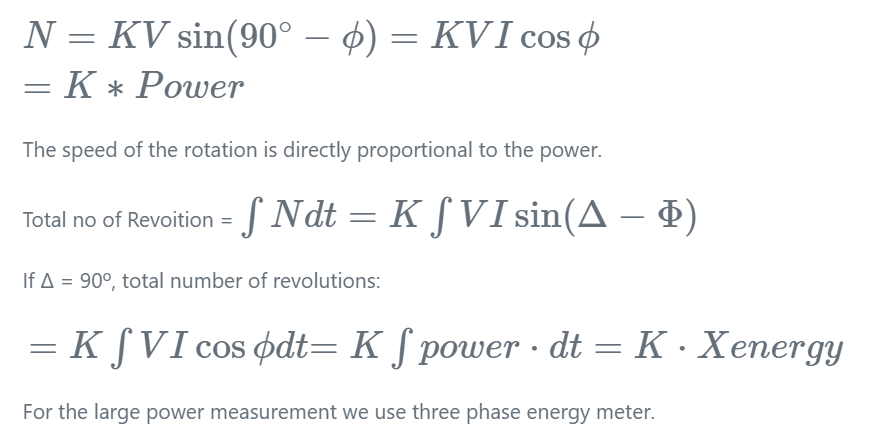

Energy Meter Definition, Types, Working, Construction & Diagram

An energy meter is a device that measures the electrical energy consumption in homes, commercial establishments, or industrial settings. It records the total energy usage, usually in kilowatt-hours (kWh), which is then used to calculate electricity bills. Energy meters play a vital role in managing energy consumption, ensuring accurate billing, and supporting energy efficiency measures. They are an essential part of modern electrical systems and are commonly found in homes, offices, factories, and other establishments.

Types of Energy Meters

Energy meters are classified into several types based on their design, application, and method of measurement. Here are the main types:

- Electromechanical Energy Meters (Analog Meters): These meters are the traditional type and have been in use for many years. They operate using a mechanical movement, which is driven by the flow of current. The meter features a rotating disc that spins as a result of the current flowing through it. The movement of the disc turns the dials, indicating the amount of electrical energy consumed. While they are durable and reliable, they have limitations such as less precision, difficulty in remote reading, and susceptibility to tampering.

- Electronic Energy Meters (Digital Meters): Electronic energy meters are more advanced and have largely replaced electromechanical meters in modern systems. They use digital technology to measure and record energy consumption. These meters consist of a microcontroller that processes the input from voltage and current sensors and displays the energy consumed on a digital screen. Digital meters offer greater accuracy, easy integration with remote reading systems, and are tamper-resistant.

- Smart Energy Meters: Smart energy meters are a newer, advanced type of digital meter that not only measure energy consumption but also allow for two-way communication between the meter and the utility company. These meters enable utilities to monitor usage in real-time, track energy trends, and even remotely disconnect or reconnect the service. Smart meters play a critical role in modern smart grids, helping consumers optimize energy usage and improving grid management.

- Prepaid Energy Meters: These meters are commonly used in locations where consumers wish to pay for energy before using it. The consumer credits the meter with a certain amount of energy, and once the credit is used up, the supply is disconnected. Prepaid meters are widely used in residential areas and allow for better control over energy costs.

- Three-Phase Energy Meters: These meters are used for measuring energy consumption in three-phase electrical systems, which are commonly found in industrial and commercial applications. Three-phase energy meters are more intricate and designed to manage larger electrical loads. They provide accurate measurements of energy consumption in systems with multiple phases.

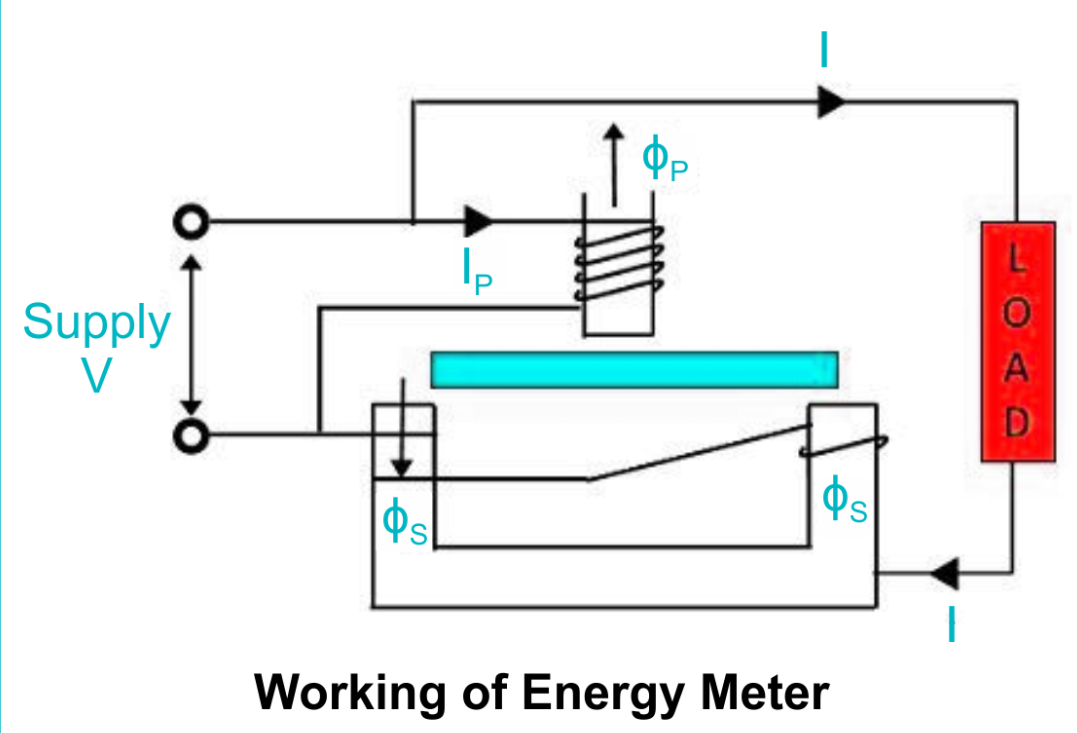

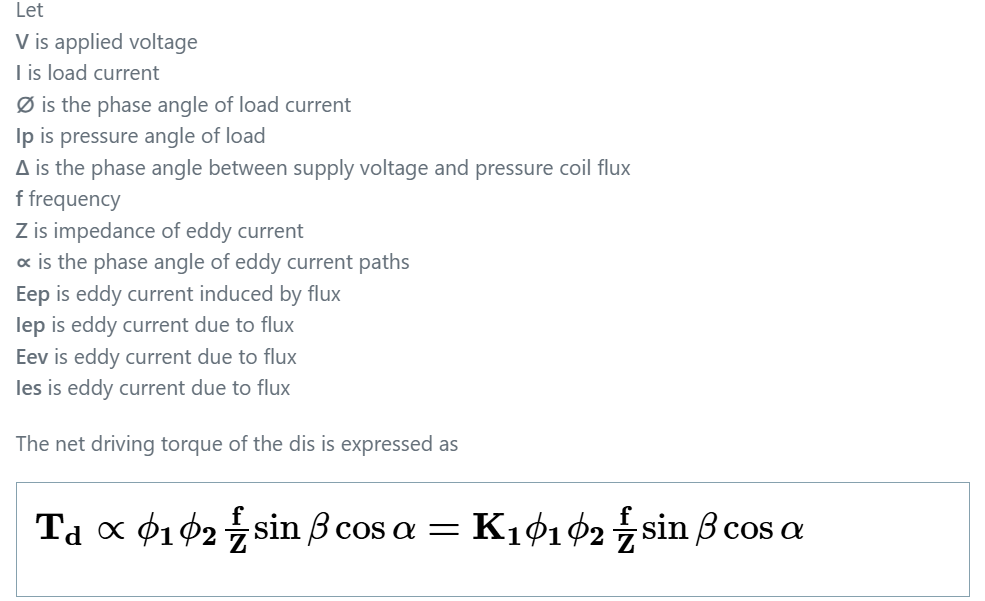

Working Principle of Energy Meter

The working principle of an energy meter involves the conversion of electrical energy into mechanical energy or directly into a digital signal. The operating principle differs based on the type of meter used. Here is a basic explanation of the working principles for electromechanical and electronic energy meters:

- Electromechanical Energy Meter:

- Electromagnetic Induction: The core working principle of electromechanical meters is electromagnetic induction. When current flows through a conductor placed in a magnetic field, it experiences a force that makes it move. In an energy meter, the current-carrying coil is placed in the magnetic field created by a permanent magnet or another coil, causing a rotating disc.

- Rotation of Disc: The speed at which the disc rotates is proportional to the power consumed. This rotation is mechanically linked to the dials or counters that indicate the energy usage.

- Friction Brake: A brake mechanism is applied to the disc to limit its speed, ensuring that it does not rotate too quickly, and the readings remain accurate.

- Electronic Energy Meter:

- Voltage and Current Sensing: Electronic meters use voltage and current sensors to continuously measure the electrical parameters of the system.

- Digital Conversion: The measured analog signals (voltage and current) are fed into an analog-to-digital converter (ADC) that transforms the continuous signals into discrete digital signals.

- Microcontroller Processing: A microcontroller processes the digital signals, calculating the energy consumed in real-time. The calculated data is shown on a digital display and saved for later reference.

Construction of an Energy Meter

The construction of an energy meter can vary depending on the type (electromechanical, electronic, or smart). However, the general components include the following:

- Current Coil: This coil is placed in series with the load and carries the current to be measured. It generates a magnetic field that interacts with the magnetic field of the voltage coil, producing a mechanical torque in the case of electromechanical meters.

- Voltage Coil: The voltage coil produces a magnetic field that interacts with the one created by the current coil. The voltage coil generates a magnetic field that interacts with the magnetic field produced by the current coil.

- Rotating Disc (for electromechanical meters): The current and voltage coils generate a magnetic field that induces a torque on a metal disc. The disc rotates, and the speed of rotation is proportional to the power consumption. The mechanical motion of the disc drives the dials to display the energy used.

- Digital Display (for electronic meters): Instead of mechanical dials, electronic energy meters have a digital display that shows the energy consumption in numerical form. A microcontroller processes the data to update the display in real-time.

- Mechanical Dials: In older electromechanical meters, the disc’s motion is linked to a set of dials or gears that indicate the energy usage.

- Brake Mechanism: A friction brake mechanism is applied to slow down the rotation of the disc in electromechanical meters, ensuring the meter measures the energy consumption accurately.

- Transformer (optional): In some energy meters, especially for higher voltage systems, transformers are used to step down the voltage to safe, measurable levels.

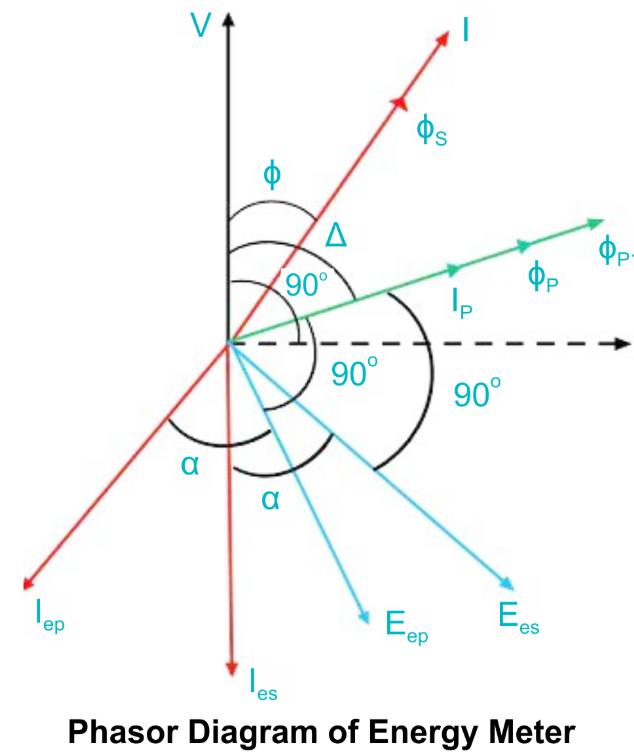

Energy Meter Phasor Diagram

The phasor diagram is a graphical representation of the relationship between the voltage and current waveforms in an AC circuit. For energy meters, phasor diagrams help in understanding how the current and voltage are related, which is essential for accurate energy measurement.

In a typical AC circuit, the voltage and current waveforms are sinusoidal but may be out of phase. The angle between the voltage and current phasors indicates the phase difference. For active power (real power), the voltage and current are in phase, and the power factor is unity (1). However, in most practical cases, the current and voltage are not perfectly in phase due to inductive or capacitive components, leading to a power factor less than 1.

The energy meter measures the product of voltage and current over time, which is then displayed as the energy consumption. The phase difference between the current and voltage is critical, as it influences the calculation of the true power (active power) that the energy meter records.

Conclusion

Energy meters are indispensable tools in modern electrical systems, providing accurate measurement and monitoring of electrical energy usage. Whether electromechanical, electronic, or smart meters, they all serve the primary function of measuring electrical consumption. Understanding the construction, working principles, and types of energy meters helps consumers and utilities optimize energy management and ensure efficient billing practices. Phasor diagrams are a useful tool in understanding the relationship between voltage and current, aiding in accurate energy measurement, particularly in AC circuits.

The post Energy Meter Definition, Types, Working, Construction & Diagram appeared first on ELE Times.

Analog IC vs Digital IC – Difference and Comparison

Integrated circuits (ICs) have revolutionized modern electronics, serving as the backbone of countless devices. Broadly, ICs are categorized into two main types: Analog ICs and Digital ICs. Understanding their differences and specific applications is essential for selecting the right components for various electronic systems. This article delves into the distinctions and comparisons between analog and digital ICs, highlighting their respective advantages, limitations, and use cases.

What are Analog ICs?

Analog ICs process continuous signals that vary over time and are used to manage real-world data such as sound, light, temperature, or pressure. These integrated circuits are crucial in scenarios that demand high precision and uncompromised signal quality.

Key Features of Analog ICs:

- Continuous Signal Processing: Operate with signals that have infinite values within a range.

- Signal Amplification and Conditioning: Amplify or modify analog signals for further processing.

- High Sensitivity: Analog ICs are ideal for handling small changes in signal amplitude.

Common Examples:

- Operational amplifiers (op-amps)

- Voltage regulators

- Analog-to-digital converters (ADCs)

- Audio amplifiers

What are Digital ICs?

Digital integrated circuits process discrete signals, encoding information in binary format, where data is represented as sequences of 0s and 1s. These ICs are integral to modern computing and communication systems.

Key Features of Digital ICs:

- Binary Signal Processing: Work with two distinct states, high (1) and low (0).

- Logical Operations: Perform arithmetic, logical, and control operations efficiently.

- Noise Immunity: Digital ICs demonstrate greater resilience to noise, making them more reliable in environments with high interference.

Common Examples:

- Microprocessors

- Memory chips (RAM, ROM)

- Logic gates

- Digital-to-analog converters (DACs)

Comparison Between Analog ICs and Digital ICs

| Aspect | Analog IC | Digital IC |

| Signal Type | Continuous signals | Discrete signals (binary) |

| Processing | Processes real-world, variable data | Processes binary data |

| Complexity | Simpler design | Higher complexity in circuits |

| Noise Sensitivity | More vulnerable to interference and distortions | More resistant to interference and noise disruptions |

| Applications | Audio, sensors, signal conditioning | Computing, storage, digital communication |

| Power Consumption | Generally higher for amplifiers | Lower for logic circuits |

| Accuracy | Depends on precision of components | High for binary operations |

| Speed | Limited by signal amplitude and frequency | Faster due to digital switching |

Hybrid ICs: Bridging the Gap

Modern systems often necessitate a combination of both analog and digital capabilities to function seamlessly. For instance, smartphones rely on analog ICs for signal acquisition (microphones, cameras) and digital ICs for processing (processors, memory). Hybrid ICs, which combine analog and digital components, are increasingly popular for such integrated applications.

Example:

- Analog-to-Digital Converters (ADCs) convert continuous analog inputs into a digital format, enabling their use in computational and processing systems.

- Digital-to-Analog Converters (DACs) take processed digital data and convert it back into analog signals for practical, real-world output.

Applications of Analog ICs

- Audio Equipment: Analog amplifiers and equalizers enhance sound quality in audio systems.

- Power Management: Voltage regulators and power amplifiers manage and stabilize power supplies.

- Sensors and Instrumentation: Analog ICs process data from temperature, pressure, and motion sensors.

Applications of Digital ICs

- Computing Devices: Microprocessors and memory chips drive computers and smartphones.

- Communication Systems: Digital signal processors (DSPs) enable data encoding, modulation, and transmission.

- Automation and Control: Logic circuits and microcontrollers power robotics and industrial automation.

Advantages and Disadvantages

Analog ICs:

- Advantages:

- Superior for real-world signal processing.

- Ideal for use in scenarios where maintaining high signal accuracy and integrity is essential.

- Disadvantages:

- More susceptible to interference and signal degradation.

- Larger power consumption for certain tasks.

Digital ICs:

- Advantages:

- High accuracy and noise immunity.

- Efficient for high-speed operations and complex computations.

- Disadvantages:

- Limited in handling real-world signals directly.

- Conversion to and from analog signals may introduce delays.

Conclusion

Analog and digital ICs serve distinct yet complementary roles in modern electronics. While analog ICs excel in processing real-world signals with precision, digital ICs dominate areas requiring speed, accuracy, and computational power. The synergy of these technologies, often realized in hybrid ICs, is driving innovation across industries such as healthcare, automotive, consumer electronics, and communication. Understanding the strengths and limitations of each type enables engineers and designers to create optimized and efficient electronic systems tailored to specific applications.

The post Analog IC vs Digital IC – Difference and Comparison appeared first on ELE Times.

Sparc the robot wiring

| A homemade robot powered by arduino [link] [comments] |

NUBURU announces board and committee appointments

Voyant launches FMCW LiDAR sensor on a chip

DOE announces $179m funding for Microelectronics Science Research Centers

Exploring Space with Next-Gen Satellites and Electronics

The relentless pursuit of space exploration has always been a testament to humanity’s desire to push the boundaries of what’s possible. From the earliest satellite launches to interplanetary missions, the technological advances driving these achievements are nothing short of revolutionary. Among these, next-generation satellites and cutting-edge electronics are at the forefront, enabling unprecedented capabilities in communication, observation, and exploration.

The Evolution of Satellite Technology

The journey of satellite technology began in 1957 with the launch of Sputnik 1, a rudimentary metal sphere weighing just 83.6 kilograms. Since then, satellites have evolved from basic communication devices to complex systems that underpin modern society. Today’s satellites are miniature marvels, integrating advanced materials, AI-driven systems, and versatile designs to meet a myriad of demands.

- Miniaturization and Cost Reduction: With advancements in microelectronics and manufacturing techniques, the size and cost of satellites have drastically decreased. CubeSats and nanosatellites, often no larger than a shoebox, are increasingly common, democratizing space access for academic institutions, startups, and developing nations.

- Increased Functionality: Modern satellites boast multi-functional capabilities, combining Earth observation, weather monitoring, and communication tasks in a single platform.

- Enhanced Durability: New materials and radiation-resistant electronics extend satellite lifespans, reducing the frequency and cost of replacements.

Cutting-Edge Electronics in Space Exploration

The electronics onboard spacecraft are critical to their success, operating in extreme conditions of temperature, radiation, and vacuum. Next-generation electronic systems are pushing the boundaries of what’s feasible in these harsh environments.

- Radiation-Hardened Components: Space electronics are designed to withstand intense radiation and high-energy particles. Innovations in semiconductor manufacturing, such as gallium nitride (GaN) and silicon carbide (SiC) technologies, enhance performance while ensuring reliability.

- AI and Edge Computing: Artificial Intelligence (AI) empowers satellites to operate independently by analyzing data and making decisions on the fly, significantly reducing dependency on ground control

- Energy Efficiency: Power consumption is a critical factor in space. Advances in low-power processors and energy-harvesting technologies, like solar arrays and thermal converters, ensure sustainable operations.

Transformative Applications of Next-Gen Satellites

The advancements in satellite technology and electronics have unlocked transformative applications across industries and domains. Here are some key domains impacted:

- Global Connectivity: Initiatives like SpaceX’s Starlink and OneWeb aim to provide high-speed internet access to even the most remote areas, bridging the digital divide and fostering economic growth.

- Earth Observation: Satellites equipped with high-resolution cameras and advanced sensors are pivotal for environmental monitoring, disaster response, and agricultural optimization.

- Space-Based Navigation: Next-gen satellites improve the accuracy and reliability of Global Navigation Satellite Systems (GNSS), enhancing applications from autonomous vehicles to precision farming.

- Deep Space Missions: Advanced electronics enable missions to Mars, asteroids, and beyond, with improved data transmission rates, robust hardware, and autonomous systems to handle the challenges of interplanetary travel.

Latest Case Studies

Recent case studies highlight the real-world impact of next-gen satellites and electronics. For instance, the European Space Agency’s (ESA) Copernicus Sentinel program uses cutting-edge satellites to monitor climate change, providing invaluable data for policymakers worldwide. Similarly, NASA’s Perseverance rover, equipped with advanced electronic systems, has been exploring Mars, collecting samples, and sending high-definition images back to Earth. Another example is SpaceX’s Starlink constellation, which has successfully deployed over 5,000 satellites, revolutionizing global broadband connectivity and demonstrating the scalability of modern satellite networks.

Challenges and Innovations

Despite these advancements, the journey toward next-gen satellites and electronics is not without challenges. Addressing these hurdles requires innovative solutions and collaborative efforts.

- Thermal Management: Extreme temperatures in space necessitate effective thermal management systems. Novel materials and phase-change technologies are being developed to dissipate heat efficiently.

- Space Debris Mitigation: The proliferation of satellites increases the risk of collisions and debris generation. Technologies like satellite-servicing robots, deorbiting mechanisms, and enhanced tracking systems are crucial for sustainable space operations.

- Data Security: As satellites become integral to global infrastructure, they face growing cybersecurity threats. Implementing quantum encryption and blockchain technology can enhance security.

- Supply Chain Constraints: The demand for specialized components, coupled with geopolitical factors, poses challenges to satellite production. Investments in domestic manufacturing and diversified sourcing are essential.

The Role of AI and Machine Learning

AI and Machine Learning (ML) are revolutionizing how satellites operate and interact with their environments. From autonomous navigation to predictive maintenance, these technologies are key enablers of next-gen satellite capabilities.

- Autonomous Navigation: AI algorithms allow satellites to adjust their orbits and avoid collisions autonomously, ensuring operational continuity.

- Predictive Maintenance: ML models analyze telemetry data to predict and prevent system failures, extending satellite lifespans.

- Dynamic Tasking: AI enables satellites to prioritize tasks based on real-time data, optimizing resource utilization.

Collaboration and the Future

The development of next-generation satellites and electronics is a global endeavor, with governments, private companies, and academic institutions contributing to the effort. Collaborative initiatives like NASA’s Artemis program, ESA’s Earth Observation missions, and ISRO’s Chandrayaan projects exemplify the collective drive to explore space.

The private sector also plays a pivotal role. Companies like SpaceX, Blue Origin, and Rocket Lab are not only advancing satellite technology but also redefining space transportation and logistics. Meanwhile, electronics giants are investing heavily in research and development to create components tailored for space applications.

Conclusion

Next-generation satellites and electronics are the backbone of modern space exploration and utilization. They enable groundbreaking applications, from global connectivity to interplanetary missions, while addressing challenges with innovative solutions. As humanity continues to explore the cosmos, the synergy between satellite technology and advanced electronics will undoubtedly shape the future of space exploration and its benefits for life on Earth.

The post Exploring Space with Next-Gen Satellites and Electronics appeared first on ELE Times.

Human Augmentation Tech: Bridging Electronics and Biology

In recent years, human augmentation technology has transitioned from science fiction to an exciting frontier of innovation. Bridging the gap between electronics and biology, this emerging field holds the promise to enhance human capabilities, address disabilities, and redefine our relationship with technology. By integrating advanced electronics into the human body, researchers and engineers are unlocking unprecedented possibilities in healthcare, communication, and even daily life.

Understanding Human AugmentationHuman augmentation refers to the application of technology to enhance or restore physical, cognitive, and sensory abilities. These enhancements can be divided into three broad categories:

- Physical Augmentation: Technologies that enhance physical strength, mobility, or endurance. Examples include exoskeletons and prosthetics.

- Cognitive Augmentation: Tools that boost mental capabilities such as memory, problem-solving, and learning.

- Sensory Augmentation: Devices that enhance or restore sensory perception, such as hearing aids, cochlear implants, or visual prostheses.

- Prosthetics and Bionics

Advanced prosthetics and bionic devices are redefining what it means to live with a disability. Prosthetic limbs equipped with sensors and actuators can replicate natural movements, while neural interfaces enable users to control these devices using brain signals. For instance, DARPA’s Brain-Machine Interface (BMI) program has developed prosthetics capable of providing tactile feedback, offering users a sense of touch.

- Exoskeletons

Exoskeletons are wearable devices that augment strength and mobility. Used in industries such as healthcare, military, and manufacturing, these devices reduce physical strain and assist individuals with mobility impairments. Companies like Ekso Bionics and ReWalk Robotics are leading the way in commercializing exoskeleton technologies.

- Brain-Computer Interfaces (BCIs)

BCIs establish direct communication between the brain and external devices. This technology is instrumental in restoring communication for individuals with severe paralysis. Neuralink, a company founded by Elon Musk, is pioneering BCIs that aim to treat neurological conditions and enable direct interaction with digital devices.

- Sensory Augmentation Devices

Sensory augmentation focuses on restoring or enhancing sensory inputs. Cochlear implants, for example, have revolutionized hearing restoration, while retinal implants like the Argus II are helping individuals with certain types of blindness regain partial vision. Innovations in haptic feedback systems are also enabling users to experience touch in virtual and augmented reality environments.

- Gene Editing and Bioengineering

Gene-editing technologies like CRISPR-Cas9 are paving the way for biological augmentation. By altering genetic codes, scientists aim to enhance immunity, improve cognitive functions, and even extend lifespan. Although still in its infancy, this area holds tremendous potential for preventive healthcare and personalized medicine.

Applications of Human AugmentationHealthcare

Human augmentation is already transforming the healthcare sector. From robotic surgical systems that enhance precision to wearable devices monitoring real-time health metrics, technology is enabling proactive and personalized medical care. For individuals with disabilities, augmentation devices are restoring independence and improving quality of life.

Military and Defense

Exoskeletons and augmented reality systems are being developed to enhance soldier capabilities on the battlefield. Augmented soldiers equipped with heads-up displays and enhanced communication systems can process critical information faster, improving decision-making in high-stress environments.

Workplace Productivity

In industrial settings, exoskeletons reduce fatigue and injury among workers by assisting with heavy lifting and repetitive tasks. Cognitive augmentation tools, such as AI-driven analytics platforms, are enhancing decision-making and problem-solving in office environments.

Education and Learning

Augmented reality (AR) and virtual reality (VR) technologies are creating immersive learning experiences. Cognitive augmentation tools are also helping students with learning disabilities by providing tailored educational content and improving focus.

Entertainment and Gaming

Wearable devices and haptic feedback systems are enhancing the gaming experience, allowing players to interact with virtual environments in unprecedented ways. Sensory augmentation devices are also enabling more inclusive gaming for individuals with disabilities.

Challenges in Human AugmentationWhile the potential of human augmentation is immense, the field faces several challenges:

Ethical Concerns

The integration of technology with human biology raises profound ethical questions. Should augmented individuals be given competitive advantages in education or the workplace? How do we ensure equitable access to these technologies?

Privacy and Security

Devices like BCIs and wearable health monitors collect sensitive data, making them potential targets for cyberattacks. Establishing robust security protocols and data privacy standards is essential to address these concerns.

Biocompatibility and Safety

Ensuring that augmentation devices are safe and compatible with the human body is critical. Long-term studies are necessary to assess the potential risks and side effects of implantable technologies.

Cost and Accessibility

Many human augmentation technologies are expensive, limiting their accessibility. Scaling production and developing cost-effective solutions will be vital to democratizing these innovations.

Future Directions in Human AugmentationAdvancements in AI and Machine Learning

AI is playing a pivotal role in enhancing human augmentation technologies. Machine learning algorithms are improving the functionality of prosthetics, enabling them to adapt to user behavior. AI-driven insights are also optimizing BCI systems and making real-time health monitoring more accurate.

Development of Soft Robotics

Soft robotics, which uses flexible materials, is revolutionizing wearable devices and prosthetics. These systems are more comfortable and better mimic natural movements, providing a seamless user experience.

Integration with 5G and IoT

The deployment of 5G networks and the Internet of Things (IoT) is facilitating seamless communication between augmentation devices and external systems. Real-time data exchange will enable faster decision-making and improved device functionality.

Focus on Sustainable Materials

To address environmental concerns, researchers are exploring sustainable and biodegradable materials for augmentation devices. These materials not only reduce ecological impact but also enhance biocompatibility.

Global Collaboration

Collaboration between governments, private sectors, and academic institutions is accelerating innovation in human augmentation. International partnerships are driving research, standardizing regulations, and ensuring ethical practices.

The Social Impact of Human AugmentationHuman augmentation has the potential to redefine societal norms. By addressing disabilities and enhancing abilities, these technologies can foster inclusivity and equity. However, they also risk widening social inequalities if access is limited to privileged groups. Balancing innovation with accessibility and ethical considerations will be crucial for harnessing the full potential of human augmentation.

ConclusionHuman augmentation technology represents a remarkable fusion of electronics and biology, pushing the boundaries of what humans can achieve. While challenges remain, ongoing advancements in AI, robotics, and biotechnology are paving the way for a future where augmented capabilities are an integral part of daily life. As we navigate this transformative era, fostering a collaborative, ethical, and inclusive approach will be key to ensuring these innovations benefit humanity as a whole.

The post Human Augmentation Tech: Bridging Electronics and Biology appeared first on ELE Times.

Dimmer Switch Meaning, Types, Working, Benefits & Applications

A dimmer switch is a versatile and practical device designed to adjust the brightness of lighting in a room. By regulating the amount of power delivered to a light bulb, dimmer switches offer users control over the ambiance and energy consumption of their spaces. These devices find extensive applications across homes, businesses, and industrial environments.

Types of Dimmer SwitchesDimmer switches are available in a variety of designs and technologies, each tailored to meet different requirements and compatible with various lighting setups:

1. Rotary Dimmer Switch:

– Operated by turning a knob to adjust brightness levels.

– Common in older installations and ideal for simple setups.

2. Slide Dimmer Switch:

– Features a sliding control to increase or decrease brightness.

– Allows for accurate control and is user-friendly.

3. Toggle Dimmer Switch:

– Combines a traditional on/off toggle with a small slider or dial for dimming.

– Merges functionality with a classic and enduring visual charm.

4. Touch Dimmer Switch:

– Adjusted by touching a panel or button.

– Often includes modern features like memory settings for preferred brightness levels.

5. Smart Dimmer Switch:

– Connects with smart home platforms and allows control through mobile apps or voice commands.

– Works seamlessly with smart devices such as Amazon Alexa, Google Assistant, and Apple HomeKit.

6. Universal Dimmer Switch:

– Compatible with different types of bulbs, such as incandescent, LED, and CFL.

– Ideal for versatile lighting setups.

How Does a Dimmer Switch Work?

Dimmer switches function by regulating the electrical current supplied to a light bulb, altering its intensity. The way a dimmer switch operates differs depending on its type and technology:

1. Incandescent Dimmers:

– Decrease the electrical voltage delivered to the bulb..

– Simple yet effective for traditional incandescent lights.

2. TRIAC Dimmers:

– Use a TRIAC (Triode for Alternating Current) semiconductor to control power delivery.

– Common in modern dimmers for compatibility with LEDs and CFLs.

3. Pulse Width Modulation (PWM):

– Found in advanced dimmers, especially for LED lights.

– Modulates the electrical signal by rapidly turning it on and off to adjust brightness without flickering.

4. Resistive Dimmers:

– Employ resistors to limit the electrical flow.

– Typically used in low-power or specialty applications.

Dimmer switches are widely used to enhance lighting environments and offer specific benefits across various settings:

1. Residential Spaces:

– Set a warm and inviting mood in spaces like living rooms, dining areas, and bedrooms.

– Enable mood lighting for special occasions or relaxation.

2. Commercial Settings:

– Adjust lighting in restaurants, hotels, and retail stores to suit customer preferences.

– Improve energy efficiency in offices by adapting light levels based on natural light.

3. Theatrical and Event Lighting:

– Offer accurate management of lighting for stage productions and event configurations.

4. Outdoor Applications:

– Control exterior lights, such as patio or garden lighting, to complement outdoor activities.

Using a dimmer switch is straightforward, but it’s essential to follow certain steps for optimal performance:

1. Choose the Right Dimmer:

– Ensure compatibility with your lighting system (e.g., LED-compatible dimmer for LED bulbs).

2. Installation:

– Ensure the power supply is completely switched off before beginning the installation process.

– Adhere to the provided installation guidelines or seek assistance from a qualified electrician.

3. Operation:

– Adjust brightness levels using the slider, knob, or touch interface.

– For smart dimmers, set up the device via the accompanying app for remote control.

4. Maintenance:

– Regularly clean the switch to maintain optimal functionality.

– Replace faulty dimmers to maintain lighting quality.

Dimmer switches offer several benefits, making them a popular choice for lighting control:

1. Energy Efficiency:

– Lower brightness levels reduce power consumption, leading to energy savings.

2. Extended Bulb Life:

– Reduced electrical flow minimizes stress on bulbs, increasing their lifespan.

3. Customizable Ambiance:

– Adjust lighting to suit activities like reading, relaxing, or entertaining.

4. Cost Savings:

– Energy savings and extended bulb life contribute to reduced utility and replacement costs.

5. Environmental Benefits:

– Reduced energy usage results in a smaller environmental impact and a lower carbon footprint.

6. Enhanced Aesthetics:

– Create visually appealing spaces with tailored lighting effects.

While dimmer switches offer numerous benefits, they may present some challenges:

1. Compatibility Issues:

– Ensure compatibility between your bulbs and the dimmer to prevent flickering or suboptimal performance.

2. Installation Errors:

– Ensure proper wiring and follow guidelines to prevent malfunctions.

3. Noise:

– Some dimmers may produce a humming sound; selecting high-quality products can mitigate this issue.

4. Limited Dimming Range:

– Check the dimmer’s specifications for the range of brightness levels it supports.

Dimmer switches are essential for improving lighting management, boosting energy efficiency, and creating the desired atmosphere. With various types available, from simple rotary models to advanced smart dimmers, they cater to diverse needs and preferences. By understanding their functionality, applications, and benefits, you can effectively integrate dimmer switches into your spaces, transforming the way you experience lighting.

The post Dimmer Switch Meaning, Types, Working, Benefits & Applications appeared first on ELE Times.

Stealth Technology Definition, Types, Working & Applications

Stealth technology, also known as low observable technology, is a sophisticated engineering method aimed at making objects less visible to radar, infrared, sonar, and other detection methods. Originally developed for military applications, stealth technology has significantly evolved, playing a critical role in modern warfare, security, and even civilian applications.

Types of Stealth TechnologyStealth technology encompasses various techniques and methods designed to evade detection across different spectrums. The primary types include:

Radar Stealth:

– Uses specially designed shapes and materials to reduce radar cross-section (RCS).

– Aircraft like the F-22 Raptor and B-2 Spirit are prime examples, designed with angular shapes to deflect radar signals.

Infrared Stealth:

– Focuses on reducing heat signatures emitted by engines and exhausts.

– Utilizes heat shields, special coatings, and exhaust cooling techniques.

Acoustic Stealth:

– Reduces noise generated by vehicles, particularly submarines and helicopters.

– Employs quiet engines, sound-dampening materials, and advanced propeller designs.

Visual Stealth:

– Involves camouflage and coatings to blend with surroundings.

– Advanced techniques include adaptive camouflage using digital displays or light-reflecting materials.

Electromagnetic Stealth:

– Reduces electromagnetic emissions from electronic systems to prevent detection or interception.

Sonar Stealth:

– Targets underwater applications by minimizing sound wave reflections.

– Submarines use anechoic coatings to absorb sound waves and avoid sonar detection.

Stealth technology operates on the principles of reflection, absorption, and emission minimization:

1. Shaping:

– Aircraft and vehicles are designed with sharp angles and curves that deflect radar waves away from the source.

2. Radar-Absorbent Materials (RAM):

– Specialized coatings and composites absorb radar waves, reducing reflected signals.

3. Heat Suppression:

– Thermal management systems dissipate or redirect heat emissions to minimize infrared detectability.

4. Soundproofing:

– Advanced insulation and quiet propulsion systems reduce acoustic signatures.

5. Signal Emission Control:

– Shielding electronic components limits electromagnetic leaks, ensuring stealthy operations.

Stealth technology has a wide range of applications, primarily in defense but increasingly in civilian sectors:

1. Military Aviation:

– Stealth fighters and bombers like the F-35 Lightning II and B-2 Spirit dominate airspace with their low radar detectability.

2. Naval Applications:

– Stealth ships and submarines employ sonar-absorbing materials and noise-reduction designs.

3. Missiles and Drones:

– Unmanned aerial vehicles (UAVs) and advanced missiles use stealth to penetrate enemy defenses.

4. Land Vehicles:

– Tanks and armored vehicles incorporate stealth coatings and designs for battlefield advantage.

5. Surveillance:

– Stealth drones and sensors are used in intelligence gathering, reconnaissance, and tracking operations.

6. Civilian Uses:

– Concepts like noise-reduction in transportation, such as electric vehicles, benefit from stealth principles.

The advantages of stealth technology extend well beyond reducing visibility:

1. Operational Superiority:

– Allows forces to operate undetected, giving them a significant tactical advantage.

2. Survivability:

– Reduces the likelihood of detection and targeting by adversaries.

3. Precision Strikes:

– Enhances mission effectiveness by allowing stealthy penetration into hostile environments.

4. Versatility:

– Adaptable for various platforms, including aircraft, ships, submarines, and vehicles.

5. Enhanced Safety:

– Reduces collateral damage by enabling targeted operations.

Several iconic examples demonstrate the efficacy and evolution of stealth technology:

1. F-117 Nighthawk:

– The world’s first operational stealth aircraft, designed primarily for radar evasion.

2. B-2 Spirit Bomber:

– A long-range bomber with an all-wing design to minimize radar visibility.

3. F-22 Raptor:

– A fifth-generation fighter aircraft known for its radar-absorbing coatings and advanced stealth features.

4. Virginia-Class Submarine:

– Utilizes acoustic stealth to operate undetected in hostile waters.

5. Zumwalt-Class Destroyer:

– A stealth warship with angular designs and radar-absorbent materials.

6. RQ-170 Sentinel Drone:

– Known as the “Beast of Kandahar,” this UAV combines stealth and advanced surveillance capabilities.

While stealth technology provides numerous benefits, it also encounters significant challenges:

1. High Costs:

– Stealth platforms are expensive to design, build, and maintain.

2. Technological Countermeasures:

– Advanced detection methods, like low-frequency radar, challenge stealth capabilities.

3. Limited Payloads:

– To maintain stealth, platforms often compromise on weapon load and internal space.

4. Environmental Conditions:

– Factors like weather can impact the effectiveness of stealth features.

5. Energy Demand:

– Sophisticated stealth systems often require high energy, limiting their operational endurance.

The future of stealth technology lies in adaptive and intelligent systems. Emerging trends include:

– Quantum Stealth: Advanced materials that bend light to make objects invisible.

– AI Integration: Autonomous systems capable of dynamic stealth adjustments.

– Hypersonic Applications: Developing stealth features for high-speed vehicles.

– Advanced Materials: Nano-coatings and metamaterials for enhanced stealth.

Stealth technology represents a pivotal advancement in modern engineering and defense. From radar evasion to acoustic stealth, its applications have reshaped military strategy and continue to influence various fields. As detection methods evolve, so too will stealth technologies, ensuring their relevance in a rapidly advancing technological landscape.

The post Stealth Technology Definition, Types, Working & Applications appeared first on ELE Times.

Is Imagination Technologies for sale again?

Graphics chip designer Imagination Technologies is up for grabs again. A Bloomberg report claims that Canyon Bridge Capital Partners, the private equity firm with ties to Chinese state investors, has hired Lazard Inc. to seek a buyer for the Hertfordshire, U.K.-based chip designer.

Imagination, once a promising graphics technology outfit, could never recover after the Apple fiasco and the perception of Chinese ownership. According to media reports, Apple, which owned an 8.1% stake in Imagination, considered buying the British chip designer in 2016. However, after failing to agree on Imagination’s valuation, Apple left the negotiating table and announced that it would start developing its own graphics IP.

Apple contributed to nearly half of Imagination’s sale, sending shock waves at the British chip company at that time. The company’s stock fell by 70%, and in 2017, Canyon Bridge, backed by state-owned China Reform, acquired Imagination for $686 million. Soon after, Imagination began shedding its non-core businesses; for instance, it sold its connectivity business Ensigma comprising Wi-Fi and Bluetooth silicon to Nordic Semiconductor.

Next came the issue of China gaining access to key semiconductor technology. The effort to appoint new board members and Imagination’s listing in Shanghai proved hot potatoes, leading to intervention from the U.K. regulators to ensure that Imagination remains a U.K.-headquartered business. The company has been in distress since then.

Figure 1 Imagination has more than 3,500 patents related to graphics and related technologies.

Its CEO, Simon Beresford-Wylie, has denied a recent Daily Telegraph report that he’s stepping down. He also rejected some reports about the company engaging in illicit transfers of technology to China. Earlier, in November 2023, Reuters reported that Imagination was laying off 20% of its staff.

With this backdrop, let’s go back to Imagination on the selling block. The Bloomberg report has named Alphabet Inc.’s Google, MediaTek, Renesas, and Texas Instruments as Imagination’s key clients. But no suitors have been reported in trade media yet.

Imagination owners are pinning their hopes on two major factors. First, they draw their hopes from Nvidia’s runaway success in the graphics realm. Though Nvidia’s GPUs are targeted at entirely different markets such as data centers and scientific computing. Imagination, on the other hand, mainly offers graphic solutions for lower-power markets such as automotive, PC cards, drones, robotics, and smartphones.

Second, like Nvidia, Imagination aims to bolster its standing by incorporating artificial intelligence (AI) content in its graphics IP offerings. The British chip firm plans to turn its graphics IP into AI accelerators for low-power training and inference applications.

Figure 2 Imagination is aiming to bring graphics-centric AI to battery-powered devices like drones and smartphones.

Imagination, founded in 1985, has come a long way in its 40-year long technology journey. Once seen as a jewel in Britain’s technology crown, it’s now facing the paradox of a struggling company with a highly promising technology. Perhaps its new owner could address that paradox and put the graphics design house in order.

Related Content

- Re-imagining Imagination Technologies

- Imagination’s RISC-V gambit reaches its next level

- Imagination Raises $100 Million Investment To Take On Edge AI

- GPU specialist Imagination to create 250 engineering jobs in 2022

- Imagination Sells Ensigma Wi-Fi Business to Nordic Semiconductor

The post Is Imagination Technologies for sale again? appeared first on EDN.

I modified an electronic sump pump controller to add a battery backup.

| submitted by /u/ElectricGears [link] [comments] |

EEVblog 1660 - AC Basics Tutorial Part 4: Resistors, Capacitors, Inductors

Every Component of a Linear Power Supply Explained (while building one)

| submitted by /u/ZenoArrow [link] [comments] |

Myths and facts on the origins of the name "BNC". (TL;DR: Neill and Concelman did not invent it).

| submitted by /u/1Davide [link] [comments] |

[Brag] First time built AM modulator with Colpitts oscillator

![[Brag] First time built AM modulator with Colpitts oscillator [Brag] First time built AM modulator with Colpitts oscillator](https://b.thumbs.redditmedia.com/zrvnvzadC8qwPZfRS1g3PYFXfghQ8TWBj-7phPRrESA.jpg) | submitted by /u/Prestigious-Sky-4104 [link] [comments] |