ELE Times

Anritsu and SK Telecom Jointly Verify AI-Based Antenna Optimisation, POSTECH and Bluetest

ANRITSU CORPORATION has jointly verified AI-based antenna optimisation technologies with SK Telecom, South Korea’s leading mobile network operator, Pohang University of Science and Technology (POSTECH), and Bluetest of Sweden.

In this verification, MIMO measurement data were acquired in a real user environment using Anritsu’s Radio Communication Test Station MT8000A and Universal Wireless Test Set MT8870A. Based on AI-based analysis and optimisation technologies, the effectiveness of antenna performance optimisation was confirmed.

Details of this joint verification were also presented at MWC Barcelona 2026 (MWC 2026), one of the world’s largest mobile communications exhibitions.

This verification analysed antenna performance based on throughput and ECC (Error Correlation Coefficient) data collected from real user environments. It reflected practical usage conditions, including free-space scenarios, handheld operation, and head-proximate usage scenarios. By incorporating a variety of user grip conditions, it quantitatively evaluated performance variations under time-varying RF conditions.

Through AI-based analysis, RF performance differences according to antenna tuner states were modelled, and the optimal antenna switching configuration was automatically identified. This enabled dynamic optimisation of antenna performance while maintaining communication quality in real user environments.

Based on measurement-driven evaluation results, significant throughput improvements were confirmed across various user scenarios in an 8Rx (eight-receive-antenna) configuration, while in a 4Tx (four-transmit-antenna) configuration, throughput improvement of up to more than two times was observed.

Verification Overview

This verification presented an AI-based antenna optimisation workflow built on real measurement data collected in an Over-the-Air (OTA) test environment.

The verification covered the following processes:

- Analysis of RF performance variations according to user scenarios and tuner state changes

- Comparison of power and performance characteristics for each antenna path

- Derivation of optimal switching states based on throughput and ECC data

- Verification of performance improvement through AI analysis based on measurement data

This approach goes beyond conventional static antenna design-centric evaluation, enabling data-driven optimisation verification that reflects real environmental conditions.

MT8000A (5G NR Test Platform)

MT8000A is an integrated RF and protocol-based test platform for 5G NR device validation. In this verification, it was used for MIMO performance analysis and throughput evaluation in an OTA environment.

Key features include:

- 4×4 / 8×8 MIMO signal generation and OTA data acquisition

- Multi-port synchronised measurement based on digital IQ capture

- Throughput evaluation under controlled 5G NR link conditions

- Provision of a repeatable and stable RF test environment

MT8000A provided high-precision signal generation and analysis capabilities for measurement-based performance verification, supporting the acquisition of highly reliable data required for AI modelling.

MT8870A (RF Measurement Platform)

MT8870A is a general-purpose wireless measurement platform supporting non-signalling RF measurements. In this verification, it was used for RF characteristic analysis by antenna path and comparative measurement of switching states.

Key features include:

- RF power measurement by antenna path under various tuner states

- TX/RX path control and RF characteristic measurement

- Collection of measurement data across antenna paths and switching states

- Support for multi-port RF measurement configurations

The path-specific RF characteristic data obtained through MT8870A is used as core input data for AI-based optimisation analysis.

The post Anritsu and SK Telecom Jointly Verify AI-Based Antenna Optimisation, POSTECH and Bluetest appeared first on ELE Times.

Gartner Predicts That by 2030, Performing Inference on an LLM With 1 Trillion Parameters Will Cost GenAI Providers Over 90% Less Than in 2025

By 2030, performing inference on a large language model (LLM) with one trillion parameters will cost GenAI providers over 90% less than it did in 2025, according to Gartner, Inc., a business and technology insights company.

AI tokens are the units of data that GenAI models process. For the purposes of this analysis, a token is 3.5 bytes of data, or approximately 4 characters.

“These cost improvements will be driven by a combination of semiconductor and infrastructure efficiency improvements, model design innovations, higher chip utilisation, increased use of inference-specialised silicon, and application of edge devices for specific use cases,” said Will Sommer, Sr. Director Analyst at Gartner.

As a result of these trends, Gartner forecasts that LLMs in 2030 will be up to 100 times more cost-efficient than the earliest models of similar size developed in 2022.

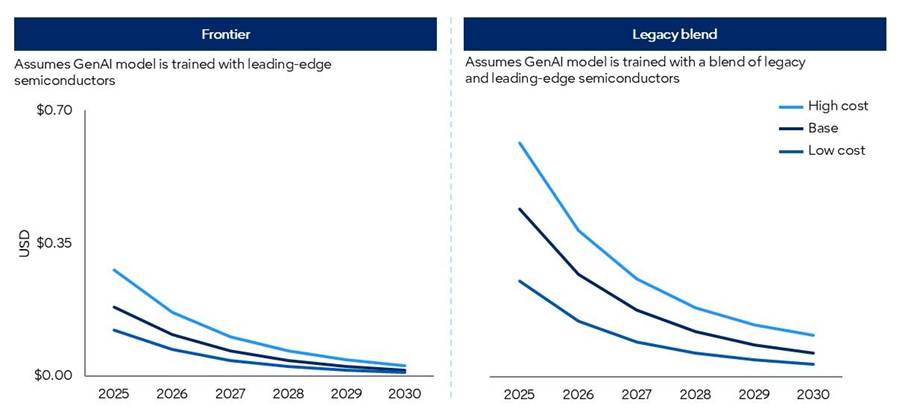

The forecasted model results are split between two sets of semiconductor scenarios:

- Frontier scenarios: Model processing is based on a representation of cutting-edge chips.

- Legacy blend scenarios: Model processing is based on a representative blend of available semiconductors benchmarked to Gartner forecasts.

Modelled costs in the “blend” forecast scenarios are considerably higher than in the “frontier” scenarios, given lower computational power (see Figure 1).

Figure 1: Gartner GenAI Inference Cost Scenario Forecasts

Source: Gartner (March 2026)

Falling Token Costs will not Democratize Frontier Intelligence

However, falling GenAI provider token costs will not be fully passed on to enterprise customers. Moreover, frontier intelligence will demand significantly more tokens than current mainstream applications. Agentic models, for example, require between 5-30 times more tokens per task than a standard GenAI chatbot, and can perform many more tasks than a human using GenAI.

While lower token unit costs will enable more advanced GenAI capabilities, these advancements will drive disproportionately higher token demand. As token consumption rises faster than token costs fall, overall inference costs are expected to increase.

“Chief Product Officers (CPOs) should not confuse the deflation of commodity tokens with the democratisation of frontier reasoning,” said Sommer. “As commoditised intelligence trends toward near-zero cost, the compute and systems needed to support advanced reasoning remain scarce. CPOs who mask architectural inefficiencies with cheap tokens today will find agentic scale elusive tomorrow.”

Value will accrue to platforms that can orchestrate workloads across a diverse portfolio of models. Routine, high-frequency tasks must be routed to more efficient small and domain-specific language models, which perform better than generic solutions at a fraction of the cost when aligned to specialised workflows. Expensive inference of frontier-level models must be heavily gated and reserved exclusively for high-margin, complex reasoning tasks.

The post Gartner Predicts That by 2030, Performing Inference on an LLM With 1 Trillion Parameters Will Cost GenAI Providers Over 90% Less Than in 2025 appeared first on ELE Times.

Keysight Launches Local Manufacturing in India to Accelerate Global Innovation

Keysight Technologies has announced plans to begin local manufacturing in India, expanding its global production footprint to provide locally manufactured solutions for the country’s mission-critical industries. This strategic expansion enables Keysight to better serve its long-standing customer base—including aerospace and defence, government R&D, industry and academic research institutions—by providing streamlined procurement of world-class technology.

As India emerges as one of the world’s fastest-growing innovation economies, demand for advanced test and measurement technologies is increasing across all industrial and research sectors. India’s electronics manufacturing sector is expected to exceed $300 billion by 2026, driven by a surge in domestic production and advanced research initiatives.

The phased rollout of the new facility will focus on test equipment, serving both Indian and global customers while enhancing supply chain resilience. The move reinforces Keysight’s long-term commitment to India and aligns with the country’s flagship initiatives, including Make in India, Semicon India, the National Quantum Mission, as well as aerospace and defence modernisation programs.

“India is entering a once-in-a-generation innovation decade,” said Sudhir Tangri, Vice President and General Manager, Asia Pacific at Keysight. “Establishing local manufacturing allows Keysight to better support customers in India while strengthening our global supply chain. Building in India for the world will accelerate technology development across a broad spectrum of industries.”

Keysight’s manufacturing operations in India will support innovation across key sectors:

- Semiconductors: Enabling design validation and production testing as India expands its semiconductor industry under the Semicon India program.

- Quantum Technologies: Supporting research institutions and national laboratories advancing quantum computing under the National Quantum Mission.

- Aerospace and Defence: Providing advanced, locally manufactured test solutions for radar, electronic warfare, and satellite systems supporting India’s defence modernisation.

- Next-Generation AI and Wireless: Accelerating development and deployment of 5G and future 6G infrastructure, AI infrastructure and data centres.

- Research and Academia: Equipping universities and national laboratories with world-class tools for advanced engineering research and scientific discovery.

Keysight will continue to collaborate with Indian government agencies, research laboratories, and leading engineering universities to accelerate technology development and strengthen the country’s innovation ecosystem. The expansion reflects Keysight’s long-term strategy to invest in high-growth technology hubs that support customers developing the next generation of computing, communications, and national security systems.

The post Keysight Launches Local Manufacturing in India to Accelerate Global Innovation appeared first on ELE Times.

Microchip Introduces Automotive-Qualified System-in-Package Hybrid MCU for Automotive and E-Mobility Human-Machine Interface Applications

processor and 512 Mbit DDR2 SDRAM. The SAM9X75D5M supports large display sizes up to 10 inches and XGA resolution of 1024 × 768 pixels.

processor and 512 Mbit DDR2 SDRAM. The SAM9X75D5M supports large display sizes up to 10 inches and XGA resolution of 1024 × 768 pixels.The post Microchip Introduces Automotive-Qualified System-in-Package Hybrid MCU for Automotive and E-Mobility Human-Machine Interface Applications appeared first on ELE Times.

Cadence and NVIDIA Collaborate on Accelerated Engineering Solutions for Agentic AI Chip and System Design

Cadence announced an expansion of its broad collaboration with NVIDIA to accelerate Cadence’s Design for AI and AI for Design strategy. The next generation of agentic AI design solutions includes autonomous, long-running agents that require accelerated, trusted, physics-grounded engines to translate design intent into automated flows, generate designs and debug errors, and manage long, complex, end-to-end workflows. Cadence’s leadership in agentic AI is expanded by integrating its portfolio of industry-leading chip and system design solutions with NVIDIA’s accelerated computing stack.

“The fusion of agentic AI and physics-based design is transforming how the world’s most advanced chips are engineered,” said Anirudh Devgan, president and CEO of Cadence. “Through our expanded collaboration with NVIDIA, we’re bringing together Cadence’s expertise in agentic IC design and physics-driven optimisation with NVIDIA’s accelerated computing to advance a new era of AI-driven chip innovation. Together, we’re enabling customers to design more intelligent, efficient silicon that will power the next generation of computing and AI infrastructure.”

“AI is driving the largest infrastructure buildout in history—spurring the creation of new chips, systems, and AI factories around the world,” said Jensen Huang, founder and CEO of NVIDIA. “Together, NVIDIA and Cadence have created the Cadence Millennium M2000—a revolutionary AI supercomputer built to tackle the immense scale and complexity of designing the world’s next generation of infrastructure.”

Broadest-Ever Portfolio of Accelerated Design Solutions

To give agents and engineers the tools they need, Cadence has expanded its design solutions accelerated with NVIDIA Grace CPUs and NVIDIA Blackwell GPUs—and as a turnkey deployment on the Cadence Millennium M2000 Supercomputer—delivering up to 80X greater throughput and up to 20X lower power consumption. This expanded offering now spans analysis, optimisation, and design, with key solvers deeply optimised with NVIDIA CUDA-X. One example is the Cadence Clarity 3D Solver demonstrating that a Millennium M2000 system configured with 8X NVIDIA RTX Pro 6000 GPU servers is up to 5X faster, or 4X better cost iso-performance, compared to an equivalent CPU-based solution, when extracting complex and large-scale designs.

Cadence accelerated solutions that will be available in 2026 include:

- Electronic Design Automation (EDA): The industry’s leading place-and-route solution, Innovus Implementation System; chip, chiplet and 3D-IC analysis and optimisation with Celsius Thermal Solver and Voltus IC Power Integrity Solution; advanced memory and circuit analysis with EMX Planar 3D Solver and Liberate MX Memory Characterisation; and Spectre X Simulator and Quantus Field Solver for circuit analysis.

- System Design Automation (SDA): Industry-leading advanced package and PCB optimisation with the Allegro X Design Platform, Clarity 3D Solver, Celsius EC Solver; system-level multiphysics analysis with Fidelity CFD Software; and Cadence MSC Actran for physical AI system analysis and optimisation.

- Life Sciences / Bio: ROCS X is an AI-enabled virtual screening solution that enables scientists to conduct 3D searches of over 200 trillion drug-like molecules. Target X is a physics-based AI solution that detects potential druggable pockets, achieving a success rate of over 90%.

The Cadence Allegro X Design Platform and the Cadence Reality Digital Twin Platform also integrate with NVIDIA Omniverse libraries for photo-realistic visualisation, critical for multi-disciplinary engineering and design. Cadence’s MSC Virtual Test Drive (VTD) is being integrated with NVIDIA Cosmos and NVIDIA Omniverse NuRec for advancing the state of the art in physical AI.

Design for AI and AI for Design

Industry leaders use Cadence’s full suite of accelerated agentic solutions to design the next generation of AI infrastructure. The Cadence Reality Digital Twin Platform helps teams use physics-based models and AI to design and operate AI factories, accelerating deployment timelines and unlocking new revenue streams across the data centre portfolio.

Cadence is advancing AI-driven engineering with its agentic AI solutions, led by the Cadence ChipStack AI Super Agent, to help engineers deliver higher quality, more complex designs. Cadence and NVIDIA are also collaborating on future agentic AI innovations in custom and analogue design and building deep research and long-running agents for engineering NVIDIA NemoClaw, an open source stack that simplifies running OpenClaw always-on assistants, more safely, with a single command. As part of the NVIDIA Agent Toolkit, it installs the NVIDIA OpenShell runtime—a secure environment for running autonomous agents, and open source models like NVIDIA Nemotron.

From Silicon to Turbofan Engines, Customers Achieve the Previously Impossible

Cadence customers across semiconductors, automotive, aerospace and life sciences are using agentic AI, GPU-accelerated solutions and the Millennium M2000 Supercomputer to tackle design challenges that are not achievable with traditional approaches.

Honda is using Cadence Fidelity CFD Software, accelerated on the Millennium M2000 GB200 NVL72 system, to pursue time-accurate, full turbofan engine simulation—a grand challenge in computational fluid dynamics (CFD) previously impractical for routine design use.

“This capability opens the door to a more exploratory design methodology—one where our engineers can evaluate tradeoffs earlier and innovate with greater confidence as we develop the next generation of high-performance gas turbine engines,” said Keiji Otsu, CEO, Honda R&D.

Micron is integrating GPU-accelerated Cadence design technologies and Cadence’s agentic AI solution directly into its HBM memory design flow to accelerate iteration and maintain accuracy at leading-edge scale.

“As our HBM and next-generation memory designs grow in scale and complexity, reducing the cycle time for our most demanding verification and simulation steps has become essential,” said Sanjay Mehrotra, Chairman, president and CEO, Micron. “Through our expanded collaboration with Cadence, we’re integrating GPU-accelerated design technologies—powered by NVIDIA computing—and building agentic AI directly into our development environment.”

Larsen & Toubro Semiconductor is using the Cadence Spectre X Simulator, accelerated up to 5X with NVIDIA GPUs, to shorten design cycles for next-generation AI and data centre chips as the company advances India’s sovereign semiconductor ambitions.

“Faster design iteration and verification directly translate into competitive advantage and time to market for the highly customised AI silicon we’re building,” said Sandeep Kumar, CEO, Larsen & Toubro Semiconductor. “GPU-accelerated performance from Cadence’s Spectre X Simulator gives our teams the throughput to confidently move complex, AI-ready chips into production faster.“

The post Cadence and NVIDIA Collaborate on Accelerated Engineering Solutions for Agentic AI Chip and System Design appeared first on ELE Times.

TI unveils high-performance isolated power modules to advance power density in data centers and EVs

Texas Instruments (TI) has unveiled new isolated power modules, helping enable increased power density, efficiency and safety in applications ranging from data centres to electric vehicles (EVs). The UCC34141-Q1 and UCC33420 isolated power modules leverage TI’s IsoShield technology, a proprietary multichip packaging solution that achieves up to three times higher power density than discrete solutions in isolated power designs. TI is showcasing these innovations at the 2026 Applied Power Electronics Conference (APEC), March 23-26 in San Antonio, Texas.

“Packaging innovation is revolutionising the power industry, with power modules at the forefront of this transformation,” said Kannan Soundarapandian, vice president and general manager, High Voltage Products at TI. “TI’s new IsoShield technology delivers what power engineers need most: smaller solutions with improved efficiency and reliability, and a faster time to market. It is the latest example of TI’s continued commitment to advance power semiconductor technology to help solve today’s engineering challenges.”

Redefining power density with TI’s packaging technology

Historically, power designers have turned to power modules to conserve valuable board space and simplify the design process. As chip sizes reach their physical limits and miniaturisation increases in importance, advancements in packaging technology are enabling further performance and efficiency gains.

TI’s new IsoShield technology combines a high-performance planar transformer with an isolated power stage, offering functional, basic, and reinforced isolation capabilities. It enables a distributed power architecture, helping manufacturers meet functional safety requirements by avoiding single-point failures. The result is a packaging advancement that shrinks solution size by as much as 70% while delivering up to 2W of power, enabling compact, high-performance and reliable designs for automotive, industrial and data centre applications that require reinforced isolation.

Advancing data centre and EV performance through power innovations

Power density innovations are nowhere more critical than in today’s evolving data centre and automotive designs. Meeting design requirements in those applications starts with advanced analogue semiconductors – the components that enable smarter, more efficient operations. As global data centres continue to scale to meet exponentially growing demand, high-performance power modules must pack more power in smaller spaces. With TI’s IsoShield packaging technology, designers can achieve higher power density in compact form factors, ensuring reliable and safe operation of the world’s digital infrastructure. Similarly, the increased power density enabled by IsoShield technology helps engineers design lighter and more efficient EVs that significantly extend range and enhance performance.

Building on our power module innovation

For decades, TI has strategically invested in power management technology, with recent developments in power modules that feature integrated transformers and integrated inductors. Through innovative proprietary packaging solutions such as IsoShield and MagPack technologies, along with a comprehensive portfolio of over 350 power modules with optimised packages, TI’s semiconductors empower engineers to maximise performance in any power design or application.

technologies, along with a comprehensive portfolio of over 350 power modules with optimised packages, TI’s semiconductors empower engineers to maximise performance in any power design or application.

Innovating what’s next in power at APEC 2026

In booth No. 1819 at the Henry B. González Convention Centre, TI will feature the isolated power modules with IsoShield technology in a high-power, high-performance automotive silicon carbide (SiC) 300kW traction inverter reference design. Additionally, TI will debut other advancements in data centers, automotive, humanoid robots, sustainable energy and USB Type-C® applications, including an 800V to 6V DC/DC power distribution board. This design features TI’s portfolio of gallium nitride integrated power stages, digital isolators and microcontrollers that help enable high efficiency and power density in power conversion for next-generation data center computing trays with AI processors.

The post TI unveils high-performance isolated power modules to advance power density in data centers and EVs appeared first on ELE Times.

STMicroelectronics Unveils AI-Enabled ‘Stellar P3E’ MCU, Backs 28nm Strategy for Cost and Supply Chain Stability

By Shreya Bansal, Sub-Editor

STMicroelectronics introduced the Stellar P3E, a next-generation automotive microcontroller with embedded artificial intelligence (AI) acceleration, positioning it as a key enabler for software-defined vehicles (SDVs) and consolidated “X-in-1” electric vehicle architectures.

Announced during a media briefing, the Stellar P3E marks a significant step in integrating real-time AI with deterministic control, addressing the rising complexity of modern automotive systems driven by electrification and connectivity.

Powering the X-in-1 Transition

Automakers are increasingly shifting toward “X-in-1” architectures, which consolidate multiple functions, such as battery management, onboard charging, and power conversion into a single system. This reduces hardware redundancy, wiring, and overall system weight.

The Stellar P3E is designed to sit at the centre of this transition, combining high-performance computing, advanced analogue integration, and AI capabilities in a single chip.

Embedded AI for Real-Time Intelligence

A key highlight of the new MCU is its Neural ART Accelerator, a dedicated neural processing unit (NPU) that enables real-time AI inference at the edge. The accelerator is capable of significantly reducing inference time, up to 69 times faster than CPU-based implementations, while maintaining low power consumption.

This allows vehicles to process unstructured data, detect patterns, and adapt system behaviour dynamically, supporting applications such as predictive maintenance, intelligent sensing, and optimised energy management.

Addressing Industry-Wide Complexity

With vehicles evolving into software-driven platforms, the industry is facing unprecedented challenges, including exponential software growth, stricter safety and cybersecurity requirements, and ongoing supply chain uncertainties.

STMicroelectronics emphasised three key pillars behind the Stellar P3E:

- Reducing complexity and cost through hardware consolidation and software optimisation

- Enabling smarter systems with AI-driven algorithms

- Delivering high-performance computing with precise sensing and actuation

The MCU also complies with ISO 21434 cybersecurity standards and incorporates flexible safety configurations, including split-lock and lockstep modes.

High Performance, Rich Integration

The Stellar P3E delivers up to 8,000 CoreMark performance and features:

- Up to 19.5 MB of embedded non-volatile memory using phase-change memory (PCM)

- Over 300 GPIOs and more than 100 ADC channels

- Support for Gigabit Ethernet and CAN-XL communication

These capabilities enable integration of multiple powertrain components, including inverters, DC-DC converters, and battery systems within a unified architecture.

Industry Shift to Software-Defined Vehicles

The launch aligns with the broader move toward software-defined vehicles, where functionality is increasingly delivered through software updates rather than hardware changes. With support for over-the-air (OTA) updates and scalable memory, the Stellar P3E enables continuous feature upgrades over a vehicle’s lifecycle.

The company is targeting a $16 billion automotive MCU market opportunity by 2030, driven by electrification, ADAS, and SDVs.

Why 28nm Still Matters: ST Explains Its Node Strategy

When asked about ST’s decision to use a 28-nanometer process node at a time when competitors are pushing toward more advanced nodes, they clarified that while advanced nodes are typically optimised for maximum compute efficiency, they are not always cost-effective for automotive applications that require a balance of digital processing and analogue functionality.

The company stated that 28nm represents a “sweet spot” where both analogue performance and digital complexity can be efficiently integrated. It also highlighted its advantage in embedding large memory at this node, leveraging what it described as one of the densest technologies in the industry.

On the supply chain front, ST emphasised its vertically integrated manufacturing strategy. The 28nm technology used for Stellar P3E is produced at its high-capacity facility in Crolles, France, allowing the company to retain greater control over production.

Unlike reliance on external foundries, which are currently under pressure from AI-driven demand, ST’s in-house manufacturing enables it to prioritise automotive and industrial customers. The company also noted its dual-sourcing strategy for automotive MCUs at every stage of production to enhance resilience.

The post STMicroelectronics Unveils AI-Enabled ‘Stellar P3E’ MCU, Backs 28nm Strategy for Cost and Supply Chain Stability appeared first on ELE Times.

R&S amplifiers enable high-field immunity testing expansion at IB Lenhardt Lab

IBL Lab GmbH, the DAkkS (Deutsche Akkreditierungsstelle GmbH) accredited EMC test laboratory of IB Lenhardt AG, has significantly expanded its high-field immunity testing capabilities with a substantial investment in a suite of high-power amplifier systems from Rohde & Schwarz. This upgrade directly addresses increasing demands from the defence sector for rigorous and realistic testing compliant with standards like MIL-STD-461, AECTP-500, VG 95373 and VG 95370.

The core of this optimisation lies in the deployment of the R&S BBA300-FG180 amplifier (6-18 GHz), coupled with a Schwarzbeck HWRD650 EMS antenna through a direct-mount configuration. This approach eliminates RF cable losses, enabling IBL Lab to achieve field strengths exceeding 400 V/m – a level rarely attained – with a target of surpassing 600 V/m.

The integration of Rohde & Schwarz equipment provides several key advantages for IB Lenhardt. A comprehensive testing range from 9 kHz to 18 GHz is now supported by the integrated system comprising the R&S BBA300-FG180, R&S BBL200A-A5000, R&S BBA150-BC2000, and R&S BBA300-DE1000 amplifiers. Direct antenna mounting on the BBA300-FG180 maximises power transfer and significantly boosts field strength in the 6-18 GHz range, a capability crucial for demanding defence applications.

As Florian Schmidt, Head of Department EMC at IBL Lab GmbH, explains: “Direct antenna mounting on the BBA300-FG180 was the key to achieving field strengths exceeding 400 V/m in the 6–18 GHz range. Combined with our other amplifiers, this setup enables high-field immunity testing across the entire frequency range from 9 kHz to 18 GHz for demanding defence applications.”

Furthermore, amplifiers like the R&S BBA300-FG180 and R&S BBA300-DE1000 offer wide frequency coverage alongside high linearity, while the R&S BBL200A-A5000 delivers 5 kW of continuous power with 100% mismatch tolerance. Leveraging Rohde & Schwarz’s reputation for precision and reliability reinforces IBL Lab’s DAkkS accreditation (ISO/IEC 17025) and NATO CAGE Code (CNH80), bolstering confidence in test results.

Finally, IBL Lab’s position as one of the first laboratories globally to operate the R&S BBA300-DE1000 demonstrates a commitment to utilising cutting-edge testing capabilities. Daniel Lenhardt, CEO of IB Lenhardt AG, says: “High field strengths and stable RF signals are essential for realistic and reliable immunity testing, underscoring the strategic importance of this investment. The combination of high performance and broad frequency coverage positions IBL Lab to effectively serve manufacturers of defence, aerospace, automotive, and industrial electronics requiring advanced RF immunity validation.”

The post R&S amplifiers enable high-field immunity testing expansion at IB Lenhardt Lab appeared first on ELE Times.

India’s Electronics Powerplay: Why 2026 Will Lead the Way for the Industry

India’s electronics and semiconductor sector is currently experiencing a significant turning point in its trajectory. This transformation is primarily fuelled by key government initiatives such as the Production Linked Incentive (PLI), Electronic Manufacturing Clusters Scheme (EMCS), and Design Linked Incentive (DLI) schemes. In addition, the sector is benefiting from the realignment of global supply chains towards India and the anticipated growth in domestic demand. As a result of these factors, industry projections indicate that the sector is on track to reach a market value of US$500 billion by the year 2030. This rapid evolution signifies India’s transition from being a consumption-driven market to emerging as a prominent global centre for innovation, manufacturing excellence, and intellectual property (IP) development.

At the core of this momentum are events such as Electronica India and Productronica India, which are organised by Messe Muenchen India. These platforms have transformed beyond mere trade shows and have become pivotal drivers of industry advancement. By bringing together policymakers, international investors, pioneers, suppliers, and producers in a single setting, these events facilitate more than just conversations. They lead to tangible results such as establishing new collaborations, transferring technology, integrating supply chains, and translating policies into market opportunities that enhance India’s electronics value chain.

In a highly insightful discussion, the President of IMEA (India, Middle East, Africa) at Messe München, along with the CEO of Messe München India, sheds light on India’s remarkable journey from a consumption-oriented market to a prominent global electronics manufacturing hub. Recognising the imperative need to keep pace with the swiftly evolving industry landscape, electronica India and productronica India are making a strategic shift to a biannual schedule commencing from April 2026 in Greater Noida. These cutting-edge platforms, revered as “decision-grade” marketplaces, are strategically designed to streamline the supply chain operations, showcasing over 400 exhibitors and fostering collaborative partnerships, technological advancements, and bolstering domestic production capabilities.

In a recent conversation with Bhupinder Singh, President of India, Middle East, and Africa at Messe München, as well as the Chief Executive Officer of Messe München India, we discussed…

ELETimes: India’s electronics landscape has evidently undergone a significant transformation. In your opinion, which pivotal shift do you believe is driving the market trends presently?

Bhupinder Singh: The crucial transition happening in the current landscape, shifting from intent to execution at a large scale. With capacity increasing, compliance becoming stricter, and decision-making processes becoming more efficient, the market must enhance its capability to assess technologies, validate partners, and smoothly progress from planning to implementation without delays caused by evaluating multiple vendors. In such a dynamic setting, business platforms should not only bring stakeholders together but also facilitate productive outcomes.

ELETimes: What sets electronica India and productronica India apart as marketplaces in 2026?

Bhupinder Singh: Our role is to simplify a complex supply chain by reducing friction. Given the deeply interconnected nature of electronics manufacturing, Electronica India and Productronica India bring the entire value chain into a single, focused environment—enabling companies to evaluate solutions end-to-end, align cross-functional stakeholders, and make more confident decisions. Ultimately, this is not just a showcase, but a purpose-built, decision-grade marketplace.

ELETimes: What level of scale and participation can the industry anticipate from the April 2026 editions?

Bhupinder Singh: Scale matters—but what truly drives outcomes is decision density. The April 2026 edition is built around high-intent engagement, bringing together 400+ exhibitors representing over 1,000 companies from 20+ countries, connecting with an expected 30,000+ trade attendees. Through live demonstrations, operational equipment, supplier interactions, and structured meetings, participants can evaluate solutions in a focused setting. With multiple options available in one place, teams can benchmark more efficiently, compare with greater accuracy, and accelerate decision-making. In effect, the event condenses months of fragmented vendor assessments into a few days of meaningful, high-value evaluation—because attendees don’t come to browse; they come to make decisions.

ELETimes: What prompted the shift to hosting two editions each year at this point?

Bhupinder Singh: The pace of the industry has fundamentally shifted. Product cycles are shorter, supplier qualification is more stringent, and project timelines leave far less room for delay. A single annual—or even biennial—touchpoint no longer reflects how companies make decisions, build, and scale today.

This transition also aligns with the momentum driven by India’s PLI and ECMS schemes, which are accelerating investments across electronics components, products, and systems manufacturing, while enabling faster capacity expansion across regions.

Taking all of this into account, from 2026 we are moving to a biannual format: Greater Noida in April and Bengaluru in September—two key markets, two distinct buying cycles, and two strategic opportunities each year to evaluate solutions, strengthen partnerships, and fast-track implementation.

ELETimes: What new opportunities does a biannual format create for exhibitors?

Bhupinder Singh: It creates three distinct advantages: speed, precision and responsiveness.

First, pipeline velocity improves—exhibitors can engage buyers more frequently, which directly supports conversion.

Second, regional precision—North and South are both high-opportunity, but they operate differently in procurement cycles and ecosystem density.

Third, market responsiveness—brands can launch updates, gather feedback and recalibrate strategy with far less lag. In electronics, speed is not a nice-to-have. It’s a competitive advantage.

And for visitors, it means access. If you’re sourcing, building, or scaling in India, you don’t have to wait for a single annual sourcing window. You can qualify suppliers, shortlist faster and keep projects moving with a six-month rhythm.

ELETimes: The April edition is being hosted in Uttar Pradesh—what new value or advantage does this bring to the event?

Bhupinder Singh: Hosting changes the quality of engagement. With Uttar Pradesh as host, the presence of relevant government departments and institutional stakeholders becomes structural—not optional. For international and domestic participants, a host state context brings sharper visibility on facilitation and readiness—so expansion conversations move from exploratory to executable

ELETimes: The event will be inaugurated by Hon’ble Chief Minister of Uttar Pradesh, Shri Yogi Adityanath—what message does this send to the broader industry?

Bhupinder Singh: It reflects a clear strategic commitment. Electronics sits at the core of national competitiveness and industrial growth, and the strength of state ecosystems increasingly determines the pace of progress. An inauguration led by the Chief Minister underscores electronics as a priority growth engine. For the market, this sends a strong signal—it boosts confidence and enhances the overall business environment surrounding the marketplace.

ELETimes: Uttar Pradesh has also unveiled targeted initiatives at Electronica India and Productronica India 2026. What makes these events the right platform for such announcements?

Bhupinder Singh: The aim is to elevate engagement beyond generic networking and create structured access. These initiatives are designed to raise the signal-to-noise ratio and make engagement more purposeful:

- UP Electronics Leadership Summit: A closed-door gathering of 100+ CEOs to accelerate top-level partnership and investment conversations

- CM-Meet: An invite-only leadership roundtable to align on priorities and collaboration themes

- 1: 1 meeting with international companies: To foster and accelerate alliances, JVs and market-entry conversations.

- Startup Showcase: 20+ startups to connect innovation with adoption and manufacturing capability

ELETimes: How international is the 2026 edition—practically speaking?

Bhupinder Singh: You’ll see a genuinely global footprint—strong participation across Asia, Europe and the US—bringing better benchmarking and more partnership options. As we progress toward the event, we are building toward the planned scale of 400+ exhibitors from 20+ countries.

For visitors and exhibitors alike, this matters because international presence improves benchmarking, expands partnership options, and raises the standard of technical and commercial discussions.

ELETimes: What does “end-to-end ecosystem” actually translate to on the show floor?

Bhupinder Singh: It translates to a complete, decision-ready view of electronics manufacturing—where stakeholders can assess both upstream and downstream implications and qualify partners with confidence. That includes components and modules, SMT and assembly, automation, test and inspection, embedded hardware and connectivity, EMS capabilities, and the factory disciplines that protect yield and reliability—cleanroom readiness, ESD control, safety systems and process consistency. The point isn’t variety. The point is readiness because electronics outcomes are not driven by one technology choice—they are driven by how choices perform together across the production flow.

ELETimes: You also announced a significant milestone for India’s PCB ecosystem—BPCA 2026 in collaboration with ELCINA. What shift does this represent?

Bhupinder Singh: We’ve formally launched the next phase of BPCA 2026—Bharat’s dedicated platform for Printed Circuit Boards and Assemblies—in partnership with ELCINA (Electronic Industries Association of India). As part of this transition, the India PCB Tech Conference will be rebranded as the Bharat PCB Tech Conference, creating a stronger national platform aligned with global standards and manufacturing readiness. With BPCA joining Electronica India and Productronica India 2026, we are shaping a more focused, future-ready PCB ecosystem under one roof.

ELETimes: Where does the Bharat Electronics Yatra fit into the larger strategy?

Bhupinder Singh: The Yatra is about building market readiness before the event and expanding engagement beyond the venue. It takes the conversation directly to the clusters and decision-makers, captures on-ground perspectives, and drives awareness across the broader production chain. The outcome is better participation quality: a more informed audience, sharper buyer intent and a show floor aligned to real needs. It’s a pipeline builder, pulling the ecosystem in—focused on relevance and ensuring this trade forum remains connected to the market between editions.

ELETimes: Final message—what makes the April 2026 editions of electronica India 2026 and productronica India 2026 essential fixtures on every serious industry calendar?

Bhupinder Singh: Because India is no longer “next”—it is now. Capacity is expanding, standards are sharpening, and scale is accelerating faster than most markets can track. In such a cycle, advantage belongs to those who evaluate rigorously and secure the right partners early. electronica India and productronica India are designed as decision-grade marketplaces—where technologies are benchmarked live, and partnerships move swiftly from discussion to commitment. And in April 2026, Greater Noida is where market leaders go not just to get ahead—but to stay ahead.

The post India’s Electronics Powerplay: Why 2026 Will Lead the Way for the Industry appeared first on ELE Times.

Renesas Launches First Bidirectional 650V-Class GaN Switch For Multiple Uses

Renesas Electronics Corporation, a premier supplier of advanced semiconductor solutions, unveiled the industry’s first bidirectional switch using depletion-mode (d-mode) GaN technology, capable of blocking both positive and negative currents in a single device with integrated DC blocking. Targeting single-stage solar microinverters, AI data centres, and onboard electric-vehicle chargers, the high-voltage TP65B110HRU dramatically simplifies power-converter designs. It replaces conventional back-to-back FET switches with a single low-loss, fast-switching, easy-to-drive device.

Single-Stage Topology Boosts Efficiency, Reduces Components

Today’s high-power conversion designs use unidirectional silicon or silicon carbide (SiC) switches, which block current in only one direction when in the off state. As a result, power conversion must be divided into stages with multiple switched bridge circuits. For example, a typical solar microinverter uses a four-switch full bridge to convert from DC to DC for the first stage, followed by a second stage to produce the final AC output to the grid. Even as the electronics industry moves toward more efficient single-stage converters, engineers must work around inherent switching limitations. Many of today’s single-stage designs use conventional unidirectional switches back-to-back, resulting in a fourfold increase in switch count and reduced efficiency.

Bidirectional GaN changes this landscape entirely. By integrating bidirectional blocking functionality on a single GaN product, power conversion can be achieved in a single stage using fewer switching devices. A typical solar microinverter, for example, will require only two high-voltage Renesas SuperGaN® bidirectional devices, eliminating the intermediary DC-link capacitors and cutting the switch count by half. In addition, GaN products switch fast, with low stored charge, enabling higher switching frequencies and higher power density. In a real-world single-stage solar microinverter implementation, the new GaN architecture demonstrated higher than 97.5 per cent power efficiency with the elimination of back-to-back connections and slow silicon switches.

Combining Robust Performance and Reliability with Silicon-Compatible Drivers

Renesas’ field-proven 650V SuperGaN devices are based on a proprietary normally-off technology that is simple to drive and highly robust. The TP65B110HRU combines a high-voltage bidirectional d-mode GaN chip co-packaged with two low-voltage silicon MOSFETs with high threshold voltage (3V), high gate margin (±20V), and built-in body diodes for efficient reverse conduction. Compared with enhancement-mode (e-mode) bidirectional GaN devices, the Renesas bidirectional GaN switch offers compatibility with standard gate drivers that require no negative gate bias. This translates to a simpler, lower-cost gate loop design and fast, stable switching in both soft and hard switching operation without a performance penalty. Power conversion topologies that require hard switching, such as the Vienna-style rectifier, can benefit from its high dv/dt capability of >100 V/ns, with minimum ringing and short delays during on/off transitions. The Renesas GaN device enables true bidirectional switching with high robustness, high performance and ease of use.

“Extending our SuperGaN technology to the bidirectional GaN platform marks a major shift in power conversion design norms,” said Rohan Samsi, Vice President, GaN Business Division at Renesas. “Customers can now achieve higher efficiency with fewer switching components, smaller PCB area and lower system cost. At the same time, they can accelerate design by leveraging Renesas’ system-level integration with gate drivers, controllers and power management ICs.”

Key features of the TP65B110HRU:

- ±650V continuous peak AC and DC rating, ±800V transient rating

- 2kV Human Body Model ESD protection rating (HBM and CDM)

- 110 mΩ typical RSS,ON @ 25⁰C

- 3V typical Vgs(th)

- No negative drive required

- ±20V maximum Vgs

- >100 V/ns dv/dt immunity

- 1.8V, VSS,FW freewheeling diode voltage-drop

- TOLT top-side cooled package with industry standard pin-out

The post Renesas Launches First Bidirectional 650V-Class GaN Switch For Multiple Uses appeared first on ELE Times.

Government’s Rs. 33,600 crore BHAVYA Scheme Strengthens India’s Electronics, Components, Semiconductor Manufacturing Industries: ELCINA

The Electronic Industries Association of India (ELCINA), India’s leading association of electronics manufacturers, welcomes the Government’s announcement of the Bharat Audyogik Vikas Yojana (BHAVYA) scheme, with a Rs. 33,600 crore outlay, aimed at developing India’s industrial manufacturing ecosystem. The BHAVYA scheme would support India’s transformation into a globally competitive, self-reliant electronics, components, and semiconductor ecosystem.

Welcoming the BHAVYA scheme, Rajoo Goel, Secretary General, ELCINA, said: “The Government has announced the BHAVYA scheme at an opportune time and stands to significantly strengthen the ecosystem and the value chain. Through cluster-based promotion, BHAVYA can co-locate OEMs, component suppliers, logistics providers, and service providers within the same industrial park, which is exactly what a deeper ecosystem for electronics and semiconductors requires. At ELCINA, we are excited to see how this scheme will transform the industry over the next few years.”

ELCINA President, Dr Sasikumar Gendham, lauded the scheme as “it would complement the EMC Schemes of MeitY under which several Electronics Manufacturing Clusters had been initiated and industries set up. BHAVYA would catalyse this further and suggested that existing Clusters should also be allowed to benefit from the Scheme and enhance their infrastructure further”.

The plug-and-play industrial ecosystems will help industry players – both existing and new – cut down on the setup phase and move more quickly towards production. Additionally, with streamlined approvals, effective single-window systems, and investor-friendly reforms led by states, the industry would be in a better position to address the critical need to reduce import dependence and position the country as a credible export and supply-chain hub.

ELCINA also lauds the Government’s broader goals of job creation, investment, and economic growth across states. BHAVYA is expected to enhance the supply chain while creating new opportunities for Indians who stand to benefit from the country’s manufacturing growth, particularly in the electronics sector.

The post Government’s Rs. 33,600 crore BHAVYA Scheme Strengthens India’s Electronics, Components, Semiconductor Manufacturing Industries: ELCINA appeared first on ELE Times.

Microchip Announces New BZPACK mSiC Power Modules with HV-H3TRB Reliability Standards

The post Microchip Announces New BZPACK mSiC Power Modules with HV-H3TRB Reliability Standards appeared first on ELE Times.

Mythic and Microchip Partner to Redefine AI Processing with Next-Gen Analogue Compute-in-Memory Technology.

One hundred fifty billion units of SST SuperFlash technology that Mythic is licensing have been shipped to date. SuperFlash technology is the de facto eNVM solution for a broad spectrum of industries, including industrial, automotive, consumer, and computing, for critical data and code storage, and is licensed by all of the top 10 semiconductor foundries worldwide.

“Mythic is pioneering innovative solutions in AI inference processing and AI sensor fusion for industrial, automotive and data centre applications, effectively overcoming current AI power limitations,” said Mark Reiten, vice president of Microchip’s Edge AI business unit. “As the core memory technology for Mythic’s next-generation products, memBrain delivers significant power efficiency and high performance for both edge and data centre applications.”

The memBrain cell features:

- Up to 8 data bits per bitcell (8 bpc) storage

- Single-digit nanoamp (nA) bitcell read current

- 10-year data retention at operating temperature

- 100,000 endurance cycles

- Full state machine control of the 8 bpc multi-state write operation

- Single-cycle multiply-and-accumulate operations for aCIM

“Mythic selected SST after an industry-wide search of eNVM technologies and determined the memBrain cell technology best enabled us to achieve the ultra-low-power and high performance required by our customers,” said Dr Taner Ozcelik, Mythic’s chief executive officer. “Additionally, the wide foundry availability of its industry-proven SuperFlash technology, coupled with the outstanding support of the SST engineering team, has been invaluable during our product development cycle.”

SST’s memBrain technology has been developed and deployed in 40 nm and 28 nm foundry processes using production-ready SuperFlash memory. 22 nm memBrain development is planned to extend the technology roadmap. Designed to provide reliable, high-performance and low-power non-volatile storage directly on the chip, SuperFlash memory is widely used in applications that require fast access times, high endurance and data retention without the need for external memory components.

The post Mythic and Microchip Partner to Redefine AI Processing with Next-Gen Analogue Compute-in-Memory Technology. appeared first on ELE Times.

The new performance bottleneck: How more GPU memory unlocks next-gen gaming and AI PCs

Courtesy: Micron

The next era of PC performance will be defined not by more compute, but by memory scale. The rising size of game assets and AI models has outpaced GPU memory capacity until now. Micron’s latest evolution of GDDR7 marks a pivotal shift for next-generation GPUs by combining higher memory density with the scalability that modern gaming and AI workloads now demand. With expanded capacity options built to support configurations up to 96GB of graphics memory, this generation of GDDR empowers systems to keep vastly larger worlds, richer textures, and growing AI models resident in memory, reducing bottlenecks and unlocking more consistent real-time performance across high-fidelity games and AI-enhanced applications.

Visual computing: The convergence of graphics and intelligence

Visual computing is entering a new era as graphics and intelligence converge. Modern systems must not only render high-fidelity scenes in real time, but also interpret, enhance, and generate content using increasingly complex AI models. Two forces are accelerating this shift: the push toward cinematic quality gaming and the rapid emergence of AI-powered PCs. As worlds grow larger, textures more detailed, and on-device AI more integral to responsiveness and personalisation, the demands placed on GPU memory have surged. What that means is, memory capacity and efficiency now determine how smoothly a system can deliver immersive gameplay, intelligent creation tools, and real-time simulation, making memory a foundational enabler of next-generation visual computing.

Delivering unprecedented performance for high-resolution gaming

Modern games are pushing GPU architectures harder than ever. Real-time ray tracing demands continuous access to massive datasets, geometry, materials, lighting maps, and shadows, while high refresh rate displays and ultra-resolution textures multiply the data the GPU must process each frame. Add in sprawling open worlds and increasingly AI-assisted rendering techniques, and the result is a workload that easily overwhelms traditional memory limits.

The problem is that when GPU memory can’t hold all this data at once, the system is forced to constantly swap assets in and out. That leads to the issues gamers know too well: texture pop-in, mid-frame stutters, uneven frame times, and sudden drops during intense ray-traced scenes. AI-generated frames and upscaling pipelines also become less consistent when memory is constrained, because the models and intermediate buffers they rely on are constantly competing for space.

This is where next-generation GDDR capacity and bandwidth become critical. By enabling far larger datasets to remain resident in memory, GDDR7 keeps the entire visual pipeline fed: textures, lighting data, geometry sets, and AI inference models, without the bottlenecks that cause visual artefacts or performance instability. The result is smoother, more predictable real-time rendering at 4K, 5K, and 8K, even in the most demanding scenes.

To keep these visual pipelines running efficiently, the memory subsystem must deliver data rapidly and consistently.

Enabling larger, more detailed worlds with 24Gb die density

As game environments expand and visual assets grow, memory capacity becomes critical to maintaining seamless, artefact-free experiences. Micron’s new 24Gb die density enables up to 96GB of graphics memory, giving GPUs significantly more space for high-resolution textures, expansive worlds, and advanced visual effects.

This increased capacity matters to gamers because:

- Reduces asset swapping and texture pop-in

- Supports larger frame buffers for high-resolution displays

- Enables richer, more detailed environments with fewer loading transitions

Creators and professional users also benefit from faster real-time rendering, more responsive GPU-accelerated workflows, and improved handling of large datasets.

Fueling AI-enhanced graphics and the rise of AI PCs

AI is rapidly becoming integral to personal computing. Neural rendering, real-time media enhancement, content generation, and AI-assisted workflows place new demands on system memory. Micron GDDR7 is built to support these emerging workloads with increased bandwidth, lower latency, and improved efficiency.

Why GDDR7 matters for AI PCs

AI-driven graphics and compute tasks rely on continuous movement of large datasets. GDDR7 accelerates these operations by improving throughput and responsiveness across GPU pipelines.

Systems built with GDDR7 benefit from:

- Faster on-device AI inference for creation, media, and collaboration

- Lower-latency performance across hybrid CPU-GPU-NPU workflows

- Higher throughput for neural graphics and generative AI models

- Improved power efficiency thanks to architectural refinements and reduced operating voltages

As AI becomes embedded into everyday PC tasks from writing, coding, editing, presenting, and gaming, memory performance will heavily influence the immediacy, intelligence, and fluidity of the experience.

Enabling the future of immersive and intelligent computing

Micron GDDR7 is more than a performance improvement; it is a foundational technology for the next decade of visual and AI computing. With 36 Gbps bandwidth, 24Gb die density, and improved efficiency, GDDR7 empowers GPU and AI PC vendors to deliver richer, more dynamic, and more intelligent computing experiences.

While NPUs are becoming essential for power-efficient, on-device AI acceleration, the most demanding visual and AI workloads still rely on the scale and parallelism of a discrete GPU. NPUs excel at sustained, low-power inference, but GPUs deliver significantly higher throughput for large models, neural graphics, advanced rendering, and gaming workloads. By pairing NPUs with discrete GPUs equipped with GDDR7, AI PCs can intelligently distribute tasks, assigning lightweight inference to the NPU while leveraging the GPU’s computing power and memory bandwidth for operations that require maximum performance. This combination unlocks capabilities far beyond what NPUs can achieve alone.

Together, Micron GDDR7 and the next wave of discrete GPUs set the stage for a new era of immersive graphics and high-performance AI computing.

The post The new performance bottleneck: How more GPU memory unlocks next-gen gaming and AI PCs appeared first on ELE Times.

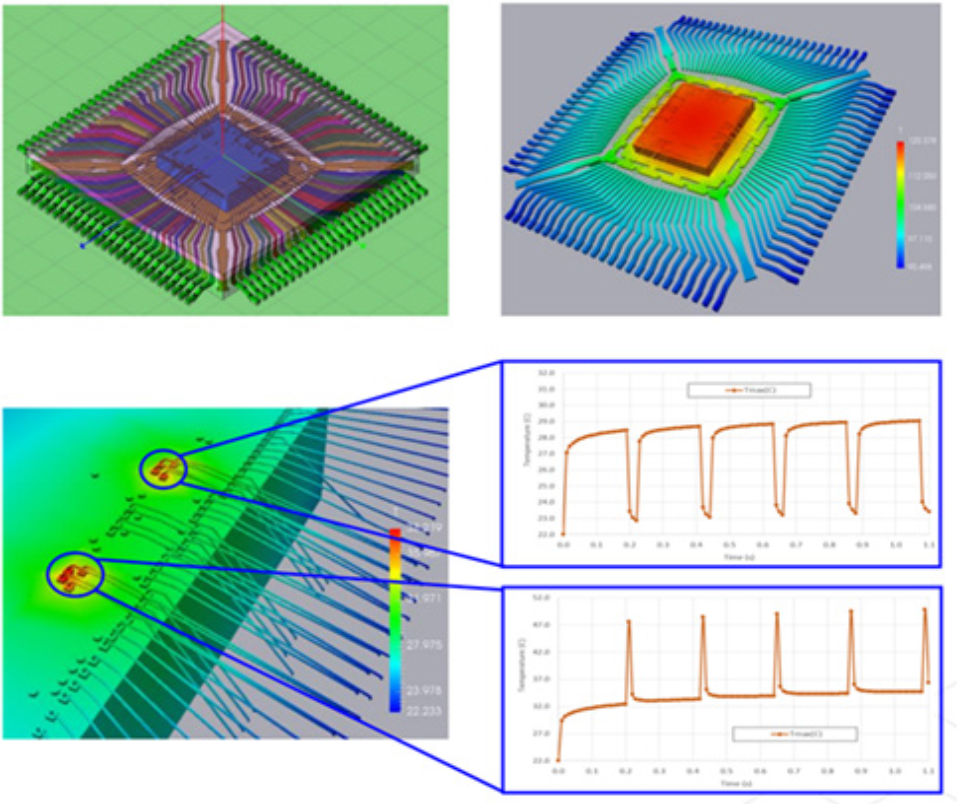

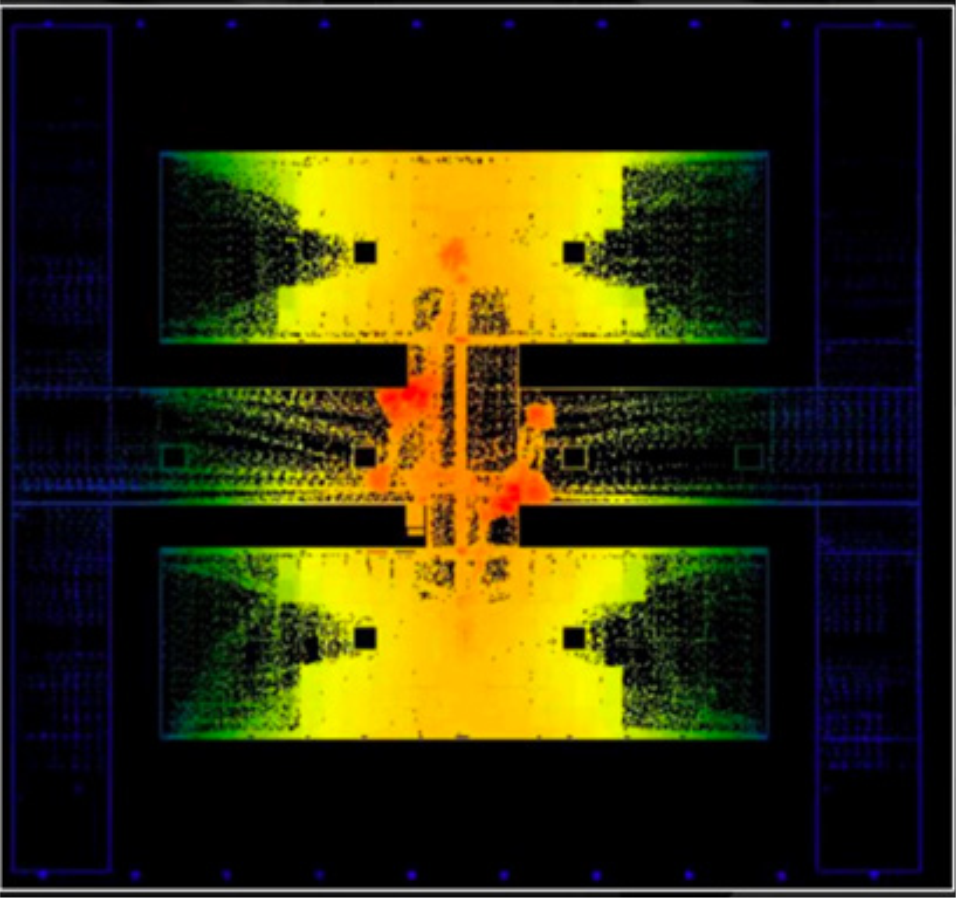

Thermal Management in 3D-IC: Modelling Hotspots, Materials, & Cooling Strategies

Courtesy: Cadence

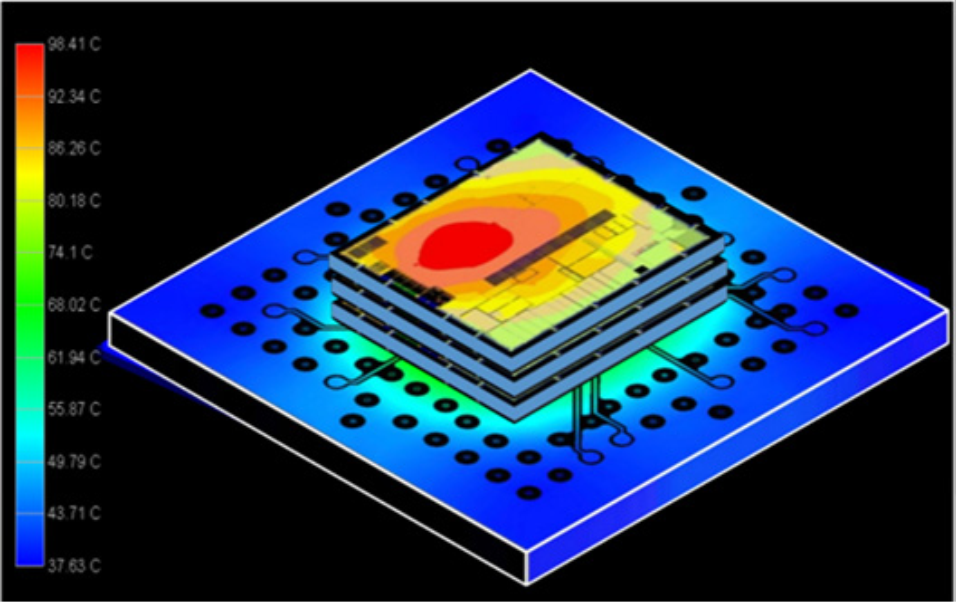

As three-dimensional integrated circuit (3D-IC) technology becomes the architectural backbone of AI, high-performance computing (HPC), and advanced edge systems, thermal management has shifted from a downstream constraint to a fundamental design driver. The dense vertical integration that enables unprecedented performance also concentrates heat at levels that traditional two-dimensional design methodologies cannot anticipate or mitigate. In fact, the temperatures and heat fluxes inside localised 3D-IC hotspots can approach fractions of those encountered in rocket-launching thermal zones, only here the challenge unfolds on a microscopic silicon landscape rather than within a combustion chamber. This extreme thermal intensity makes early and predictive planning essential rather than optional.

Effective thermal management now begins at the architecture definition stage, where designers evaluate stack feasibility, power distribution, and allowable thermal envelopes before committing to partitioning decisions. These early insights directly shape block placement, power-delivery topology, and the choice of materials, interposers, and packaging technologies. As the industry increasingly relies on vertically integrated systems to achieve performance-per-watt gains, thermal awareness emerges as an architectural discipline in its own right, one that guides every subsequent stage of the 3D-IC design flow.

This article guides modelling, estimating, and mitigating thermal challenges in dense stacks and interposer-based 3D-ICs, with an emphasis on early electrothermal strategies that scale with complexity.

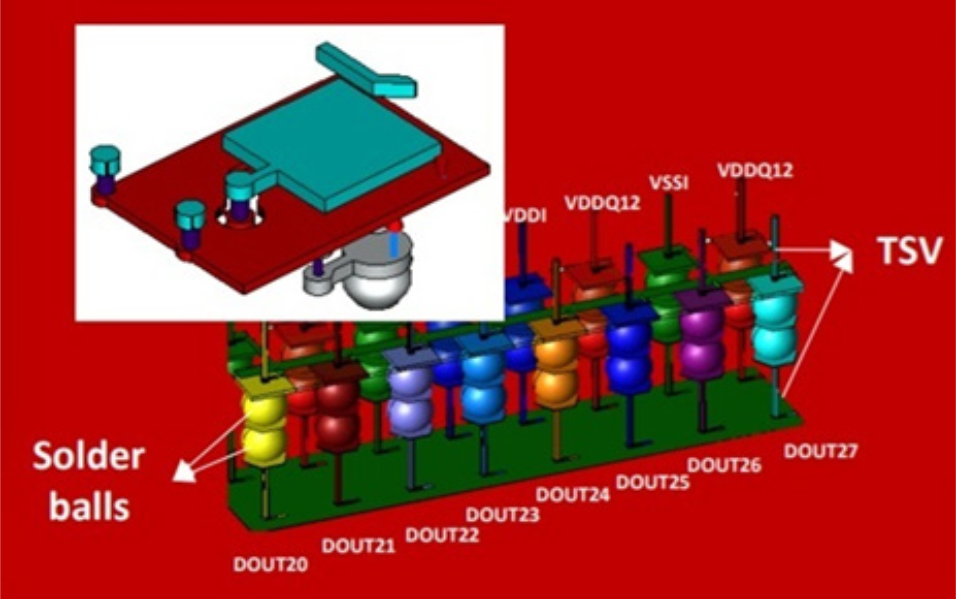

Sources of Heat in Stacked Architectures

Heat in 3D-ICs arises from a combination of device activity, vertical power density, and material constraints. When logic, memory, and accelerators are stacked, the total power per unit footprint increases dramatically. Upper dies, which are furthest from the heatsink, experience higher thermal resistance and reduced cooling efficiency, creating natural hotspots even when their individual power numbers appear modest.

The placement of through-silicon via (TSV) arrays, micro-bumps, and interconnect pillars also shapes the heat landscape. These structures act not only as electrical conduits but also as thermal conduits, depending on the material and density. Die-to-die interfaces with bonding layers often introduce thermal bottlenecks, and when chiplets operate at different power states, steep thermal gradients can trigger stress and reliability concerns. Understanding these interactions early is essential for setting realistic thermal limits and performance expectations.

Early Compact Models and Power Map Estimation

Thermal analysis must begin in parallel with the architectural definition itself. Early-stage compact models enable architects to approximate temperature distributions using only high-level power budgets, long before physical implementation. By capturing the combined influence of die thickness, material stacks, bonding interfaces, and interposer conductivity, these models reveal whether planned power densities or proposed die-stack configurations are thermally realistic. They help flag infeasible assumptions early, ensuring that functional partitioning and stacking choices are guided by thermally credible boundaries rather than late-stage surprises.

Creating usable power maps at this stage does not require full register transfer level (RTL) activity vectors. Coarse workload profiles can yield first-order estimates of dynamic and leakage power. When combined with simplified geometry models, they highlight thermally sensitive regions, enabling design teams to adjust block partitioning, die assignment, and approximate placement before entering the detailed implementation phase.

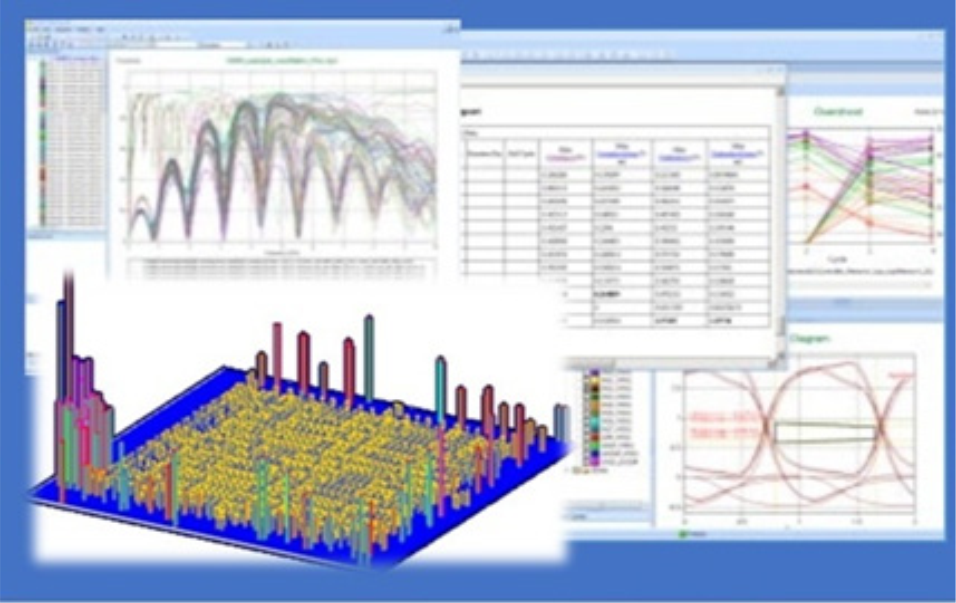

Cadence’s multiphysics system analysis ecosystem connects power estimation, compact thermal model (CTM) modelling, and system-level thermal analysis, ensuring that signal, power, electromagnetic (EM), and thermal assumptions remain aligned throughout the early design phase. This early visibility reduces late-stage thermal surprises, which are often the costliest to rectify.

Heat Paths Through Dies, Interposers, and Package

Heat does not follow a single escape route in a 3D-IC. Instead, it propagates through a network of vertical and lateral paths whose efficiency depends on materials, die arrangement, and the package environment. Lower dies may benefit from direct contact with the heatsink, while upper dies rely on indirect conduction through intermediate layers. Thermal resistance builds cumulatively across each interface.

Interposers, whether made of silicon, glass, or organic materials, play a significant role in the heat flow picture. Silicon interposers offer superior thermal conductivity, enabling heat spreading but also concentrating thermal load where chiplets cluster. Organic interposers introduce more thermal resistance but offer other integration advantages. Achieving the correct tradeoff means modelling these layers as active participants in heat distribution, not static mechanical components.

The entire package, including substrate layers, heat spreaders, and lid materials, must also be included in thermal simulation. When package effects are omitted in early analysis, temperature predictions often skew optimistic, masking hotspots that emerge only after assembly-level modelling is performed.

Materials, TIMs, and Cooling Options for Stacks

Thermal simulation heavily relies on the structural definition of a product because the geometry, material properties, and assembly details directly dictate how heat is generated, transferred, and dissipated.

High-conductivity silicon, optimised interconnect materials, and improved underfill or bonding layers can lower the vertical thermal resistance of a stack. Thermal interface materials (TIMs) exhibit significant variations in performance, and even slight differences in thickness or coverage can result in substantial temperature differences across dies.

Cooling strategies for 3D-ICs are evolving rapidly. Traditional air cooling can be sufficient for moderate power budgets, but high-performance AI and HPC systems often require advanced approaches such as direct liquid cooling or vapour chamber solutions. The choice of cooling strategy should align with the power roadmap, not just the current generation’s requirements. Once a die stack is assembled, cooling options become constrained, so decisions made early influence the thermal feasibility of future product iterations.

Co-Optimisation with Placement and PDN Design

Thermal constraints directly influence floorplanning, macro placement, and power delivery network (PDN) topology in 3D-ICs. Efficient heat spreading is achieved when high-power blocks are positioned to maximise vertical conduction paths and lateral spreading through metal layers. If a block is placed too far from major thermal conduits, even robust cooling cannot compensate for the heat.

The PDN adds additional complexity. Power delivery structures, including TSVs, bumps, and interposer redistribution layers, introduce their own resistive heating. When modelled jointly with thermal effects, the combined electro-thermal behaviour reveals interactions that neither analysis can capture alone. Co-optimisation across these domains ensures that thermal mitigation does not compromise power integrity and vice versa.

A tightly integrated workflow enables round-trip refinement as power, placement, and package assumptions evolve. Without this iterative co-design, late-stage violations become inevitable, requiring disruptive redesigns.

Electro-Thermal Readiness for Signoff

Before committing a 3D-IC to final signoff, teams must verify that the design can withstand realistic thermal stress across operating modes and process corners. This includes validating that estimated power profiles align with actual activity, ensuring that predicted peak temperatures remain within safe limits, and confirming that no layer or interface exceeds its thermal reliability threshold.

Die-to-die boundaries, micro-bump arrays, TSV clusters, and package interconnects must be evaluated holistically, since minor thermal mismatches can accumulate into significant mechanical strain. Long-term reliability also depends on understanding how temperature interacts with electromigration, ageing, and performance drift over the product lifetime.

A complete electro-thermal signoff process provides the confidence needed before entering manufacturing, reducing field failures and ensuring long-term stability.

Designing for Thermal Scalability

3D-ICs deliver unprecedented performance, but they require a disciplined and predictive approach to thermal management. Success depends on treating heat as a first-order design variable, not a late-stage correction. Early modelling, accurate power estimation, careful material and stack selection, and co-optimisation across placement, PDN, interposer, and package all contribute to thermal resilience.

As system complexity continues to climb, teams that embed electro-thermal planning into their architecture and implementation flows will deliver higher-performing, more reliable, and scalable 3D-IC designs. Thermal awareness is no longer a specialisation; it is a foundational competency for next-generation semiconductor design.

The post Thermal Management in 3D-IC: Modelling Hotspots, Materials, & Cooling Strategies appeared first on ELE Times.

Keysight Launches AI Inference Emulation Platform to Validate and Optimise AI Infrastructure

Keysight Technologies has introduced Keysight AI Inference Builder (KAI Inference Builder), an emulation and analytics platform designed to validate inference-optimised AI infrastructure at scale. Keysight will demonstrate the solution at NVIDIA GTC, showcasing operation within NVIDIA DSX Air AI factory simulation environments to model and optimise AI data centre infrastructure, architectures, and performance.

As the AI industry shifts from training large language models (LLMs) to deploying them, optimising inference has become a crucial factor for ROI. However, inference behaviour is highly dynamic and difficult to emulate. Traditional testing methods like synthetic traffic generation or GPU benchmarks cannot accurately reproduce the latency-sensitive workload behaviour of AI inferencing across compute, networking, memory, storage, and security layers.

KAI Inference Builder closes that gap by recreating realistic inference workload patterns and modelling industry-specific usage patterns to validate AI infrastructure, applications, and data centre deployments. The platform gives AI cloud providers, hardware vendors, and application developers a scalable solution for measuring, validating, and optimising real-world inference performance.

Key benefits of KAI Inference Builder include:

Built for the Inference Era: As part of the Keysight Artificial Intelligence (KAI) portfolio, KAI Inference Builder emulates AI inference workloads at scale and validates full-stack deployments under real-world conditions to optimise performance, scale, and security.

- Industry- and Application-Specific Benchmarking: Instead of generic emulations, KAI Inference Builder emulates industry-specific usage patterns and LLM architectures for AI models seen in finance, healthcare, and other verticals, enabling organisations to model and analyse infrastructure and application behaviour across different types of AI data centre deployments.

- End-to-End Validation and Optimisation: KAI Inference Builder evaluates inference workflows from user request to model response, helping teams reduce costly rework by identifying and resolving bottlenecks early across compute, network, and security layers.

- Subsystem Isolation and Root-Cause Precision: KAI Inference Builder can also do client-only emulation, which identifies where performance bottlenecks emerge across the AI infrastructure stack under load, enabling targeted optimisation that reduces overprovisioning, lowers costs, and improves overall efficiency.

- NVIDIA DSX Air Integration and Live GTC Demo: Keysight will showcase KAI Inference Builder’s turnkey integration with NVIDIA Air at NVIDIA GTC, generating realistic inference workloads throughout NVIDIA’s data centre simulation environment so operators can validate inference infrastructure before deploying physical equipment.

Ram Periakaruppan, Vice President and General Manager, Network Test & Security Solutions at Keysight, said: “Inference is the key to unlocking AI’s ROI, but that can be challenging to achieve when system resources aren’t optimised for capacity and performance. KAI Inference Builder provides visibility into real-world inference performance across the full stack, enabling customers to validate and optimise deployments before hardware reaches the rack. Showcasing this capability at NVIDIA GTC using NVIDIA’s Air platform demonstrates how organisations can accelerate the path to production while reducing risk and cost.”

Amit Katz, VP of Networking at NVIDIA, said: “As AI data centres scale to unprecedented levels, pre-deployment validation has transitioned from a best practice to a mission-critical requirement. The integration of KAI Inference Builder with NVIDIA DSX Air provides the essential environment needed to eliminate performance volatility and enables NVIDIA AI Factory partners and customers to emulate real inference workloads and preemptively resolve bottlenecks, ensuring optimised AI services reach the market quickly.”

The post Keysight Launches AI Inference Emulation Platform to Validate and Optimise AI Infrastructure appeared first on ELE Times.

STMicroelectronics accelerates global adoption and market growth of Physical AI with NVIDIA

STMicroelectronics announced the acceleration of global development and adoption of physical AI systems, including humanoid, industrial, service and healthcare robots. ST is integrating its comprehensive portfolio for advanced robotics into the reference set of components compatible with the NVIDIA Holoscan Sensor Bridge (HSB). In parallel, high-fidelity NVIDIA Isaac Sim models of ST components are being integrated into both companies’ robotics ecosystems to support faster, more accurate sim-to-real research and development. The first deliverables available to developers today include the integration of Leopard’s depth camera enabled by ST with the NVIDIA HSB and the high-fidelity model of an ST IMU into NVIDIA’s Isaac Sim ecosystem.

“ST is well engaged within the robotics community, providing robust support and a well-established ecosystem,” said Rino Peruzzi, Executive Vice President, Sales & Marketing, Americas & Global Key Account Organization at STMicroelectronics. “Our collaboration with NVIDIA aims to unleash the next wave of cutting-edge robotics innovation with developer and customer experience streamlined at every step, from the inception of AI algorithms to the seamless integration of sensors and actuators. This will accelerate the evolution of sophisticated AI-driven physical platforms.”

“Accelerating the development of next-generation autonomous systems requires high-fidelity simulation and seamless hardware integration to bridge the gap between virtual training and real-world deployment,” said Deepu Talla, Vice President of Robotics and Edge AI at NVIDIA. “The integration of STMicroelectronics’ sensor and actuator technologies with NVIDIA Isaac Sim, Holoscan Sensor Bridge and Jetson platforms provides developers with a unified foundation to build, simulate and deploy physical AI at scale.”

Simplifying sensor and actuator integration with the Holoscan Sensor Bridge

With the NVIDIA HSB, developers can unify, standardise, synchronise, and streamline data acquisition and logging from multiple ST sensors and actuators, a critical foundation for building high-fidelity NVIDIA Isaac models, accelerating learning, and minimising the sim-to-real gap.

The goal is to simplify the process of connecting ST sensors and actuators to NVIDIA Jetson platforms through pre-integrated solutions for the combination of STM32 MCUs, advanced sensors (including IMUs, imagers, and ToF devices) and motor‑control solutions, particularly for humanoid robot designs. Leopard Imaging’s stereo depth camera for robots is the perfect example. Using ST imaging, depth and motion-sensing technologies, it is expected to support a broad wave of designs across Physical AI OEMs, academic research groups and the industrial robotics community.

Reducing cost, complexity, and challenges with high-fidelity modelling for Omniverse Isaac

Advanced robotics developers face high development costs, in addition to modelling challenges. High‑fidelity simulations with extensive randomisation demand substantial GPU and CPU resources and large datasets. Selecting which parameters to randomise, and over what ranges, requires deep domain expertise. Poor choices can result in unrealistic scenarios or inefficient training. Finally, excessive variability can confuse models, slow convergence, and degrade real‑world performance when randomisation no longer reflects plausible conditions.

ST and NVIDIA’s objective is to provide accurate, hardware-calibrated models for the comprehensive portfolio of ST components, matching the requirements of advanced robotics. Following the availability of the first model of an IMU, ST is working to bring developers models of ToF sensors, actuators and other ICs derived from benchmark data collected on real ST hardware, using ST tools to capture accurate parameters and realistic behaviour, resulting in models optimised to NVIDIA’s Isaac Sim ecosystem. NVIDIA HSB is being integrated into ST’s toolchain collaboratively.

As a result, ST and NVIDIA envision that more accurate models will significantly improve robot learning. With models that closely mirror real-world device behaviour, robots can learn from simulations that better reflect actual conditions, shortening training cycles and lowering the cost of building and refining humanoid robotics applications.

The post STMicroelectronics accelerates global adoption and market growth of Physical AI with NVIDIA appeared first on ELE Times.

Socomec Expands Power Solutions Portfolio in India, Launches MASTERYS GP4 UPS and ATyS a M Automatic Transfer Switch

Socomec has announced the launch of its new advanced MASTERYS GP4 UPS and ATyS a M Automatic Transfer Switch. This further strengthens their portfolio of reliable power management solutions. With over 25 years in the industry, the launch reinforces the company’s focus on innovative, efficient technologies for modern infrastructure.

Mr. Meenu Singhal, Regional Managing Director, Socomec Innovative Power Solutions, said,

“The launch of the MASTERYS GP4 UPS and ATyS a M Automatic Transfer Switch strengthens our portfolio with solutions that drive operational continuity and efficiency. From data centres and IT rooms to commercial buildings, organisations require resilient power infrastructure to ensure uninterrupted operations and protect critical systems. These products help optimise power supply while supporting reliable performance. We remain focused on innovation and committed to delivering dependable, future-ready power solutions for our customers.”

MASTERYS GP4 UPS, Designed for Critical Power Environments:

|

The Socomec MASTERYS GP4 200–250 kVA UPS is a high-performance uninterruptible power supply designed to ensure reliable power continuity for mission-critical environments. Built with advanced power protection technology and high-efficiency SiC technology, it delivers superior energy efficiency, consistent power quality, and reliable performance for data centres, industrial operations, and commercial infrastructure requiring uninterrupted operations. |