Новини світу мікро- та наноелектроніки

Cabinet approves Rare Earth Permanent Magnet Manufacturing Scheme, worth Rs. 7,280 crores

The Cabinet approved the Rs. 7,280 crore Rare Earth Permanent Manufacturing Scheme on November 26, Wednesday. This first-of-its kind initiative aims to establish a six thousand metric tonnes per annum of integrated Rare Earth Permanent Magnet manufacturing in the country.

Cabinet Minister Ashwini Vaishnav, highlighted the importance of Earth Permanent Magnets for electric vehicles, renewable energy, electronics, aerospace, and defence applications at a media briefing in New Delhi. The scheme is expected to support the creation of integrated manufacturing facilities, involving conversion of rare earth oxides to metals, metals to alloys, and alloys to finished Rare Earth Permanent Magnet, the Union Minister added.

As the demand for electric vehicles grows, the demand for permanent magnets is expected to double by 2030. Currently India primarily relies on imports to satisfy its requirements for permanent magnets. This new scheme is expected to play a significant role in generating employment, boosting self-reliance, and accelerating the country’s aim to achieve Net Zero by 2070.

The total duration of the scheme will be seven years from the date of award, including a two-year gestation period for setting up an integrated Rare Earth Permanent Magnet manufacturing facility. The scheme envisions allocating the total capacity to five beneficiaries through a global competitive bidding process.

The post Cabinet approves Rare Earth Permanent Magnet Manufacturing Scheme, worth Rs. 7,280 crores appeared first on ELE Times.

Decoding the Future of Electronics with TI India

In an exclusive conversation with Kumar Harshit, Technology Correspondent, ELE Times, Mr. Kumar details how TI is leading the charge in creating a safer, greener, and smarter world through technology contributions from right here in India and shares his perspective on the future skill sets required for electronics engineers to thrive in the age of artificial intelligence.

Santhosh Kumar, President & Managing Director of Texas Instruments India, discusses the core themes of safety, sustainability, and innovation and outlines the transformative role of AI in shaping the next generation of engineering talent.

Here are the excerpts from the conversation:

ELE TIMES: Given the increasing focus on road safety, particularly for two-wheelers, how is TI leveraging technology to create safer and smarter vehicles?

Santhosh Kumar: Two-wheeler safety is critical, as the rider is the most exposed. We focus on leveraging simple, easy-to-deploy sensing technologies to solve real-world problems. For example, ensuring the side stand is retracted before the vehicle moves is a simple technique, often solved with magnetic sensing connected directly to the engine control. Moving to more advanced safety, we utilize radar and multiple sensors to provide warnings for both sides of the road. We also integrate technology that can help slow or stop a vehicle automatically if the car in front suddenly brakes, even if the rider isn’t fully alert. The goal is to either give the vehicle control to avoid a fatal accident or empower the rider with timely warnings.

ELE Times: TI emphasizes collaboration and community-driven innovation. How important are industry events like Electronica in deepening your relationship with the engineering ecosystem?

Santhosh Kumar: These events are vital for two key interactions. First, our engineers love to work directly with the engineers of our customers. This technical bond is the strongest foundation for creating relevant products. Events like this provide an apt platform for us to build and deepen those relationships. Second, we connect with decision-makers and purchase teams to demonstrate the affordability and worthiness of a product as a feature for mass-market products. Ultimately, innovation doesn’t happen in isolation; it comes from interaction within a community and ecosystem, making these floors essential.

ELE Times: The world is demanding greener technology. Could you outline TI’s commitment to sustainability, both in terms of internal operations and product design?

Santhosh Kumar: We are sensitive to the work we do both inside and outside our factories. Internally, we have a goal to be 100% powered by green energy by 2030, and we are well past 30% today. Furthermore, over 90% of our operational waste is diverted from landfills.

From a product design perspective, we are very sensitive to ensuring our products take up the smallest area and consume the least amount of power. We are always optimizing to create the smallest possible MCU with minimal energy consumption. This approach allows our customers to create products that are inherently greener than they would otherwise have been.

ELE Times: Can you introduce us to TI’s innovative product line in the Power management area?

Santhosh Kumar: We are heavily focused on smart, intelligent systems. A prime example is our Battery Management Systems (BMS), designed and developed in collaboration with engineers in India, ensuring power is used exactly as intended. We have several compelling demos on motor control. India has billions of motors running today, and we are showing how to make them run most efficiently, with the lowest possible cost, without sound, and without losses. You can witness these technologies integrated, such as in our two-wheeler demonstration, combining BMS, motor control, and security features. Given the huge push towards industrial and factory automation in India, we are also showcasing numerous technologies adapted for smarter, more secure, and greener appliances for the 1.4 billion people consuming electricity.

ELE Times: Beyond the automotive and industrial sectors, what are the emerging market segments in India that you see offering significant opportunities for TI’s growth?

Santhosh Kumar: We operate across five core segments, and we see growth in all of them. After automotive and broad industrial (which includes medical electronics, where a lot of Indian innovation is happening), the third key segment is personal electronics. This includes audio, video, and speech, where AI is bringing about a tremendous influx of smarter systems. The large bandwidth and data flow driving these first three segments necessitate our involvement in the communication segment, which forms the backbone. Finally, the enterprise business is the fifth segment. We are seeing customers, product creators, and applications happening in all five areas across India.

ELE Times: Texas Instruments India has been a pioneer for over 40 years. Could you detail the strategic role TIPL plays in driving cutting-edge innovation for TI’s global business units?

Santhosh Kumar: TI India is an important entity to our worldwide business. We have architects, product definers, system engineers, analog and RF designers, and application engineers who manage businesses and contribute to the entire value chain. In fact, many TI’s new products today have a significant contribution from India, including end-to-end product development. We have world-class infrastructure, including labs, benches, and all the necessary equipment in Bangalore, to enable us to contribute to the success of these global products.

ELE Times: Can you share a recent technological breakthrough from TI and define what innovation means to Texas Instruments in the context of solving real-world problems?

Santhosh Kumar: A recent breakthrough we are very excited about is our Gallium Nitride (GaN) solutions. For instance, deploying GaN in two-wheeler chargers can shrink their size by one-third compared to existing technology and significantly reduce power consumption and heat generation due to lower leakage.

To us, innovation extends beyond laboratory research; it is about how we look at real-world problems and use technology to solve them, ultimately enhancing people’s quality of life. We have both an opportunity and a responsibility to improve the lives of eight billion people while preserving the planet.

ELE Times: Talent acquisition is key to sustained innovation. What initiatives does TI India have in place to attract and nurture the next generation of core engineering talent?

Santhosh Kumar: Our strategy is to hire the bright talent directly from campuses, which accounts for 80% of our hiring. To feed this pipeline, we have programs like our Women in Semiconductor and Hardware (WiSH) program, which engages female students beginning in their second year of college. This program provides hands-on experience in core engineering disciplines, including design, testing, verification, and validation. We want to allow a large segment of the population to understand what it means to do core engineering and be a part of world-class product development right here in India.

ELE Times: As a leader who has seen India’s electronics landscape evolve over decades, what is your key message for the industry today?

Santhosh Kumar: The key message is to adopt the technologies happening globally and bring in innovation through new products. This is a tremendous opportunity for India to lead the wave of innovation, to solve real-world problems. We can bring innovation in manufacturing, product development, and applications that lift the quality of life for our people here and for the eight billion people worldwide. With the current energy in the ecosystem and the influx of new players, India can play an important role in driving innovation.

The post Decoding the Future of Electronics with TI India appeared first on ELE Times.

Delta-sigma demystified: Basics behind high-precision conversion

Delta-sigma (ΔΣ) converters may sound complex, but at their core, they are all about precision. In this post, we will peel back the layers and uncover the fundamentals behind their elegant design.

At the heart of many precision measurement systems lies the delta-sigma converter, an architecture engineered for accuracy. By trading speed for resolution, it excels in low-frequency applications where precision matters most, including instrumentation, audio, and industrial sensing. And it’s worth noting that delta-sigma and sigma-delta are interchangeable terms for the same signal conversion architecture.

Sigma-delta classic: The enduring AD7701

Let us begin with a nod to the venerable AD7701, a 16-bit sigma-delta ADC that sets a high bar for precision conversion. At its core, the device employs a continuous-time analog modulator whose average output duty cycle tracks the input signal. This modulated stream feeds a six-pole Gaussian digital filter, delivering 16-bit updates to the output register at rates up to 4 kHz.

Timing parameters—including sampling rate, filter corner, and output word rate—are governed by a master clock, sourced either externally or via an on-chip crystal oscillator. The converter’s linearity is inherently robust, and its self-calibration engine ensures endpoint accuracy by adjusting zero and full-scale references on demand. This calibration can also be extended to compensate for system-level offset and gain errors.

Data access is handled through a flexible serial interface supporting asynchronous UART-compatible mode and two synchronous modes for seamless integration with shift registers or standard microcontroller serial ports.

Introduced in the early 1990s, Analog Devices’ AD7701 helped pioneer low-power, high-resolution sigma-delta conversion for instrumentation and industrial sensing. While newer ADCs have since expanded on their capabilities, AD7701 remains in production and continues to serve in legacy systems and precision applications where its simplicity and reliability still resonate.

The following figure illustrates the functional block diagram of this enduring 16-bit sigma-delta ADC.

Figure 1 Functional block diagram of AD7701 showcases its key architectural elements. Source: Analog Devices Inc.

Delta-sigma ADCs and DACs

Delta-sigma converters—both analog-to-digital converters (ADCs) and digital-to-analog converters (DACs)—leverage oversampling and noise shaping to achieve high-resolution signal conversion with relatively simple analog circuitry.

In a delta-sigma ADC, the input signal is sampled at a much higher rate than the Nyquist frequency and passed through a modulator that emphasizes quantization noise at higher frequencies. A digital filter then removes this noise and decimates the signal to the desired resolution.

Conversely, delta-sigma DACs take high-resolution digital data, shape the noise spectrum, and output a high-rate bitstream that is smoothed by an analog low-pass filter. This architecture excels in audio and precision measurement applications due to its ability to deliver robust linearity and dynamic range with minimal analog complexity.

Note that from here onward, the focus is exclusively on delta-sigma ADCs. While DACs share similar architectural elements, their operational context and signal flow differ significantly. To maintain clarity and relevance, DACs are omitted from this discussion—perhaps a topic for a future segment.

Inside the delta-sigma ADC

A delta-sigma ADC typically consists of two core elements: a delta-sigma modulator, which generates a high-speed bitstream, and a low-pass filter that extracts the usable signal. The modulator outputs a one-bit serial stream at a rate far exceeding the converter’s data rate.

To recover the average signal level encoded in this stream, a low-pass filter is essential; it suppresses high-frequency quantization noise and reveals the underlying low-frequency content. At the heart of every delta-sigma ADC lies the modulator itself; its output bitstream represents input signal’s amplitude through its average value.

A block diagram of a simple analog first-order delta-sigma modulator is shown below.

Figure 2 The block diagram of a simple analog first-order delta-sigma modulator illustrates its core components. Source: Author

This modulator operates through a negative feedback loop composed of an integrator, a comparator, and a 1-bit DAC. The integrator accumulates the difference between the input signal and the DAC’s output. The comparator then evaluates this integrated signal against a reference voltage, producing a 1-bit data stream. This stream is fed back through DAC, closing the loop and enabling continuous refinement of the output.

Following the delta-sigma modulator, the 1-bit data stream undergoes decimation via a digital filter (decimation filter). This process involves data averaging and sample rate reduction, yielding a multi-bit digital output. Decimation concentrates the signal’s relevant information into a narrower bandwidth, enhancing resolution while suppressing quantization noise within the band of interest.

It’s no secret to most engineers that second-order delta-sigma ADCs push noise shaping further by using two integrators in the modulator loop. This deeper shaping shifts quantization noise farther into high frequencies, improving in-band resolution at a given oversampling ratio.

While the design adds complexity, it enhances signal fidelity and eases post-filtering demands. Second-order modulators are common in precision applications like audio and instrumentation, though stability and loop tuning become more critical as order increases.

Well, at its core, the delta-sigma ADC represents a seamless integration of analog and digital processing. Its ability to achieve high-resolution conversion stems from the coordinated use of oversampling, noise shaping, and decimation—striking a delicate balance between speed and precision.

Delta-sigma ADCs made approachable

Although delta-sigma conversion is a complex process, several prewired ADC modules—built around popular, low-cost ICs like the HX711, ADS1232/34, and CS1237/38—make experimentation remarkably accessible. These chips offer high-resolution conversion with minimal external components, ideal for precision sensing and weighing applications.

Figure 3 A few widely used modules simplify delta-sigma ADC practice, even for those just starting out. Source: Author

Delta-sigma vs. flash ADCs vs. SAR

Most of you already know this, but flash ADCs are the speed demons of the converter world—using parallel comparators to achieve ultra-fast conversion, typically at the expense of resolution.

Flash ADCs and delta-sigma architectures serve distinct roles, with conversion rates differing by up to two orders of magnitude. Delta-sigma ADCs are ideal for low-bandwidth applications—typically below 1 MHz—where high resolution (12 to 24 bits) is required. Their oversampling approach trades speed for precision, followed by filtering to suppress quantization noise. This also simplifies anti-aliasing requirements.

While delta-sigma ADCs excel in resolution, they are less efficient for multichannel systems. Architecture may use sampled-data modulators or continuous-time filters. The latter shows promise for higher conversion rates—potentially reaching hundreds of Msps—but with lower resolution (6 to 8 bits). Still in early R&D, continuous-time delta-sigma designs may challenge flash ADCs in mid-speed applications.

Interestingly, flash ADCs can also serve as internal building blocks within delta-sigma circuits to boost conversion rates.

Also, successive approximation register (SAR) ADCs sit comfortably between flash and delta-sigma designs, offering a practical blend of speed, resolution, and efficiency. Unlike flash ADCs, which prioritize raw speed using parallel comparators, SAR converters use a binary search approach that is slower but far more power-efficient.

Compared to delta-sigma ADCs, SAR designs avoid oversampling and complex filtering, making them ideal for moderate-resolution, real-time applications. Each architecture has its sweet spot: flash for ultra-fast, low-resolution tasks; delta-sigma for high-precision, low-bandwidth needs; and SAR for balanced performance across a wide range of embedded systems.

Delta-sigma converters elegantly bridge the analog and digital worlds, offering high-resolution performance through clever noise shaping and oversampling. Whether you are designing precision instrumentation or exploring audio fidelity, understanding their principles unlocks a deeper appreciation for modern signal processing.

Curious how these concepts translate into real-world design choices? Join the conversation—share your favorite delta-sigma use case or challenge in the comments. Let us map the noise floor together and surface the insights that matter.

T.K. Hareendran is a self-taught electronics enthusiast with a strong passion for innovative circuit design and hands-on technology. He develops both experimental and practical electronic projects, documenting and sharing his work to support fellow tinkerers and learners. Beyond the workbench, he dedicates time to technical writing and hardware evaluations to contribute meaningfully to the maker community.

T.K. Hareendran is a self-taught electronics enthusiast with a strong passion for innovative circuit design and hands-on technology. He develops both experimental and practical electronic projects, documenting and sharing his work to support fellow tinkerers and learners. Beyond the workbench, he dedicates time to technical writing and hardware evaluations to contribute meaningfully to the maker community.

Related Content

- Delta-sigma ADCs in a nutshell

- Delta-sigma ADC basics: How the digital filter works

- Recent Developments for SAR and Sigma Delta ADCs

- Understanding sigma delta ADCs: A non-mathematical approach

- 24-Bit, 16-Channel Delta-Sigma ADC Simplifies Front-End Signal Conditioning

The post Delta-sigma demystified: Basics behind high-precision conversion appeared first on EDN.

What you see here was way ahead of its time

| Late 90s before Ethernet control was anywhere near affordable and circuit control over the Internet was sci-fi dreams here was a $20 external HP JetDirect print sever controlling 8 GPIOs with Opto22 SSRs and a little fool logic to make the print sever think its connected to a real printer lol the NAND gate fooled the JetDirect that every time a byte was "sent to the printer" the printer flapped strobe as if it has printed the bye :) Data was piped via good old Linux NetCat - wait using Linux in the 90s...oh I'm getting emotional already I’ve so forgotten those days of badass innovation - now smart plugs are everywhere … [link] [comments] |

This looks like a very interesting Xbox controller I found

| Sorry for light getting in the way of appreciating the full beauty of this PCB :)) [link] [comments] |

Weekly discussion, complaint, and rant thread

Open to anything, including discussions, complaints, and rants.

Sub rules do not apply, so don't bother reporting incivility, off-topic, or spam.

Reddit-wide rules do apply.

To see the newest posts, sort the comments by "new" (instead of "best" or "top").

[link] [comments]

Old Apple IIgs Monitor LED module.

| Wish I had a spec sheet on this part. This was pulled from an Apple IIgs monitor. I don't think it's a true led. Works lovely on 5v [link] [comments] |

The SN76477 Demo Circuit

The SN76477 "Demo Circuit":

This is a 1977 Complex Sound Generator chip from Texas Instruments. Like a lot of nerds, I got one from Radio Shack, put it in an experimenter's plugboard and got various airplane, gunshot and "ray gun" noises out of it.

In the datasheet, there was one more schematic that sat in the back of my brain for these decades; the "Demo circuit".

Over time, you learn that a schematic is a fraction of what you need to build a circuit. The chip is the biggest thing in the drawing and if you're young, you think that if you've got this IC, your nearly at home plate. This schematic (there are several iterations from the past fifty-odd years) has many rotary switches, potentiometers, capacitors and resistors. There's a 7805 regulator and two jacks, but a lot is missing; there are "R-xx" numbers for the resistors and pots, but no "C-xx" numbers for the caps. J1 and J2 are unlabeled; most of the controls are unlabeled. This being a sound project, I think it's a big deal that none of the pots are noted as being linear or audio taper. On some of the drawings, two capacitors on SW7 are swapped; it would work but it'd feel flaky as you turned the switch and listened to the result

My question a couple of months ago was, "Has anybody actually built this thing?"

It appears that the answer is "No".

I spent some time with Digi-Key's web site, Excel for pricing and Visio to lay out knobs, switches and labels.

I didn't count buying two of each potentiometer, one audio taper and one linear.

I didn't count cabinet parts; the Visio work was to find the size of the front panel. The layout isn't anything like how a real build would be done; the jacks are together, the toggle switches are together, etc.

I also have never seen a 9/16" punch that leaves a tab to keep the switch from spinning in it's hole; I know they existed but I think someone cast them into the sun before the Internet got invented.

So parts would be something over $250.00 without a cabinet; the panel would be about 18" square. A 19" wide rack panel, 10U tall would do it, and you'd want it in a console of some kind, which seems expensive to think about unless you made it out of wood, and it's still designed to be powered by a 9-volt battery; the entire project feels like a collision between the cheap and the expensive.

A quick search of Reddit and/or YouTube finds a box made with less knobs and no labelling, making sounds that scream "1977 science fiction", and not Star Wars. More like that show where Jim Nabors and Ruby Buzzi played two robots.

Letting go of the Demo Circuit, another drawing in the datasheet is a block diagram of the circuit. Most of the building blocks were in big Moog and other synthesizers in the late 1960's through late 1980's; tiny parts of Keith Emerson's rig or the stuff a guy called "Tomita" used. I don't have the space or musical talent for such a thing, but I wondered about emulators, then of course Free emulators.

I ended up at https://vcvrack.com/ , download the free version, and in less than 30 minutes had an emulated SN76477 running on my computer.

I could've probably added a MIDI tracker and had it play music. If you have a MIDI keyboard, you might be able to try the "organ" project in the datasheets.

If you had budget, time, determination, space and both electronic and musical talent, you could build the Demo Circuit, and you'd probably want to somehow interface it with a keyboard. I could see somebody like David Guetta or Deadmau5 have this on one far side of the stage and do something silly as a break between the regular show, but I don't think that it could make such awesome sounds that the great orchestras would retire in shame.

That's what I figured out about the SN76477 this fall.

Regards, Mark Stout

[link] [comments]

Making this for my esp32 p4 FBDCDC and ENDCDC pins, hope it's helpful

| submitted by /u/PepeIsLife69_ [link] [comments] |

SemiLEDs full-year revenue grows eight-fold, despite last-quarter drop

4 bit full Adder

| I've assembled this 4 bit full adder with logic ics. [link] [comments] |

Infineon’s CoolGaN technology used in Anker’s new-generation 160W prime charger

A seldom-seen component: a snubber is a resistor and a capacitor in series. Placed across a switch or relay contact to suppress the arc (AC or DC).

| submitted by /u/Electro-nut [link] [comments] |

Power Tips #147: Achieving discrete active cell balancing using a bidirectional flyback

Efficient battery management becomes increasingly important as demand for portable power continues to rise, especially since balanced cells help ensure safety, high performance, and a longer battery life. When cells are mismatched, the battery pack’s total capacity decreases, leading to the overcharging of some cells and undercharging of others—conditions that accelerate degradation and reduce overall efficiency. The challenge is how to maintain an equal voltage and charge among the individual cells.

Typically, it’s possible to achieve cell balancing through either passive or active methods. Passive balancing, the more common approach because of its simplicity and low cost, equalizes cell voltages by dissipating excess energy from higher-voltage cells through a resistor or FET networks. While effective, this process wastes energy as heat.

In contrast, active cell balancing redistributes excess energy from higher-voltage cells to lower-voltage ones, improving efficiency and extending battery life. Implementing active cell balancing involves an isolated, bidirectional power converter capable of both charging and discharging individual cells.

This Power Tip presents an active cell-balancing design based on a bidirectional flyback topology and outlines the control circuitry required to achieve a reliable, high-performance solution.

System architectureIn a modular battery system, each module contains multiple cells and a corresponding bidirectional converter (the left side of Figure 1). This arrangement enables any cell within Module 1 to charge or discharge any cell in another module, and vice versa. Each cell connects to an array of switches and control circuits that regulate individual charge and discharge cycles.

Figure 1 A modular battery system block diagram with multiple cells a bidirectional converter where any cell within Module 1 can charge/discharge any cell in another module. Each cell connects to an array of switches and control circuits that regulate individual charge/discharge cycles. Source: Texas Instruments

Figure 1 A modular battery system block diagram with multiple cells a bidirectional converter where any cell within Module 1 can charge/discharge any cell in another module. Each cell connects to an array of switches and control circuits that regulate individual charge/discharge cycles. Source: Texas Instruments

The block diagram in Figure 2 illustrates the design of a bidirectional flyback converter for active cell balancing. One side of the converter connects to the bus voltage (18 V to 36 V), which could be the top of the battery cell stack, while the other side connects to a single battery cell (3.0 V to 4.2 V). Both the primary and secondary sides employ flyback controllers, allowing the circuit to operate bidirectionally, charging or discharging the cell as required.

Figure 2 A bidirectional flyback for active cell balancing reference design. Source: Texas Instruments

A single control signal defines the power-flow direction, ensuring that both flyback integrated circuits (ICs) never operate simultaneously. The design delivers up to 5 A of charge or discharge current, protecting the cell while maintaining efficiency above 80% in both directions (Figure 3).

Figure 3 Efficiency data for charging (left) and discharging (right). Source: Texas Instruments

Charge mode (power from Vbus to Vcell)In charge mode, the control signal enables the charge controller, allowing Q1 to act as the primary FET. D1 is unused. On the secondary side, the discharge controller is disabled, and Q2 is unused. D2 serves as the output diode providing power to the cell. The secondary side implements constant-current and constant-voltage loops to charge the cell at 5 A until reaching the programmed voltage (3.0 V to 4.2 V) while keeping the discharge controller disabled.

Discharge mode (power from Vcell to Vbus)Just the opposite happens in discharge mode; the control signal enables the discharge controller and disables the charge controller. Q2 is now the primary FET, and D2 is inactive. D1 serves as the output diode while Q1 is unused. The cell side enforces an input current limit to prevent discharge of the cell above 5 A. The Vbus side features a constant-voltage loop to ensure that the Vbus remains within its setpoint.

Auxiliary power and bias circuitsThe design also integrates two auxiliary DC/DC converters to maintain control functionality under all operating conditions. On the bus side, a buck regulator generates 10 V to bias the flyback IC and the discrete control logic that determines the charge and discharge direction. On the cell side, a boost regulator steps the cell voltage up to 10 V to power its controller and ensure that the control circuit is operational even at low cell voltages.

Multimodule operationFigure 4 illustrates how multiple battery modules interconnect through the reference design’s units. The architecture allows an overcharged cell from a higher-voltage module, shown at the top of the figure, to transfer energy to an undercharged cell in any other module. The modules do not need to be connected adjacently. Energy can flow between any combination of cells across the pack.

Figure 4 Interconnection of battery modules using TI’s reference design for bidirectional balancing. Source: Texas Instruments

Future improvementsFor higher-power systems (20 W to 100 W), adopting synchronous rectification on the secondary and an active-clamp circuit on the primary will reduce losses and improve efficiency, thus enhancing performance.

For systems exceeding 100 W, consider alternative topologies such as forward or inductor-inductor-capacitor (LLC) converters. Regardless of topology, you must ensure stability across the wide-input and cell-voltage ranges characteristic of large battery systems.

Modern multicell battery systems.The bidirectional flyback-based active cell balancing approach offers a compact, efficient, and scalable solution for modern multicell battery systems. By recycling energy between cells rather than dissipating this energy as heat, the design improves both energy efficiency and battery longevity. Through careful control-loop optimization and modular scalability, this architecture enables high-performance balancing in portable, automotive, and renewable energy applications.

Sarmad Abedin is currently a systems engineer with Texas Instruments, working in the power design services (PDS) team, working on both automotive and industrial power supplies. He has been designing power supplies for the past 14 years and has experience in both isolated and non-isolated power supply topologies. He graduated from Rochester Institute of Technology in 2011 with his bachelor’s degree.

Sarmad Abedin is currently a systems engineer with Texas Instruments, working in the power design services (PDS) team, working on both automotive and industrial power supplies. He has been designing power supplies for the past 14 years and has experience in both isolated and non-isolated power supply topologies. He graduated from Rochester Institute of Technology in 2011 with his bachelor’s degree.

Related Content

- Active balancing: How it works and what are its advantages

- Achieving cell balancing for lithium-ion batteries

- Lithium cell balancing: When is enough, enough?

- Product How-To: Active balancing solutions for series-connected batteries

The post Power Tips #147: Achieving discrete active cell balancing using a bidirectional flyback appeared first on EDN.

ECMS applications make history, cross Rs. 1 lakh crore in investment applications

Union Minister for Electronics and IT Ashwini Vaishnaw announced that the government has received investment applications worth nearly 1 lakh 15 thousand, 351 crore rupees under the Electronics Component Manufacturing Scheme (ECMS) against the targeted 59 thousand 350 crore rupees. The union minister made the announcement during a media briefing in New Delhi after the last date for applications was closed on November 27, 2025. He credited the 11 years of trust in the system which is now expected to drive investment, employment generation, and production.

Additionally, he added that, against a production target of 4 lakh 56 thousand and 500 crore rupees, production estimates of over 10 lakh crore rupees have been received.

The post ECMS applications make history, cross Rs. 1 lakh crore in investment applications appeared first on ELE Times.

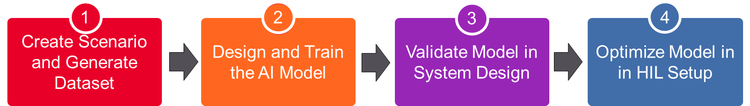

AI-Driven 6G: Smarter Design, Faster Validation

Courtesy: Keysight Technologies

| Key takeaways: Telecom companies are hoping for quick 6G standardization followed by a rapid increase in 6G enterprise and retail customers, with AI being a key enabler:

● Artificial intelligence (AI) and machine learning (ML) are expected to become essential and critical components of the 6G standards, scheduled for release in 2028 or 2029. ● Engineers in 6G and AI could take products to market quickly by understanding the potential benefits of AI / ML for 6G design validation. |

The 6G era is poised to be fundamentally different, it may potentially be the first “AI-native” iteration of wireless telecom networks. With extensive use of AI expected in 6G, engineers face an unprecedented challenge: How do you validate a system that is more dynamic, intelligent, and faster than anything before it?

This blog gives insights into 6G design validation using AI for engineers working in communication service providers, mobile network operators, communication technology vendors, and device manufacturers.

We explain the new applications that 6G and AI could unlock, the AI techniques you’re likely to run into, and how you could use them for designing and testing 6G networks.

What are the key use cases that 6G and AI will enable together?

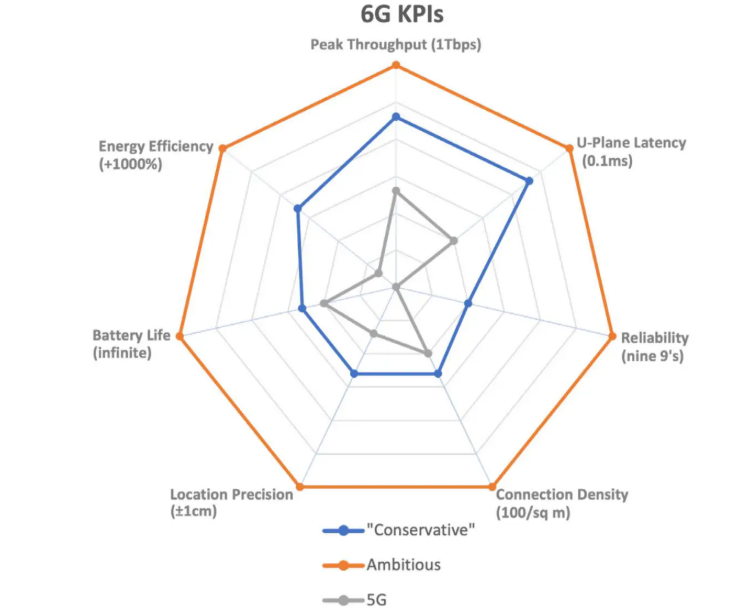

Figure 1. 6G conservative and ambitious goals versus 5G goals (Image source: How to Revolutionize 6G Research With AI-Driven Design)

The two engines of 6G and AI are projected to power exciting new use cases like real-time digital twins, smart factories, highly autonomous mobility, holographic communication, and pervasive edge intelligence.

These are among the major innovations that the International Telecommunication Union (ITU) and the Third Generation Partnership Project (3GPP) envision from 6G and AI. Let’s examine these key use cases for AI in 6G and 6G for AI in 2030 and beyond.

Real-time digital twins using 6G and AI

With promises of ubiquitous deployment, high data rates, and ultra-low latency, 6G and AI could create precise real-time representations of the physical world as digital twins.

Digital twins will be powerful tools for modeling, monitoring, managing, analyzing, and simulating all kinds of physical assets, resources, environments, and situations in real time.

Digital twin networks could serve as replicas of physical networks, enabling real-time optimization and control of 6G wireless communication networks. Proposed 6G capabilities like integrated sensing and communication (ISAC) could efficiently synchronize these digital and physical worlds.

Smart factories through 6G and AI

6G and AI have the potential to support advanced industrial applications (“industrial 6G”) through reliable low-latency connections for ubiquitous real-time data collecting, sharing, and decision-making. They could enable full automation, control, and operation, leveraging connectivity to intelligent devices, industrial Internet of Things (IoT), and robots. Private 6G networks may effectively streamline operations at airports and seaports.

Autonomous mobility via 6G and AI

6G and AI are set to enhance autonomous mobility, including self-driving vehicles and autonomous transport based on cellular vehicle-to-everything (C-V2X) technologies. This involves AI-assisted automated driving, real-time 3D-mapping, and high-precision positioning.

Holographic communication over 6G

6G and AI data centers could enable immersive multimedia experiences, like holographic telepresence and remote multi-sensory interactions. Semantic communication, where AI will try to understand users’ actual current needs and adapt to them, could help meet the demands of data-hungry applications like holographic communication and extended reality, transmitting only the essential semantics of messages.

Pervasive edge AI over 6G technologies

The convergence of communication and computing, particularly through edge computing and edge intelligence, is likely to distribute AI capabilities throughout the 6G network, close to the data source. This has the potential to enable real-time distributed learning, joint inference, and collaboration between intelligent robots and devices, leading to ubiquitous intelligence.

How will AI optimize 6G network design and operation?

In this section, we look more specifically at how AI is being considered for the design and testing of 6G networks.

At a high level, 6G communications will likely involve:

- physical components, like the base stations, PHY transceivers, network switches, and user equipment (UE, like smartphones or fixed wireless modems)

- logical subsystems, like the radio access network (RAN), core network, network functions, and protocol stacks

Some of these are expected to be designed, optimized, and tested using design-time AI models before deployment. Others are expected to use runtime AI models during their operations to dynamically adapt to local traffic, geographical, and weather conditions.

Let’s look at which aspects of 6G radio and network functions are likely to be enhanced by the integration of AI techniques in their designs.

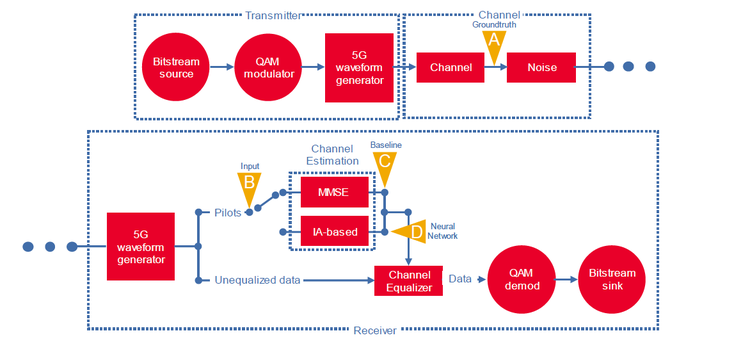

AI-native air interface

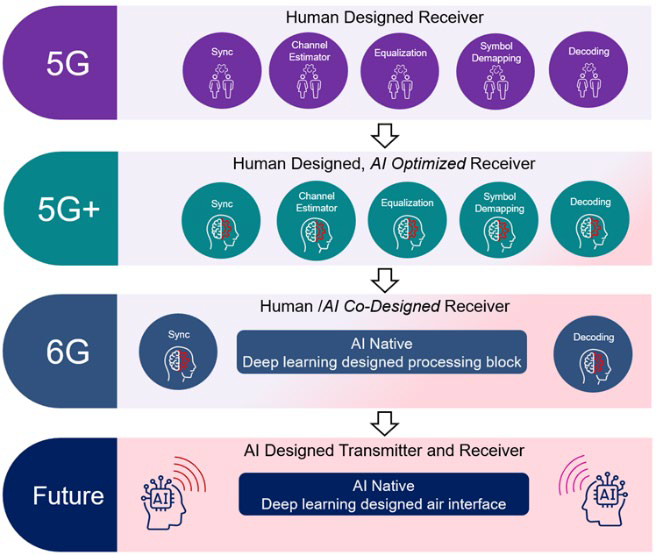

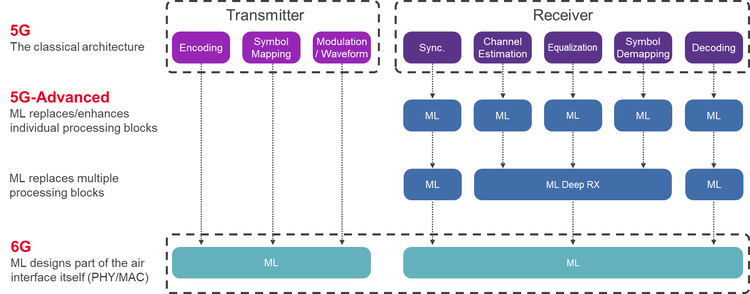

Figure 2. How AI may change the air interface design (Image source: The Integration of AI and 6G)

In the UE-to-RAN air interface, AI models could enhance core radio functions like symbol detection, channel estimation, channel state information (CSI) estimation, beam selection, modulation, and antenna selection.

Figure 3. The three key phases toward a 6G AI-Native Air interface (Image source: The Integration of AI and 6G)

Some of these AI models may run on the UEs, some on the base stations, and some on both.

AI-assisted beamforming

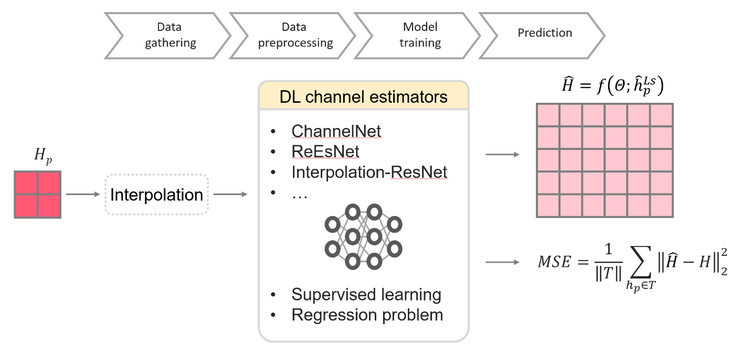

Figure 4. Channel estimation with supervised learning (Image source: How to Revolutionize 6G Research With AI-Driven Design)

AI is envisioned to:

- assist in ultra-massive multiple-input multiple-output (UM-MIMO) using more precise CSI

- predict optimal transmit beams

- reduce beam-pairing complexity

- assist reconfigurable intelligent surfaces (RIS) for environmental optimization

It’s hoped that AI will become instrumental in end-to-end network optimization and dynamically adapting the entire RAN through self-monitoring, self-organization, self-optimization, and self-healing.

Automated network managementAI holds the potential to automate network operation and maintenance as well as enable automated management services like predictive maintenance, intelligent data perception, on-demand capability addition, traffic prediction, and energy management.

Real-time dynamic allocation and scheduling of wireless resources like bandwidth and power for load balancing could be automatically handled by AI. AI-based mobility management could proactively manage handoffs and reduce signaling overhead.

Additionally, analysis of vast network data by AI promises precise threat intelligence, real-time monitoring, prediction, and active defense against network faults and security risks.

What AI techniques are most effective for validating 6G system-level performance?

Figure 5. 6G AI-based model validation (Image source: The Integration of AI and 6G)

AI is a wide field with many techniques, like deep learning, reinforcement learning, generative models, and machine learning. Let’s look at how these different AI algorithms and architectures could be used for 6G design, validation, and network performance testing.

Reinforcement learning (RL)

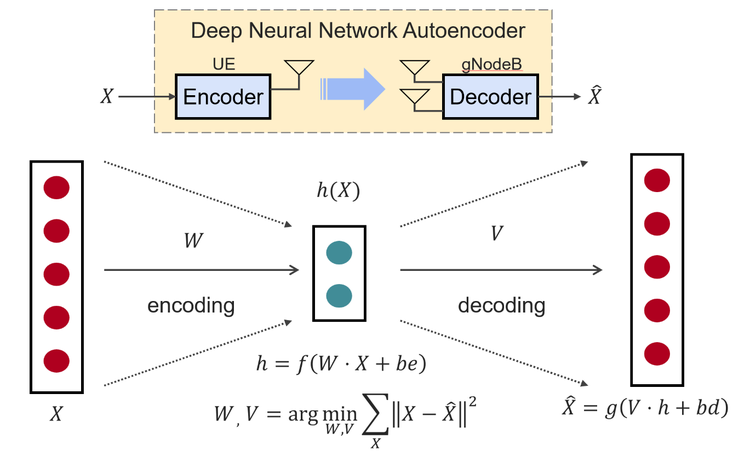

Figure 6. CSI feedback compression (Image source: How to Revolutionize 6G Research With AI-Driven Design)

RL has the potential to be at the forefront of AI for 6G self-optimization, network design, and testing because it is good at replicating human decision-making, testing on a massive scale, and enabling the recent rise of large reasoning models.

RL and deep RL could be used for the following use cases:

- RAN optimization: RL is already being used for intent-based RAN optimization in 5G, enabling autonomous decision-making in dynamic network environments, particularly for mobility management, interference mitigation, and energy-efficient scheduling. RL can control and optimize complex workflows.

- Enhanced beamforming: Deep RL could be used for beam prediction in the spatial and temporal domains.

- Functional testing: Autonomous agents, trained using RL, could test 6G hardware and software systems, looking for bugs as their rewards. Each agent will be a deep neural network trained using proximal policy optimization or direct preference optimization to do sequences of network actions and favor those sequences that are likely to maximize their rewards (the number of bugs found).

- Performance testing: In a 6G system, performance will be an emergent property of hundreds of interacting network parameters. Manually finding the combinations that lead to poor performance will be nearly impossible. An RL agent could automatically explore these combinations and identify configurations that result in performance bottlenecks.

DNNs could be used for the following:

- Channel estimation: DNNs and other deep learning architectures like Convolutional Neural Networks (CNNs) could estimate channel conditions, which will be crucial for overall system performance, especially in complex, high-noise environments.

- CSI compression: CNN-based autoencoders are poised to become the most commonly used architecture for CSI compression.

Transformer-based autoencoders (like Transnet) have been tested for compressing CSI feedback from UEs to a 5G base station and could be used for 6G too.

Graph neural networks (GNNs)GNNs are used to model the relational structure of network elements. They could learn spatial and topological patterns for tasks like mobility management, interference mitigation, and resource allocation.

They may also be used as physics-informed models for channel estimation reconstruction.

Generative adversarial networks (GANs)GANs will probably be used to learn and create realistic wireless channel data. They could also be used for denoising and anomaly detection.

Large reasoning and action modelsThese models are created from pre-trained large language models or large concept models by using RL to fine-tune them for reasoning and acting. They are the foundations of agentic AI. Agentic AI for 6G is still a very new research topic. Agentic AI’s ability for complex orchestration of smaller AI models, hardware, databases, and tools could make it suitable for testing 6G networks.

How is synthetic data generated by AI used in 6G testing and validation?

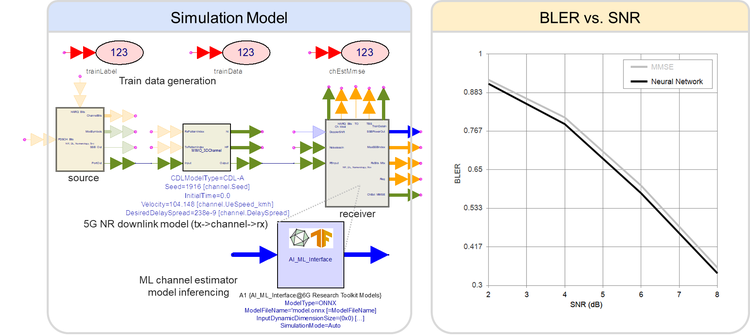

Figure 7. Using AI models in System Design (Image source: The Integration of AI and 6G)

A key benefit of AI will be its ability to synthesize test scenarios and data that simulates realistic 6G environments in lockstep with the 6G standards as they emerge and evolve in the coming years. Such synthesis could enhance designs and reduce development risks from day one.

The use of AI in network operations will lead to non-determinism and an explosion of possible outcomes that challenge testability and repeatability.

Design and test engineers will have to worry about how they can test all possible scenarios and edge cases. Physical deployments would not be possible until customer trials start. Even physical prototypes will be initially impossible and become expensive later on.

This is why AI-powered simulations and AI-generated realistic data are projected to become critical for 6G companies. AI could generate any type of large, realistic data needed to train and test the sophisticated AI/ML algorithms of 6G. The key technologies and techniques involved are outlined below:

- Digital twins: A digital twin is an accurate and detailed proxy for a real-world implementation, capable of emulating entire networks and individual components. These virtual representations will be key to simulating ultra-dense 6G environments. They could support integrated modeling of network environments and users to test complex RAN optimization problems.

- Generative AI models: GANs could become crucial for testing 6G wireless channels. A GAN could be trained on data from real-world 5G networks augmented with 6G-specific parameters calculated using known analytical models. The generator network would learn to synthesize realistic 6G data and simulate virtual channels for realistic environments, even accounting for geography. Later, measured data from 6G hardware prototypes could be included to enhance their realism.

- Specialized testbeds: Synthetic data is vital for studying new 6G sub-terahertz bands (100-300 GHz) because physical measurements are not practical. AI-generated scenarios based on data from sub-terahertz testbeds could recreate the complex impairments and nonlinearities expected at these frequencies.

- Simulation tools: Sophisticated visual tools like Keysight Channel Studio (RaySim) could simulate signal propagation and generate channel data in a specific environment, like a selected city area. It could model detailed characteristics like delay spread and user mobility, mimicking real-world conditions needed for training components like 6G neural receivers.

- Systems modeling platforms: An end-to-end system design platform like Keysight’s System Design will have the ability to generate high-quality 6G data for neural network training. It would combine system design budgets, 3GPP-compliant channel models (like clustered delay line models), measured data, and noise to produce diverse samples with varying noise and channel configurations.

Figure 8. Wireless channel estimation (Image source: The Integration of AI and 6G)

AI techniques like anomaly detection and intelligent test automation could help you design and validate all the advanced chips and components that will go into 6G hardware for capabilities like sub-terahertz (THz)frequency bands and UM-MIMO.

Below, we speculate on how 6G and AI could be used for chip and hardware design.

Data-driven AI modelingThe behaviors of 6G technology enablers like UM-MIMO, reconfigurable intelligent surfaces, and sub-terahertz frequency bands will be too complex to fully characterize using analytical methods. Instead, neural networks could create accurate, data-driven, nonlinear AI models.

AI models in electronic design automation (EDA)EDA tools like Advanced Design System and Device Modeling could seamlessly integrate AI models for designing the high-frequency gallium nitride (GaN) radio frequency integrated circuits that’ll probably be needed in 6G. These tools could run artificial neural network models as part of circuit simulations and device modeling.

Validation of AI-enabled components

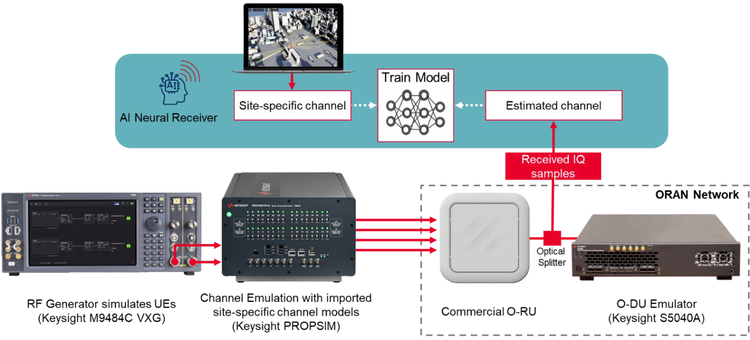

Figure 9. 6G AI neural receiver design and validation setup (Image source: The Integration of AI and 6G)

Validating the AI-native physical layer blocks (like neural receivers) will be paramount. Only AI-driven testing and automation could effectively tackle the black box nature and non-determinism of AI models.

AI-driven simulationsAI-driven simulation tools like Keysight RaySim could synthesize high-quality, site-specific channel data that — combined with deterministic, stochastic, and measured data — to create highly realistic environments for validating THz and MIMO designs.

Optimized beamforming and CSIAI models could potentially enhance beamforming by improving spectral efficiency. A problem with many antennas is the huge CSI feedback overhead. AI models like autoencoders could compress CSI feedback by as much as 25% without degrading efficiency and reliability.

Hardware-in-the-loop validationAI channel estimation models have the potential to handle multidimensionality and noise levels more robustly than traditional methods. They could be used by system design software and tested in hardware-in-the-loop setups (with channel emulators, signal generators, and digitizers) to assess effectiveness based on metrics like block error rate and signal-to-noise ratio.

Anomaly detectionAnomaly detection could be applied to data generated by AI simulations and models to identify unusual behaviors or deviations that may point to design flaws or operational issues.

What are the challenges and limitations of using AI in 6G design validation?Could AI and its results be trusted? Without careful design, every AI model is prone to out-of-distribution errors, data scarcity, poor model interpretability, overfitting, and hallucinations. A better question that your 6G and AI engineers must keep asking is, “How can we make our AI models, as well as AI-generated tests and data, more accurate and more trustworthy?”

For that, follow the recommendations below.

- Design for seamless integration: AI-based solutions must seamlessly integrate and agree with existing wireless principles built upon decades of tried-and-tested signal processing and communication theories. For example, a fully AI-designed physical layer that can dynamically change the waveform based on ambient conditions poses challenges for traditional measurement and design techniques like digital predistortion and amplifier design.

- Address data scarcity upfront: Real-world wireless data is often sparse. 6G ecosystems will probably be particularly challenging to characterize. Address this by augmenting data from 5G-Advanced networks with data calculated by 6G-specific analytical models. However, plan for extensive manual pre-processing because preparing realistic channel data to train models will not be trivial.

- Aim for model interpretability: To balance the opacity of powerful black-box techniques like deep neural networks, combine them with models that are more interpretable — like decision trees and random forests — through approaches like mixture-of-experts, ensembling, and explainable AI.

- Use physics-informed models: By bounding AI results with data from physics-informed models, engineers will be able to ensure that AI models operate within physical reality, making them robust and trustworthy. For example, reinforcement learning, which could be used for intent-based RAN optimization, can produce different results for the same input, generate out-of-bounds parameters, or fail to constrain to physical reality.

- Prevent overfitting: Sparse data and poor data diversity can lead to overfitting. For example, data generated under severe fading channel conditions is known to result in overfitting. Follow data augmentation and cross-validation best practices to counteract overfitting.

- Plan hardware-in-the-loop testing: Synthetically generated channels can be loaded into channel emulators like PROPSIM to test AI/ML algorithms in base stations and UEs. This will enable model advancements based on real failures and impairments.

- Avoid negative side effects: AI integration should not lead to excessive energy usage, unmanageable training data, or security risks. AI will greatly expand the threat surface, but since AI itself is quite new, cybersecurity risks are not well understood. This means 6G and AI integrations must be carefully designed for resilience and quick recovery from cyber attacks.

The post AI-Driven 6G: Smarter Design, Faster Validation appeared first on ELE Times.

Scaling up the Smart Manufacturing Mountain

Courtesy: Rockwell Automation

| A step-by-step roadmap to adopting smart manufacturing tools, boosting efficiency, and unifying systems for a smoother digital transformation journey. |

Embracing new technology in manufacturing is similar to ascending a mountain since it requires strategy, pacing, and the right gear. Rushing ahead without proper support can strain your systems as well as your people, but with thoughtful planning and timely technology selection, the climb becomes manageable and rewarding.

There are many paths to digital excellence. Integrating new technologies can significantly boost productivity and efficiency, but even the smoothest rollouts can come with hurdles. In our decades of experience working with customers, we’ve learned the importance of taking a measured approach to change to avoid unnecessary disruption. Here, we’ll lay out one way to approach digital transformation.

Beginning the Climb: Laying the Foundation

For many manufacturers, an accessible starting point for digital transformation is real-time production monitoring. Production monitoring enhances visibility and empowers your team to manage performance proactively—without overhauling existing workflows.

By consolidating machine and system data into a single dashboard, production monitoring eliminates silos and simplifies decision-making. It equips your team with actionable KPIs and insights from the shop floor to the executive suite.

With minimal investment in time, budget, and effort, real-time monitoring can deliver immediate value—which makes it an ideal first step on your digital journey.

Climbing Higher: Expanding Capabilities

While production monitoring is a strong foundation, it’s just the beginning. To unlock deeper efficiencies, manufacturers can next implement systems that offer broader control and insight across operations.

A modern manufacturing execution system (MES) is a prime example. By automating routine tasks, a MES reduces errors, cuts costs, and improves profitability. It also provides end-to-end visibility, communication, and traceability throughout the production lifecycle.

Pairing MES with a robust enterprise resource planning (ERP) system further enhances operational oversight. ERP tools help streamline compliance, manage risk, and align financial, operational, and IT strategies under one umbrella.

The real power lies in integrating these systems. When MES, ERP, and other tools work together in harmony, manufacturers can experience transformative results.

Reaching the Peak: Unlocking Full Potential

Even with a unified platform, there’s still room to elevate your operations. Today’s smart tools don’t just optimize—they redefine what’s possible.

Plex MES Automation and Orchestration leverages cutting-edge technology to connect machines and deliver unprecedented transparency and control. With intuitive low-code integration, your team can customize workflows and achieve seamless automation across the plant floor.

Gear Up for Your Digital Climb

According to our 10th Annual State of Smart Manufacturing report, many manufacturers feel they’re falling behind technologically compared to last year. If you’re exploring new solutions but unsure about the path forward, you’re not alone.

Whether you’re just beginning your smart manufacturing journey or seeking advanced, integrated solutions, we’d like to help! Check out our case study library to see how we’ve helped companies just like yours take on projects to advance their digital transformation journey.

The post Scaling up the Smart Manufacturing Mountain appeared first on ELE Times.

Singapore’s largest industrial district cooling system, Now operational at ST’s AMK TechnoPark

The District Cooling System at ST’s Ang Mo Kio (AMK) TechnoPark is operational and on time. Ms. Low Yen Ling, Senior Minister of State, Ministry of Trade and Industry & Ministry of Culture, Community and Youth, who joined ST in announcing this project in 2022, now took part in the inauguration ceremony. This launch is a critical milestone in ST’s goal to achieve carbon neutrality by 2027, and to work with local partners while also serving the communities as we move toward this sustainability objective.

Why a District Cooling System? Composition of a District Cooling System ST’s Ang Mo Kio TechnoPark in Singapore

ST’s Ang Mo Kio TechnoPark in Singapore

In a DCS, one plant cools water before sending it to a network of underground pipes that serve various buildings. The system thus pools resources to increase efficiency, reduce environmental impacts, and save space. Buildings no longer need chillers, saving power and maintenance costs thanks to the central plant. Moreover, a loop sends the water back to the plant to cool it again. The main plant also stores water. Cooling therefore can happen during off-peak periods to improve the efficiency.

According to the Encyclopedia of Energy, the first significant DCS project dates back to 1962 and was installed in the United States. The technology garnered some interest in the 70s before subsiding. DCS became popular again in the 90s as regulators mandated chlorofluorocarbons (CFC) reduction. And now, district cooling systems gain new grounds as the world looks to reduce carbon emissions and recycle water.

Why the ST Ang Mo Kio TechnoPark?

Anatomy of a Unique Project

The AMK TechnoPark is ST’s largest wafer-production fab by volume. Bringing DCS to that particular site will thus have significant ripple effects. Traditionally, projects of this size target urban developments. For instance, the Deep Lake Water Cooling infrastructure in Toronto, Canada, has a similar capacity (40,000 tons), but the distribution network covers a chunk of the downtown area. The ST and SP Group infrastructure is thus unique because it’s one of the first at such a scale to cool an industrial manufacturing plant. It is also a first in the semiconductor industry. Most projects from competing fabs retrofit new chillers. With this new DCS, ST can re-purpose the space in favor of something much more efficient.

The project will cost an estimated USD 370 million, including the construction of the central cooling plant right next to the TechnoPark. Beyond energy savings, removing chillers within the ST plant will free up space for other environmental programs. For instance, the AMK site is looking at water conservation and solar panels, among other things. The SP Group should start construction of the central plant this year and is committed to managing the project for at least the next 20 years. Singapore also hopes that this project will inspire other companies. As Ms Low Yen Ling, Minister of State, Ministry of Culture, Community and Youth & Ministry of Trade and Industry stated, “I hope this initiative will inspire many more innovative decarbonization solutions across other industrial developments, and spur more companies to seek opportunities in sustainability.”

The post Singapore’s largest industrial district cooling system, Now operational at ST’s AMK TechnoPark appeared first on ELE Times.

Navitas consolidates Asian franchised distributor base

A makeshift motion-activated lamp

| I had an awful lot of power outages lately and decided to make a lamp based on a 12V 10W LED I had laying around. It is controlled by a dimmer with a 555 timer, modified by connecting the reset pin to a switch. This gives the devices 3 modes - off, on, or triggered by a motion sensor. I am quite proud of myself for figuring out the motion activation without using an MCU. The device is powered by any qc/pd device via a trigger or an external battery. And yes, it would be better with a 3d printed case, but I had to move and couldn't take my 3d printers with me yet, so this one is held together with hot glue and hope for a better future cardboard. [link] [comments] |